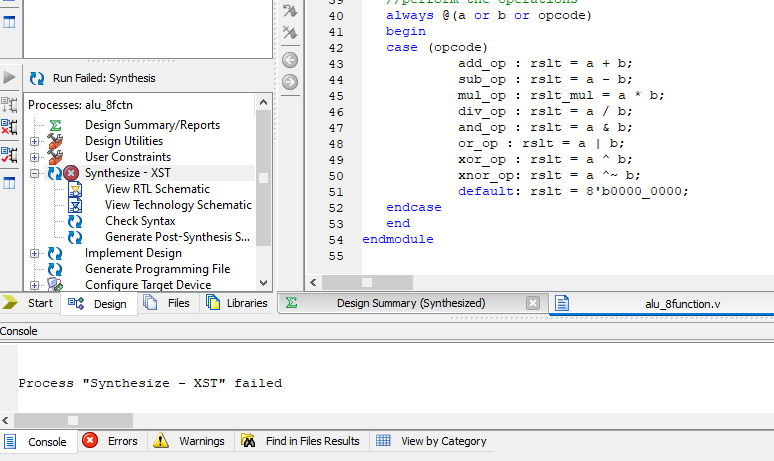

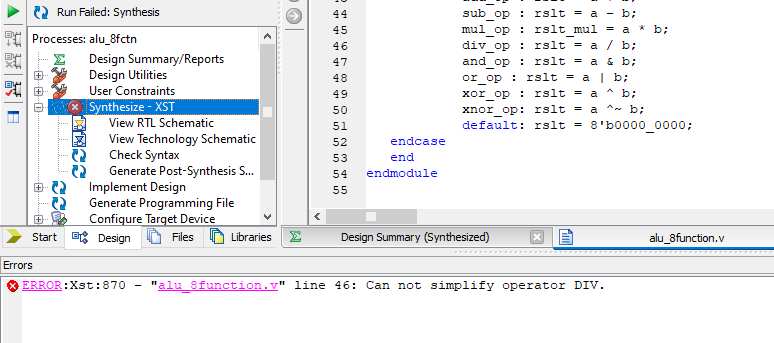

8位ALU第46行:不能简化操作符DIV

提问于 2021-03-18 10:14:31

大家好,我只想问一下如何调试这个在第46行中说的“不能简化操作符DIV”。在Verilog模块(Xilinx)。预先谢谢你的提示和帮助:)

这是我的8位ALU的代码

module alu_8fctn (a, b, opcode, rslt, rslt_mul);

input [3:0] a, b;

input [2:0] opcode;

output [3:0] rslt;

output [7:0] rslt_mul;

wire [3:0] a, b; //inputs are wire

wire [2:0] opcode;

reg [3:0] rslt; //outputs are reg

reg [7:0] rslt_mul;

//define operation codes

parameter add_op = 3'b000,

sub_op = 3'b001,

mul_op = 3'b010,

div_op = 3'b011,

and_op = 3'b100,

or_op = 3'b101,

xor_op = 3'b110,

xnor_op = 3'b111;

//perform the operations

always @(a or b or opcode)

begin

case (opcode)

add_op : rslt = a + b;

sub_op : rslt = a - b;

mul_op : rslt_mul = a * b;

div_op : rslt = a / b;

and_op : rslt = a & b;

or_op : rslt = a | b;

xor_op : rslt = a ^ b;

xnor_op: rslt = a ^~ b;

default: rslt = 8'b0000_0000;

endcase

end

endmodule回答 1

Stack Overflow用户

回答已采纳

发布于 2021-03-18 10:26:15

您的Xilinx似乎与a / b有问题。合成器很难用可变因子进行优化,特别是如果它们是零的话。

Xilinx应该有一些用于划分的预定义模块(如果不是,您可以自己创建)

wire [3:0] rslt_div;

<XilinxPrividedDividerModuleName> div ( rslt_div, a, b);

always @*

...

div_op : rslt = a / b;

...其他问题:rslt和rslt_mul是推断锁存,因为它们不是在所有条件下都被赋值。在mul_op和rslt_mul中,只在mul_op中分配rslt,这是没有分配rslt的唯一条件。

简单的解决方案是在case语句之前给rslt和rslt_mul一个初始值/默认值。

always @*

begin

rslt = 4'h0;

rslt_mul = 8'h00;

case (opcode)

// ... you other code

endcase

end还请注意,always @(a or b or opcode)是Verilog-1995编写敏感列表的方法.自Verilog-2001以来,首选的方法是always @* (或同义词always @(*))。SystemVerilog在always_comb方面更进一步,在这里,如果推断出闩锁,那么一个好的工具应该标记一个错误。

您可能还需要考虑ANSI风格的模块头(自Verilog-2001以来也可用),它比Verilog-1995模块标头样式更少冗长,更不容易打字。

module alu_8fctn (

input [3:0] a, b,

input [2:0] opcode,

output reg [3:0] rslt,

output reg [7:0] rslt_mul );

//define operation codes

parameter add_op = 3'b000,

...页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/66696817

复制