恐怖如斯的 ADI:ADC 家族 AD485x(一些有趣的细节)

恐怖如斯的 ADI:ADC 家族 AD485x(一些有趣的细节)

云深无际

发布于 2026-01-07 13:45:46

发布于 2026-01-07 13:45:46

昨天的芯片有很多的细节,可以展开聊聊。

恐怖如斯的 ADI:ADC 家族 AD485x(20bit 1Msps SAR 8 通道同步采样)

先看这个问题:对这个20bit输出有疑问,AD4858开启SHDR模式后,20bit的输出会随着softSpan的自动调整变化嘛?

在这里

在这里

SoftSpan 自动调整与增益

在 AD4858 中,SoftSpan 是一个控制输入范围的配置,自动决定 输入信号的增益。当 SHDR 启用时:输入信号的增益会自动根据每个样本的幅度进行调整;在小信号区域,增益会增大,以尽量降低噪声;而在大信号区域,增益会回落,防止信号饱和。

20-bit 输出与增益调整

SHDR 启动时,自动增益调整影响的是 模拟信号的放大,而 ADC 输出的 20-bit 数据会根据增益和输入信号的关系进行量化,但不直接反映增益的变化;输出的量化精度 依赖于信号幅度和增益设定,但 量化后的数字输出 是对输入信号的精确表示,不会随增益变化而改变位宽,20-bit 位宽保持不变。

image-20251107111858211

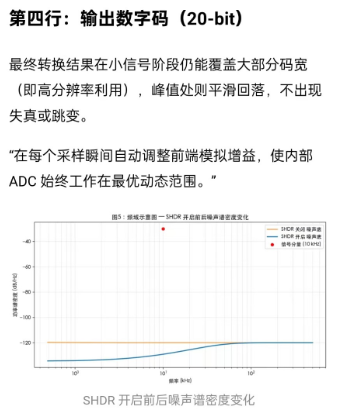

SHDR OFF(关闭状态):在关闭 SHDR 时,输入信号的噪声大约为 75 µVrms;当输入信号的幅度较小(例如接近零点)时,噪声会显著增大,导致 动态范围较窄。

SHDR ON(开启状态):当 SHDR 启用时,噪声显著降低,噪声底降低至 75 µVrms 以下,这意味着通过动态增益控制,低幅信号的噪声得到了压制,提高了系统的动态范围。

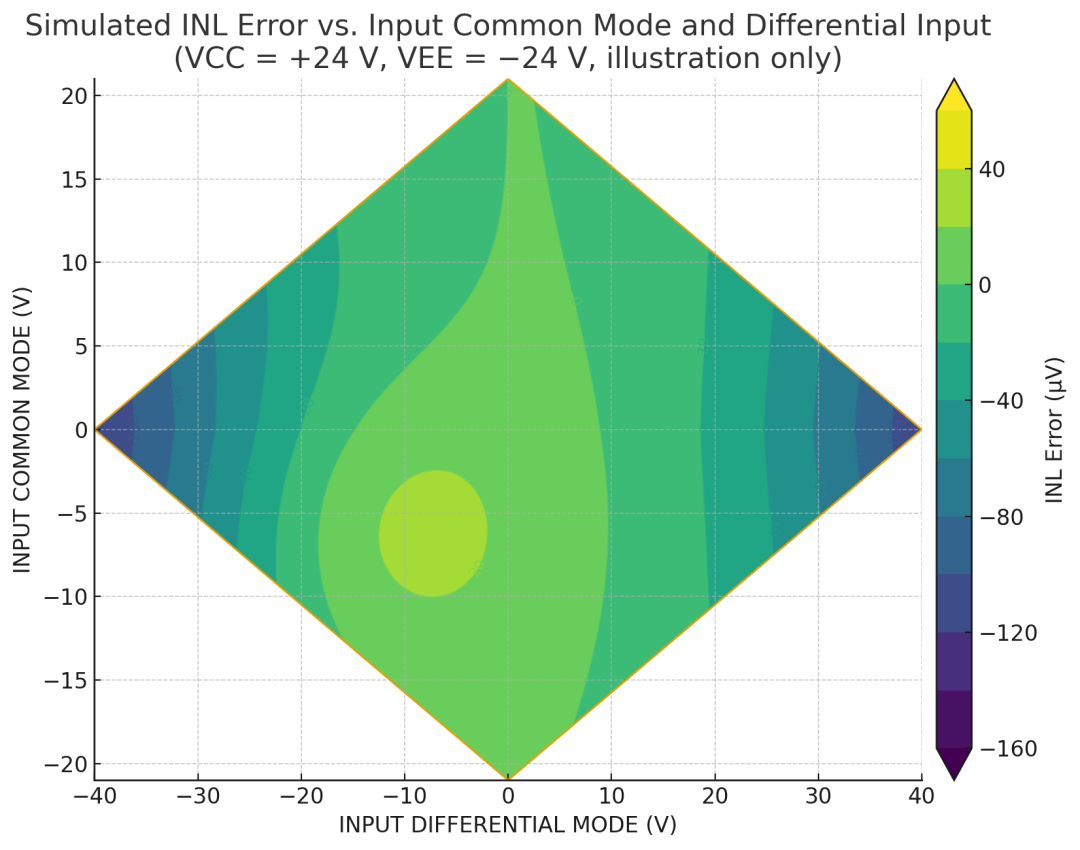

一张彩图

这是从来没有见过的彩色图:

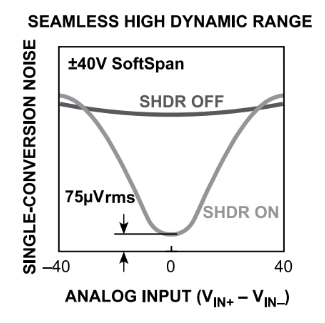

线性误差 (INL, Integral Nonlinearity)与输入共模电压 (Input Common Mode)、输入差分电压 (Input Differential Mode)

线性误差 (INL, Integral Nonlinearity)与输入共模电压 (Input Common Mode)、输入差分电压 (Input Differential Mode)

直观展示了在不同输入工作点下,ADC 的非线性误差分布情况。

横轴 (X-axis):输入差分电压 ,范围从 −40 V 到 +40 V。

纵轴 (Y-axis):输入共模电压 ,范围从 −21 V 到 +21 V。

颜色等高线 (Contour Levels in µV):代表 INL(积分非线性误差),单位是 微伏 (µV)。

供电条件: → 表示 ±24 V 双极供电下的测试条件。

图形呈“菱形区域”,这是 AD4858 输入结构的有效工作范围:

安全裕度

在该范围内 ADC 保持正常线性工作,超出边界会导致输入级共模超限或采样电荷不稳定。

中央黄色区域(INL ≈ 0 µV)

差分信号在 ±25 V 以内、共模在 ±10 V 以内时,线性误差接近 0;表明 AD4858 的线性度在绝大多数实际工作范围内非常优异(误差 < ±20 µV)。

边缘蓝色区域(负误差)

当差分电压接近 ±40 V 时(接近满量程输入),INL 误差开始上升至 −100 µV 至 −160 µV;这是采样电容与开关导通阻抗非理想效应造成的轻微压缩(Gain Compression)。

局部绿色/橙区(轻微正误差)

表示在某些共模偏置下,输入级失衡引起微小增益膨胀 (+20 µV);这种误差呈对称分布,说明内部采样路径匹配度非常高。

一定要±24 V 提供足够共模裕度:

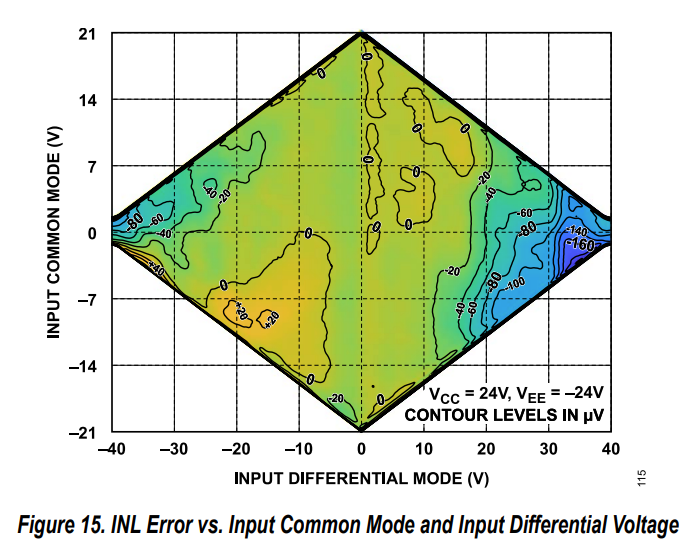

测试都是这样

测试都是这样

AD4858 的线性误差在绝大多数输入范围内都接近 0;当输入信号接近极限电平(±40 V)时会出现轻微压缩;它能在宽共模范围下保持出色的线性度,非常适合高压差分测量应用(如工业信号采集、模拟前端)。

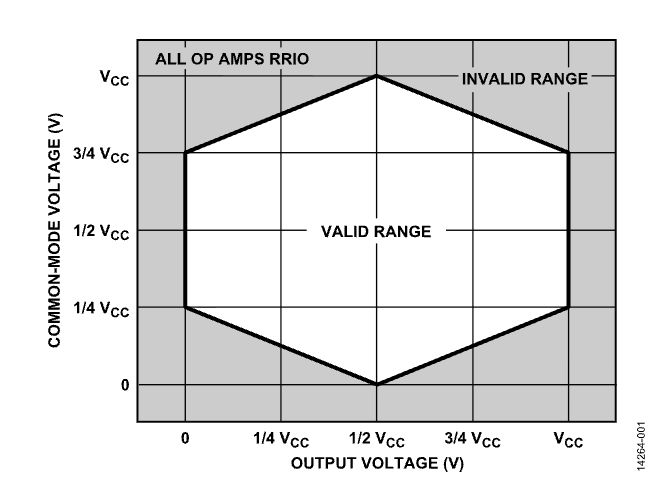

绘制一个等高线线性度误差模拟图

INL 等高线模拟图

INL 等高线模拟图

采用边界方程 ,四个顶点分别是 、,对应数据手册的工作范围。

构造“合理的”INL 误差场(仅用于说明,不是器件真实数据)

边缘负偏差: 时出现压缩,向 −80…−160 µV 发展,模拟满幅附近的轻微增益压缩;

内部小幅正口袋:在共模、差模的某个区域给出 +20…+40 µV 的小“鼓包”,对应手册里零附近偶尔出现的轻微正 INL;

中心大区块接近 0 µV,说明在多数实际工作点(|Vdiff|≲25 V、|Vcm|≲10 V)线性度极好;靠近左右边界(|Vdiff|→40 V)负偏差加:模拟满量程附近的轻微压缩(−60…−140 µV);局部正偏差口袋,提示在某些共模/差模组合下可能出现 +20…+40 µV 的小幅增益膨胀,但范围有限。

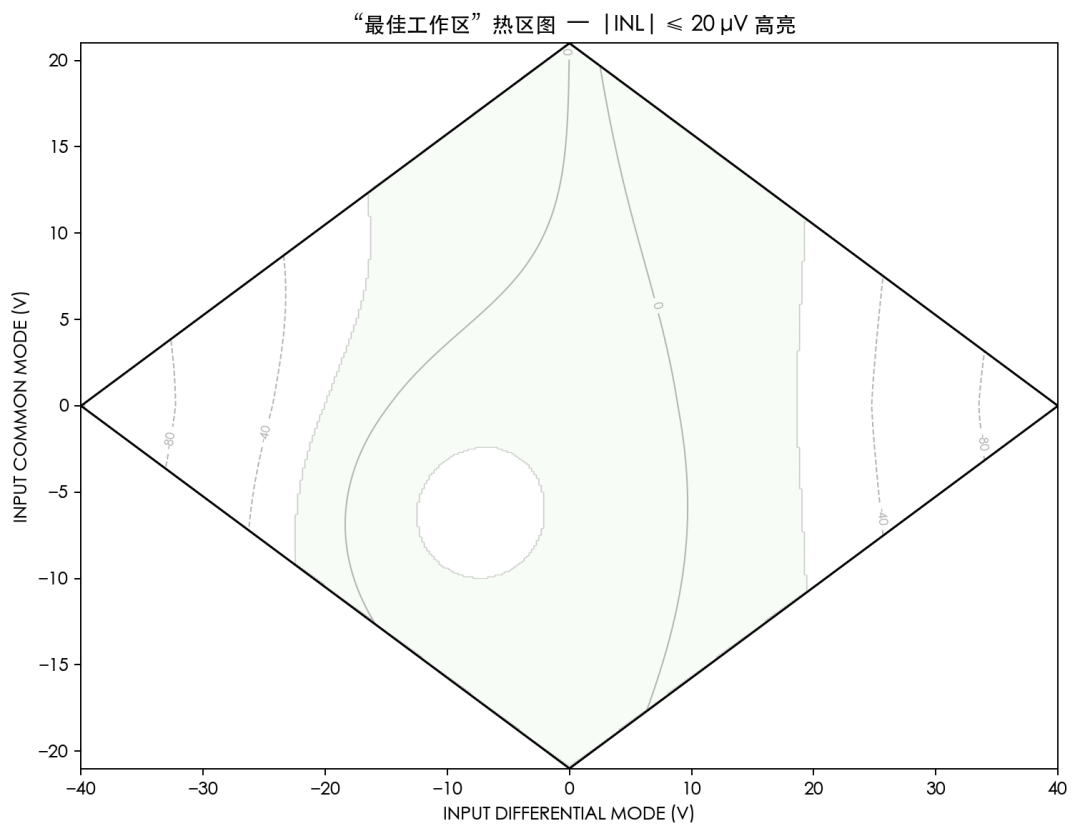

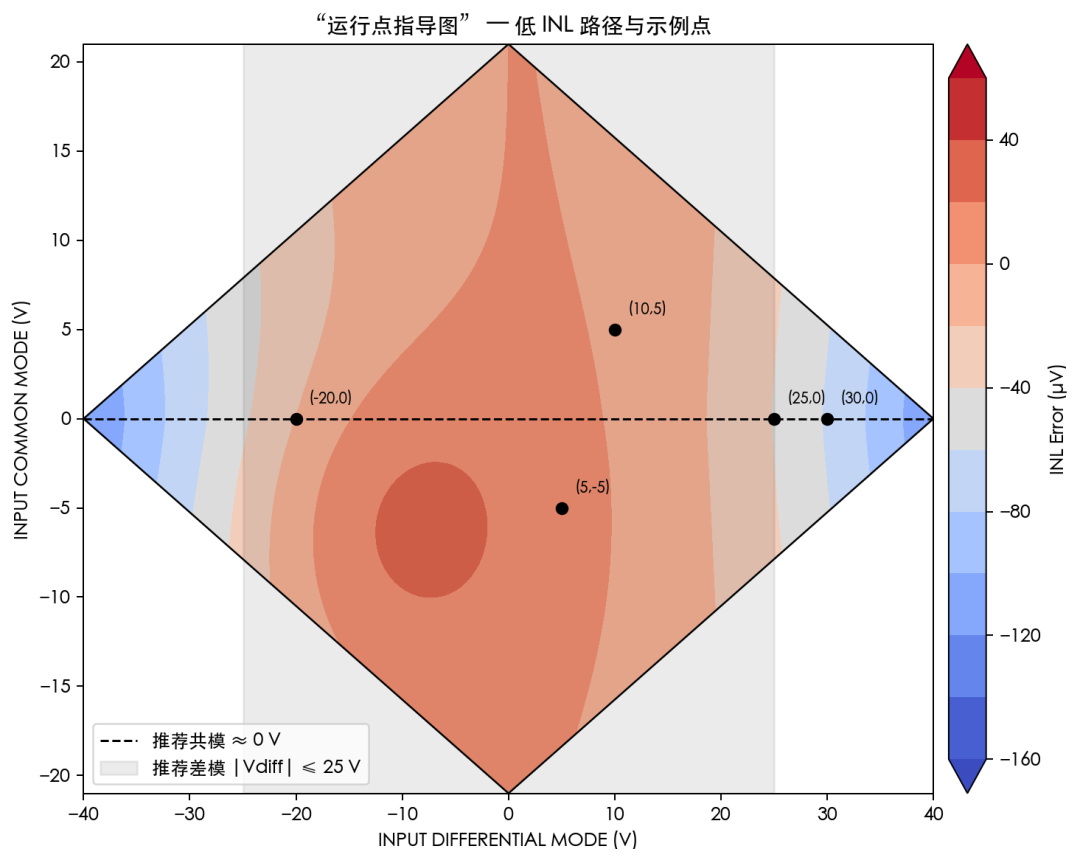

你知道这个图让我想起来了什么吗?其实是仪表放大器:

合理怀疑前级就是 INA。

绿色高亮区表示在该共模–差模组合下,等效 INL 误差的绝对值不超过 20 µV(示意模型);叠加了粗粒度的 INL 等高线(−160→+60 µV),便于看“从良好到边缘”的过渡。

结论:共模尽量接近 0 V;差模留出裕量,优先在 |Vdiff| ≤ 25 V 内工作;当需要逼近满量程(|Vdiff|→40 V)时,线性误差会加大(边界负向压缩),但是 ADI 的视频说是大共模范围,这点应该有待商榷。

背景为连续等高填色(冷暖色调:蓝=负误差,红=正误差);虚线 Vcm≈0 V 和半透明带 |Vdiff|≤25 V 给出推荐运行走廊。

标了几个示例运行点(黑点与坐标),可直接映射到前端偏置与 SoftSpan 选择;例如 (±20, 0) 几乎总在低误差带;(30, 0) 已靠近负误差加剧区,若可调量程/前端增益,建议回到 25 V 内。(不知道自动算法是不是靠着这个运行的)

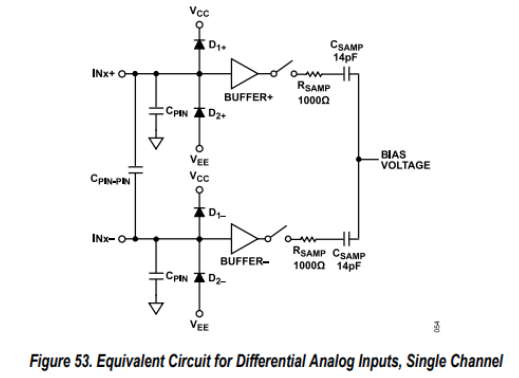

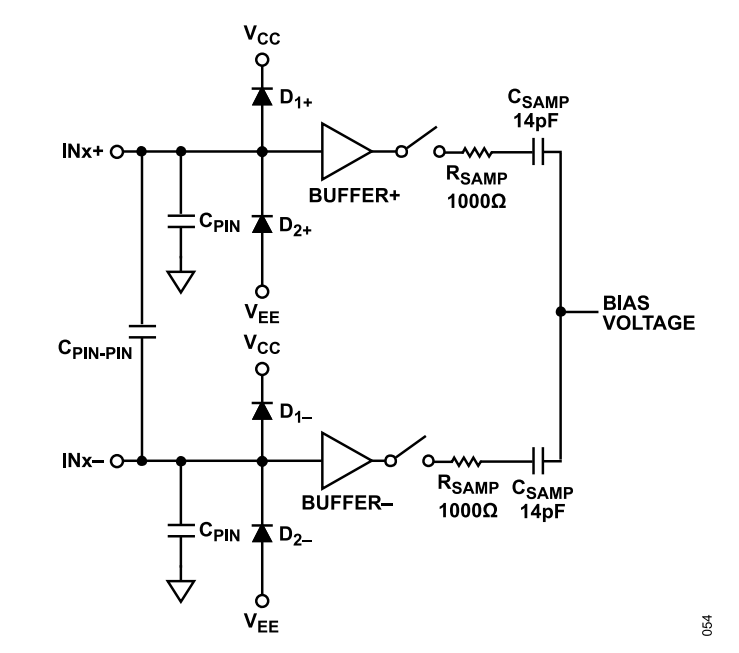

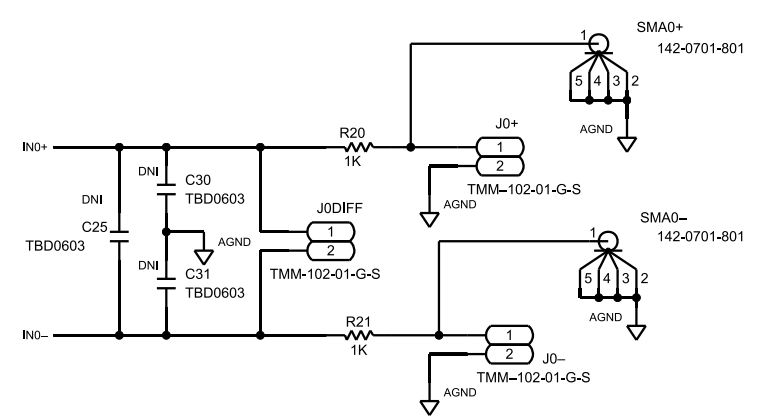

Buffered Analog Inputs+ 图 53(单通道差分等效电路)

Buffered Analog Inputs+ 图 53(单通道差分等效电路)

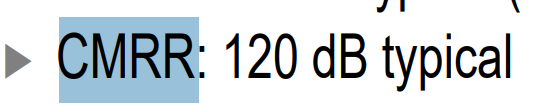

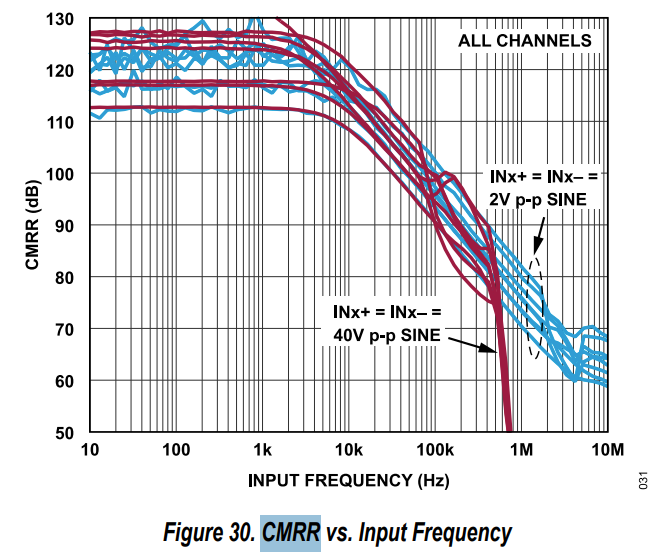

宽共模 + 高 CMRR 的差分缓冲输入

每个通道同时采样差分电压 ,且在很宽的共模范围内工作:只要 每个引脚都保持在 之间即可。

高 CMRR(共模抑制)意味着共模上的干扰/漂移被强烈抑制,真正进入量化的是纯差分分量。

image-20251107121349032

由于引脚各自只需满足“离轨 3.2 V 的安全裕度”,IN+、IN− 可以任意相对摆动:全差分、伪差分、真双极、单极性等多种驱动方式都能兼容,前端信号调理自由度很大。

其实范围上面还都挺好的

其实范围上面还都挺好的

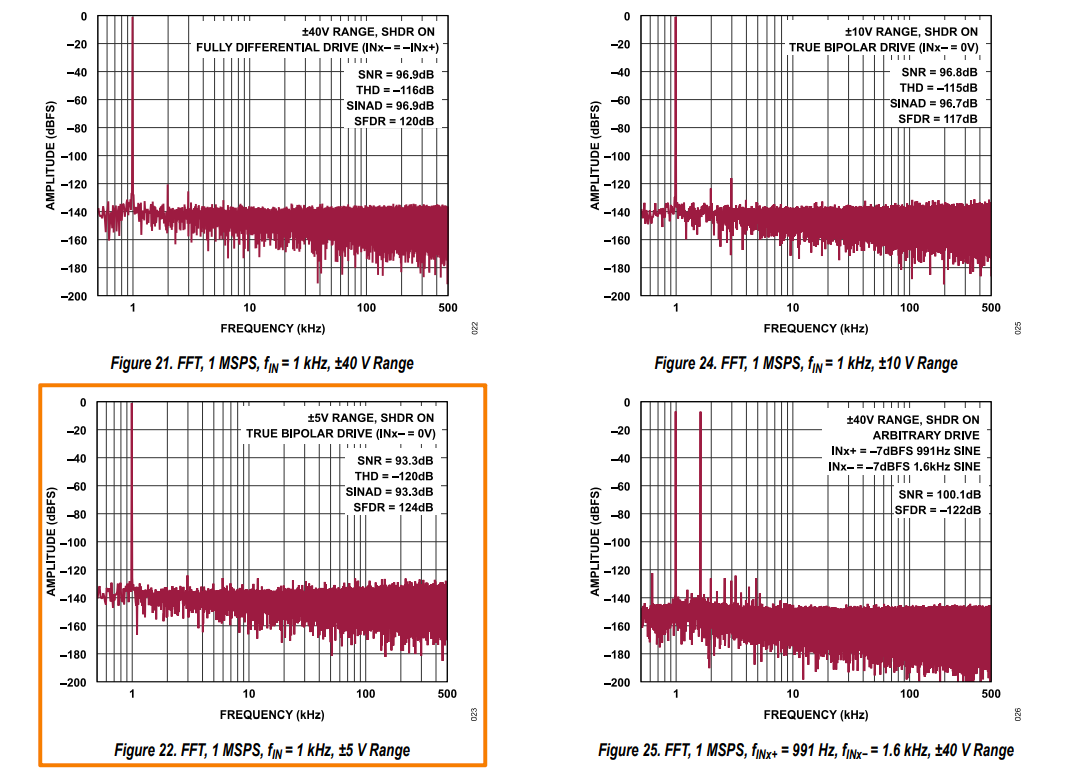

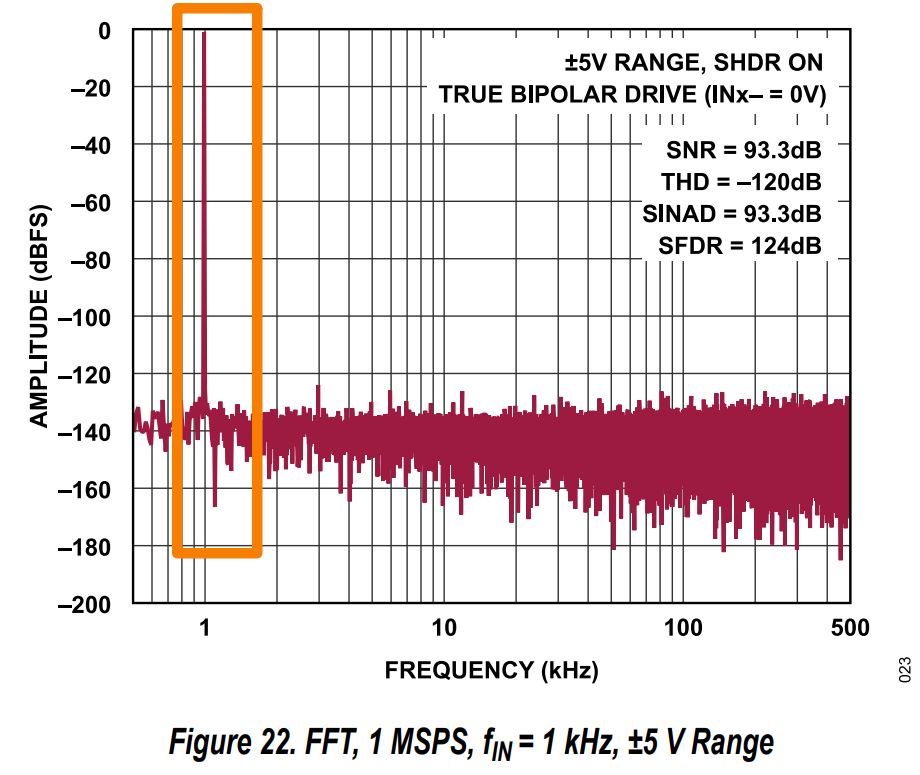

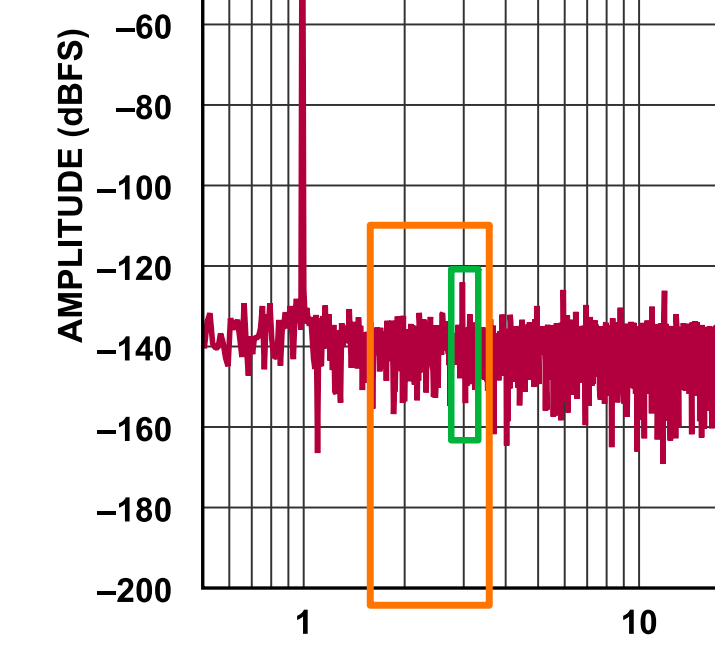

FFT(1 MSPS,fIN=1 kHz,±5 V量程,SHDR=ON,True Bipolar)

横轴:频率(对数刻度,0.5 Hz→500 kHz 的 Nyquist/2 区间);

纵轴:幅度(dBFS,满量程为 0 dBFS)。

SoftSpan 设为 ±5 V;差分“真双极性”驱动(标注 TRUE BIPOLAR DRIVE (INx−=0V) 指负端定在 0 V,正端绕 0 V 对称摆动形成差分);SHDR 打开;采样率 Fs=1 MSPS;输入为 1 kHz 正弦(接近但低于满幅的 −1 dBFS 常见做法)。

这颗 ADC 应该是 LT 团队搞的,因为这个颜色不对劲

这颗 ADC 应该是 LT 团队搞的,因为这个颜色不对劲

大红柱:1 kHz 基波;

地板约 −140 dBFS 左右的噪声底;

标注的结果:SNR=93.3 dB、THD=−120 dB、SINAD=93.3 dB、SFDR=124 dB。

参数解读

SNR = 93.3 dB

只统计“噪声”功率(排除 DC、基波与各谐波/杂散),再与基波功率比;值达到 ~93 dB,接近数据表给的 ±5 V 档 SHDR 开启时典型 SNR(~93 dB);与理想 20 bit(6.02N+1.76≈122 dB)相比低很多,原因在于实器件的前端噪声、采样开关热噪声、参考与缓冲等综合噪声,且这是单次采样、未叠加大 OSR 平均。

THD = −120 dB

总谐波失真(2f、3f、4f、5f…的功率和相对基波);

−120 dB 说明谐波极低,线性度非常好;图上在 2 kHz、3 kHz 等位置几乎看不到显著谐波柱。

SINAD = 93.3 dB

包含“噪声 + 失真”的综合指标:

这里 SINAD ≈ SNR,意味着失真项远小于噪声项——性能主要由噪声决定,而非失真决定。

对应 ENOB ≈ (SINAD−1.76)/6.02 ≈ 15.2 bit(1 MSPS、±5 V、单次采样)。

SFDR = 124 dB

基波与最大杂散(可能是某一谐波或非谐波 spur)之间的幅度差;124 dB 属于非常高的无杂散动态范围,契合 −120 dB 级 THD 的线性度表现。

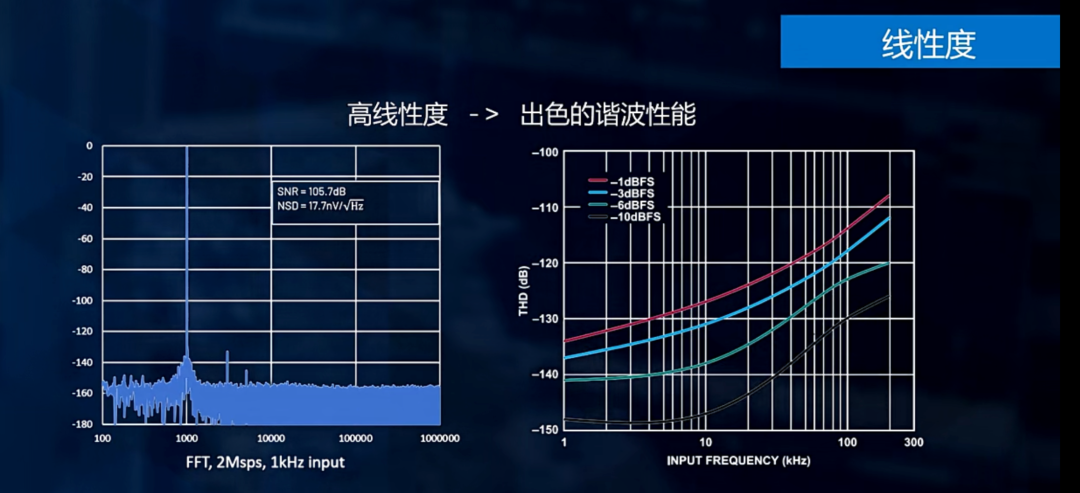

和 4630 比还是稍逊风骚的

和 4630 比还是稍逊风骚的

总结来看。

ADC的线性度强THD≈−120 dB、SFDR≈124 dB ⇒ 模拟前端与量化线性优异;看结果SINAD≈SNR ⇒ 性能瓶颈是噪声不是失真;另外SHDR 在满幅附近的作用,靠近满量程时,SHDR 会回落到与“SHDR OFF”相同的低增益;因此大信号时 SNR 与关闭时接近,小信号时才看见 SHDR 带来的显著噪声降低与 DR 提升。

量程越小,输入等效噪声越小,SNR 有所提升;SHDR 打开对小信号最有利(自动抬增益降低等效噪声);本图是 1 kHz 近满幅信号,SHDR 的收益在 FFT 上不显著(但不会更差)。所以还是尽可能的时候小量程测量,这样更加的精确。

采样序列与“采样网络”工作方式

采样序列与“采样网络”工作方式

图给出了采样瞬间的等效电路(单通道差分):

IN+ ──► BUFFER+ ──┬─[Rsamp≈10 kΩ]─┬─ Csamp≈14 pF ─┐

│ └───────────────┤→ BIAS node(两个电容的下板相连)

IN− ──► BUFFER− ──┴─[Rsamp≈10 kΩ]─┬─ Csamp≈14 pF ─┘

参考

参考

BUFFER±:片内宽带模拟缓冲,把外部引脚与内部采样电容隔离开(用户看到的是极高输入阻抗、极小漏电)。

Rsamp / Csamp:在采样相(acquisition),开关闭合,缓冲器通过 Rsamp 给 Csamp 充电;在转换相(conversion),开关断开,采样电压保持在 Csamp 上进行量化,随后复位。

BIAS VOLTAGE:两个采样电容的共用下板偏置点;配合差分结构,形成真正的差分采样。

动态要求:为了保证在 1 MSPS 下可靠建立,建议输入在采样瞬间的瞬时斜率 < 100 V/µs,避免“跟踪到保持”的切换带来额外误差(相当于减少采样孔径误差与充电未完成导致的失真/噪声)。

。在 1 MSPS(1 µs 周期)且有片内缓冲增益与带宽支撑的前提下,全幅阶跃也能在采样窗内充分建立(手册给出 <300 ns 的建立时间指标)。

引脚侧 ESD 结构与“电流注入”问题

IN± 到 VCC/VEE 各有ESD 二极管(图中 D1+/D2+、D1−/D2−),在供电合法范围内它们不导通;模拟输入的直流漏电典型仅 ~75 pA。

外部很多前置缓冲放大器(运放)也带“对电源或地的箝位二极管/保护网络”,在瞬态尖峰时容易导通,往输入路径注入反灌电流,造成瞬态误码或幅值污染,AD4858 把大寻址的宽电源窗口 + 片内缓冲结合,使 ESD 在合法输入范围内保持关断,因此极少对信号注入电流,这比把信号先送到“外置缓冲+保护二极管”的常规方案更干净、更可预期。

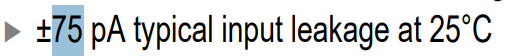

ADC 的输入阻抗

结论先说:AD4858 的模拟输入是“缓冲式超高阻”。

直流输入阻抗(每个引脚),约 1 TΩ(1000 GΩ),典型漏电 ≈ 75 pA;规格表给出输入漏电 −40…+40 nA(典/极限),典型值 0.075 nA;输入电容 ≈ 4 pF / 引脚。

样相时,片内 BUFFER± 通过 Rsamp≈10 kΩ 给 Csamp≈14 pF 充电;转换相断开保持。也就是说,外部源几乎不直接“拉”采样电容,主要由片内缓冲驱动。

输入为“真高阻”,适配各种无源/有源前端 RC 抗混叠滤波;片内缓冲的模拟带宽约11 MHz。

image-20251107122223744

动态要求

动态要求

为保证充电建立与孔径误差受控,建议采样瞬间输入斜率 < 100 V/µs。

从外部看:直流是近似开路(TΩ 级),只有几皮法电容;因此高阻传感器、分压器都能直接接,通常在引脚前加一个小 R(10–100 Ω)+C 的 RC 既可完成抗混叠与“踢回”吸收。

从芯片内部看:真正驱动采样电容的是片内缓冲(Rsamp·Csamp≈10 kΩ×14 pF≈140 ns 的一阶充电常数),这也是手册对输入斜率提出上限的原因。

ESD/过压不会在正常范围内导通,因而不会像很多外置缓冲那样在瞬态时往信号路径“注电流”。典型直流漏电 75 pA 即来源于此。

简单聊聊击穿

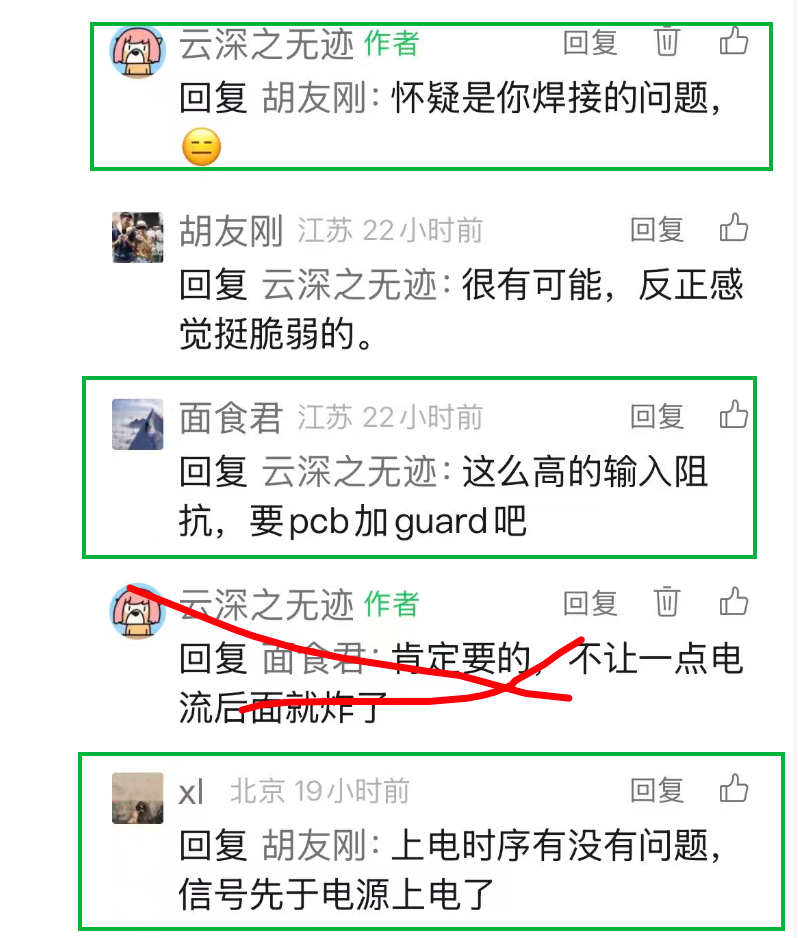

有个读者评论说这个芯片老坏

有个读者评论说这个芯片老坏

“模拟端内部二极管坏掉了(开路/短路、漏电飙升)”,基本就是EOS(Electrical Over-Stress)/闩锁搞的,应该不是“高输入阻抗不该坏”。AD4858 的输入确实是 TΩ 级、带片内缓冲,但只要瞬态让引脚越轨并灌入足够电流,ESD/箝位通道就会被过流/过热损伤。

看图说话

可能潮湿/助焊剂残留也会有漏电路径高阻节点(TΩ 级)在潮湿/脏板上变成 MΩ~GΩ,泄放电流+表面爬电,长期应力把钳位通道拖死。

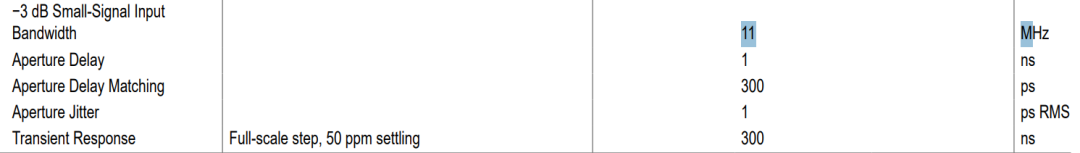

必加的串联限流电阻(近 ADC、每脚一颗)

把任何越轨时的 I_fault ≤ 10 mA。

估算:

±24 V 供电、最坏 +34 V 浪涌相对 +24 V 轨 → ;电阻220 Ω~1 kΩ / 1/8 W 常用;带宽敏感就靠近 ADC 放,前面再做 RC(见下),这在手册也是官方推荐(尤其 )。

RC 抗混叠 + 限 dV/dt

R_series 100–220 Ω + C_diff 220 pF~1 nF(差分),目标是把采样瞬间 dV/dt 压到 <100 V/µs,顺带抑制 >几百 kHz 的带外能量;如需更宽带,就把 C 做小、把 R 放到 100 Ω 级,同时保证建立时间(结合 Rsamp·Csamp)。

电源/信号时序

使能输入前,保证 VCC/VEE 已上电稳定;掉电时用 模拟开关/继电器 先断开外部源。

布线与接地

连接器→ADC 之间先走保护件,再到限流电阻,再到 ADC(就近限流);差分对等长、紧耦合;屏蔽层单端接机壳地(或两端+电容 AC-耦合),避免把大共模带进模拟地。

Guard环

在 TΩ 级节点旁边放一圈与信号同电位的铜环/面,把表面漏电引到 Guard,从而降低到地/到别的网络的漏电;它还减小输入铜箔的寄生电容;但是Guard 不能防浪涌/过压!它只是减漏电/减污染敏感的手段,对烧 ESD 二极管的那种过流毫无帮助。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-11-07,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录