不er,领导!咱们这边就是非要以太网一下子吗?(W5000)

刚刚看以前的稿子里面有什么?发现了一个以太网的东西,感觉很有趣,写一下。说起以太网现在最常见的可能就是所谓的路由器或者墙上的网线口,算了,不说了,优点是什么?

个人觉得两个场景吧,一个是高速的数据流,比如M4和M7这些MCU里面有这个IP,叫所谓的内置PHY;另外一种是连接的选择,IIC,I3C,SPI,UART这些都是所谓的Chip互联,不是远距离控制的,还有就是海量节点的时候,比如几百路,那这个东西就很合适了。更重要的是接入网络这些就可以使用现有设备。

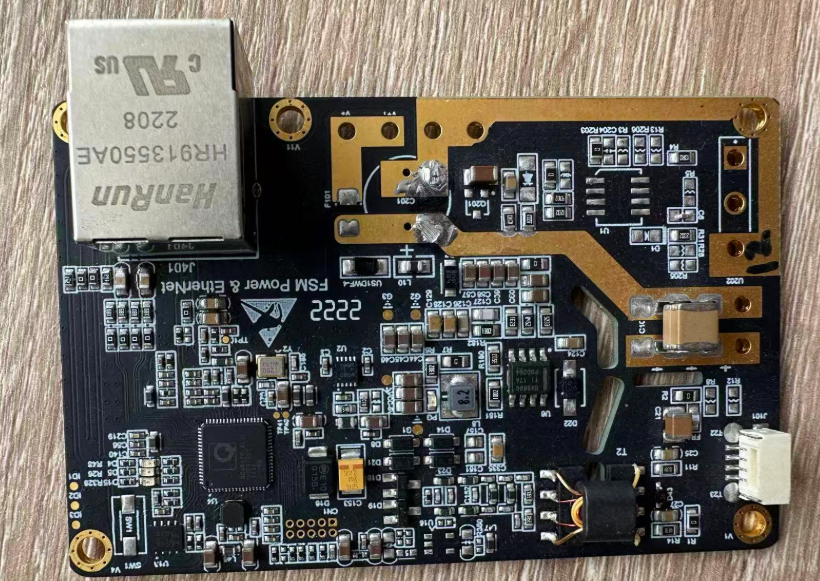

比如这个板子

比如这个板子

那普通MCU怎么拥有呢?

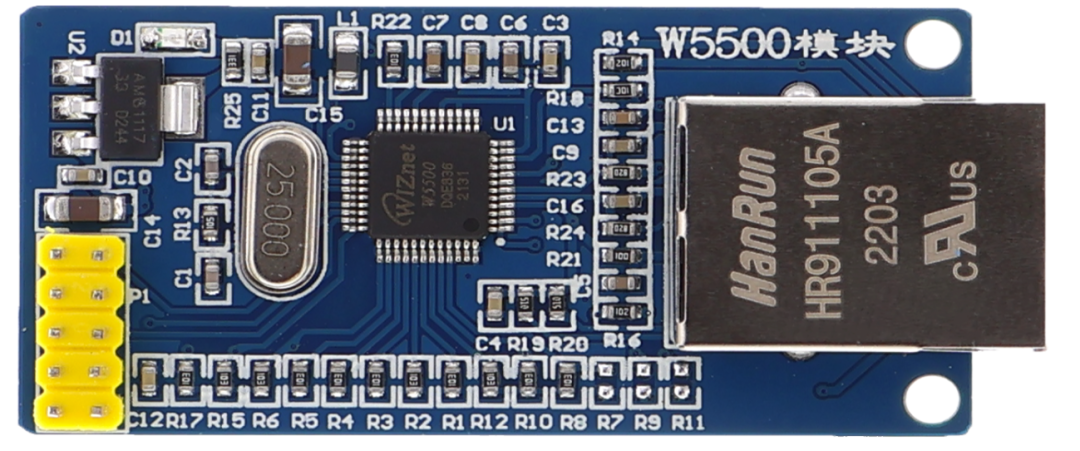

不知道多少人见过这个模块,SPI转以太网

不知道多少人见过这个模块,SPI转以太网

他们有四个芯片,基本是全场景覆盖

他们有四个芯片,基本是全场景覆盖

这里就研究最基础的W5500~

W5500 = “把 TCP/IP 协议栈做到芯片里的以太网外设”;它不是 PHY,也不只是 MAC,而是:硬件 TCP/IP 协议栈,内部集成 MAC + PHY(10/100M),MCU 只需要 SPI + Socket 编程

可以把它理解为:

一个“通过 SPI 控制的 8 路硬件网卡 + TCP/IP Offload Engine”

为什么 W5500 在嵌入式里这么常用?

MCU 负担极小

不需要 lwIP / uIP,更不需要处理 TCP 状态机,也不需要 ARP / ICMP / 重传 / 超时逻辑.

这个是MCU世界里面使用最多的库

这个是MCU世界里面使用最多的库

MCU 只做三件事,配 IP / MAC,配 Socket,最后往 TX buffer 塞数据、从 RX buffer 读数据。

是真正的“硬件 Socket”:芯片内部最多 8 个 Socket;每个 Socket 独立的有TCP / UDP / MACRAW,端口,缓存和中断;这是它和 ESP32 / lwIP 软件 Socket 的本质差异。

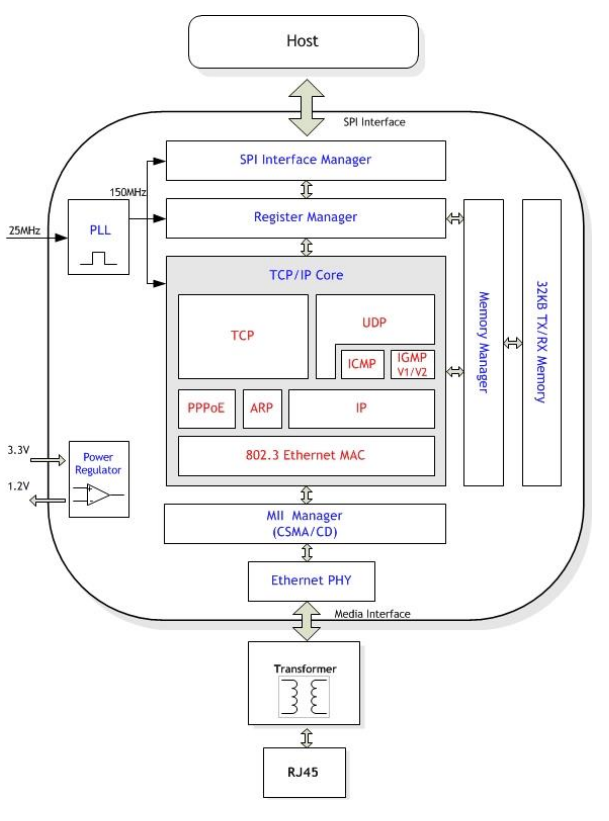

内部模块可以拆成 6 层:

唯一比较清晰的框图

唯一比较清晰的框图

MCU

│

│ SPI

▼

SPI Interface Manager

│

Register Manager

│

TCP/IP Core

├─ TCP

├─ UDP

├─ ICMP

├─ ARP

│

Ethernet MAC

│

Ethernet PHY

│

变压器 + RJ45

可以看到TCP/IP Core 完全硬件实现,MCU 永远“看不到”以太网帧,只操作寄存器 + 内存。

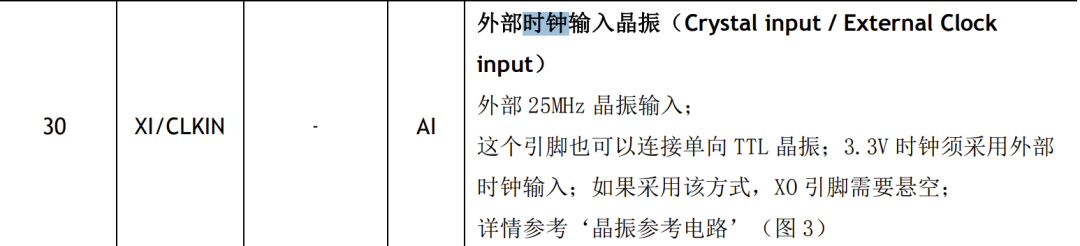

时钟(25 MHz)

支持两种方式:外部 25 MHz 晶振(推荐)以及外部时钟输入(XI/CLKIN);SPI 80 MHz ≠ 时钟 80 MHz,内部 PHY 仍然基于 25 MHz

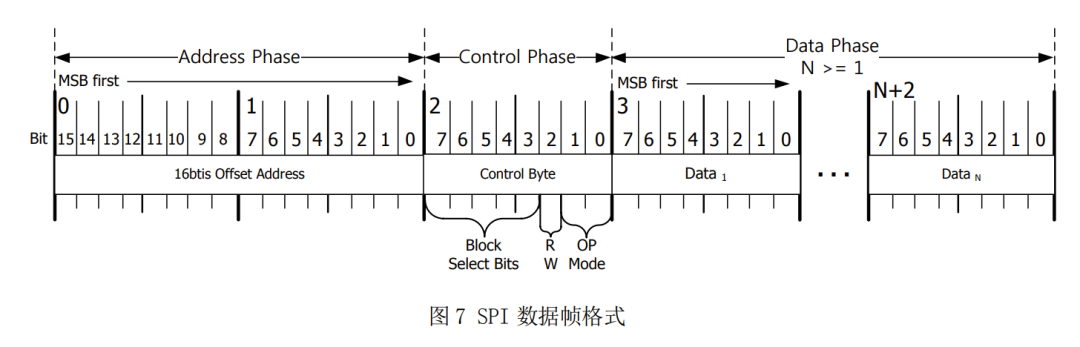

SPI 数据帧

每一帧 SPI 访问 = 3 段

| 地址段 (16bit) | 控制段 (8bit) | 数据段 (N byte) |

控制段 8bit 含义:

[ BSB4 BSB3 BSB2 BSB1 BSB0 | RWB | OM1 OM0 ]

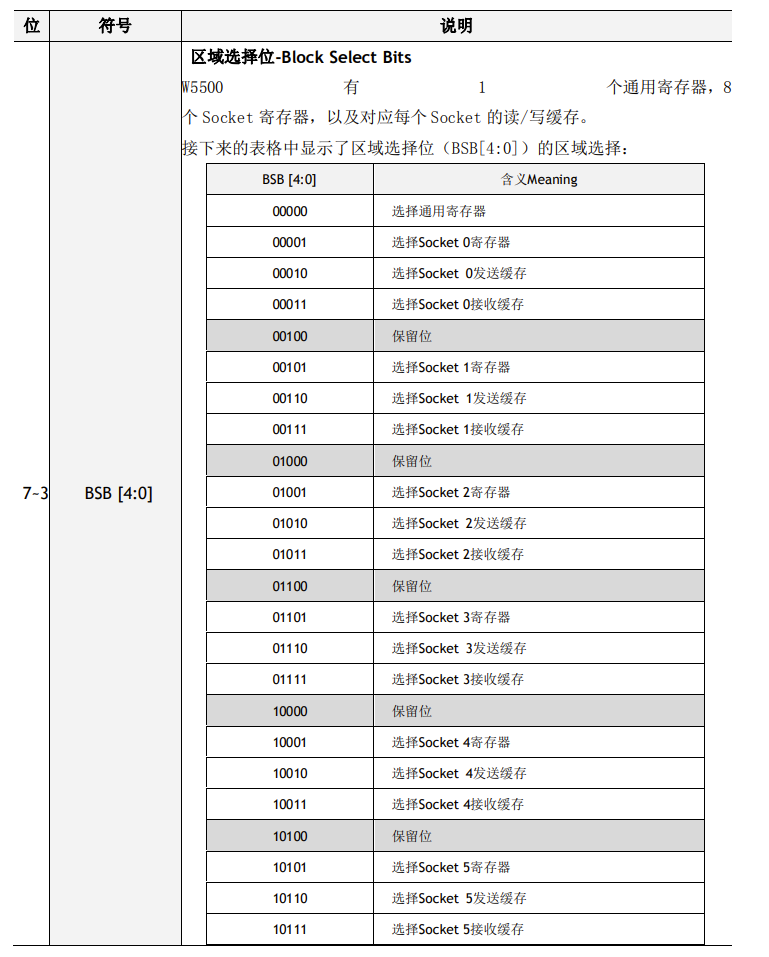

BSB:选哪个区域

RWB:读 / 写

OM:SPI 模式(VDM / FDM)

这个图很漂亮了

这个图很漂亮了

2的5次方,就是这么多的可能

2的5次方,就是这么多的可能

寄存器 & 内存模型

三大类区域

区域 | 作用 |

|---|---|

Common Register | IP、MAC、全局中断 |

Socket n Register | Socket 控制 |

Socket n TX/RX Buffer | 实际数据 |

收发数据的“指针模型”

发送流程(TX)

读 Sn_TX_WR,向 TX buffer 写数据,更新 Sn_TX_WR,Sn_CR = SEND,等 Sn_IR(SEND_OK)

接收流程(RX)

看 Sn_RX_RSR,读 Sn_RX_RD,从 RX buffer 读数据,更新 Sn_RX_RD,Sn_CR = RECV,看上去这是一个典型的 DMA Ring Buffer 思想。

算算W5500 的数据吞吐量到底有多大?

W5500 的吞吐量 不是一个数,而是被三层同时限制:

层级 | 上限 | 说明 |

|---|---|---|

以太网物理层 | 100 Mbps | PHY/MAC 极限 |

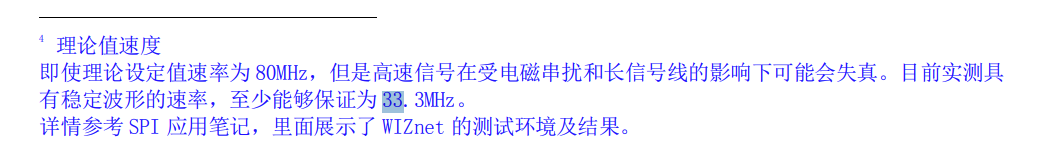

SPI 接口 | 理论 80 MHz | 稳定 ≈ 33 MHz |

MCU 处理能力 | MCU 决定 | SPI + 中断/轮询 |

真正瓶颈几乎总是在 SPI + MCU

先算 SPI等效数据带宽

以最常见配置估算(这是工程上最重要的):

SPI 时钟是33 MHz(手册明确给出实测稳定值),每 bit 1 个 SPI 时钟,每字节 8 bit,而且SPI 有协议开销(地址 + 控制)

理想裸算(不含开销):

33 MHz / 8 ≈ 4.1 MB/s ≈ 33 Mbps

加上 W5500 SPI 帧开销(地址 + 控制段):

实际有效吞吐 ≈ 2 ~ 3 MB/s;即 16 ~ 24 Mbps

这是一个非常现实、可靠的长期可用吞吐量区间

TCP vs UDP

模式 | 实际吞吐 |

|---|---|

UDP | 2.5 ~ 3 MB/s |

TCP | 1.5 ~ 2.5 MB/s |

TCP 有 ACK / 重传 / 状态机,而W5500 虽然是硬件 TCP,但 SPI 交互次数更多

和串口(UART)比,吞吐量差多少?

日常的UART 的现实极限大概是:

波特率 | 实际数据速率 |

|---|---|

115200 | ~11 KB/s |

921600 | ~90 KB/s |

3 Mbps | ~300 KB/s |

5 Mbps | ~500 KB/s |

UART 每字节 ≈ 10 bit(起始/停止位),在超过 3 Mbps 后 稳定性急剧下降,而且长线 / 多设备基本不可控

吞吐量对比(数量级差异)

接口 | 实际可用吞吐 |

|---|---|

UART(高速) | 0.1 ~ 0.5 MB/s |

W5500(SPI) | 2 ~ 3 MB/s |

差距这样算大概在5~20 倍,而且这还只是“纸面速度”层面。

W5500 相比串口的“优势”(不是只有快)

架构层级不同(这是根本),串口是字节流无边界无确认无重传无网络拓扑,要自己解决:帧同步,丢包,校验。重发,多机通信; W5500(以太网)天然的就是包这个概念,有边界有校验(CRC)有 ACK / 重传(TCP)更有有 IP / 端口;这是“通信系统” vs “信号线”的差别。 W5500可以使用Python / C / MATLAB / 浏览器,以及Wireshark 抓包调试体验极好;在实验室、量产、远程维护中,这是“质变级”的差别。

一般在数据量很小,要求低功耗,调试阶段使用串口;而在数据采集 / 仪器,实时波形 / 批量数据,需要网络化,多设备,长时间运行以及工控 / 医疗 / 测试设备要用以太网。

后记

UART 是“通信手段”,而W5500 是“通信系统”。

https://www.w5500.com/w5500/media/upload/datasheet/W5500_%E6%95%B0%E6%8D%AE%E6%89%8B%E5%86%8CV1.3.pdf

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-02-01,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录