IMEC & 上海交大/华科:基于微转印技术实现晶圆级硅光异质集成高性能TFLT调制器

IMEC & 上海交大/华科:基于微转印技术实现晶圆级硅光异质集成高性能TFLT调制器

光芯

发布于 2026-01-26 17:02:31

发布于 2026-01-26 17:02:31

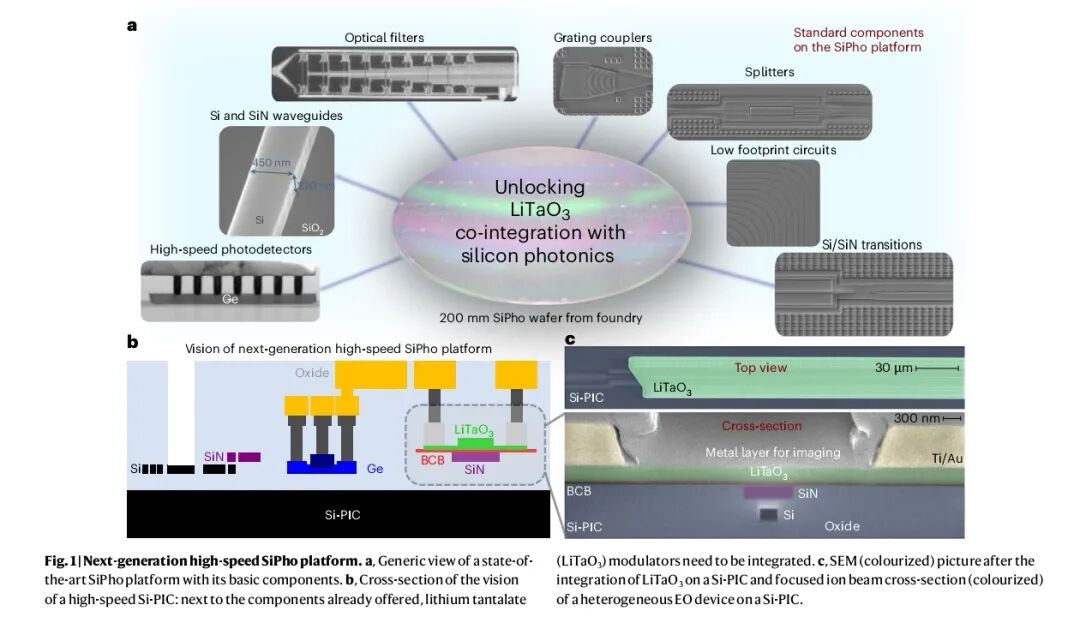

在下一代光通信、太赫兹无线传输及高精度雷达传感对器件性能提出的严苛要求下,薄膜钽酸锂(LiTaO₃,LT)凭借与铌酸锂(LiNbO₃)相当的电光系数、更优的光稳定性(弱光折变效应、高损伤阈值)及更低的双折射特性,成为突破传统硅光子与铌酸锂平台瓶颈的核心材料。近期,imec与上海交通大学/华科分别基于硅(Si)和氮化硅(Si₃N₄)光子平台,通过微转印(μTP/MTP)异质集成技术,分别构建了O波段(70 GHz带宽,2.9 dB插损,2.3 V·cm)和C波段(110 GHz带宽,1 dB插损,4.08 V·cm)的高性能调制器系统,其技术方案在兼容性、带宽、损耗及多场景拓展方面实现了关键突破,为光电集成领域的规模化应用奠定了基础。

链接:

① https://www.nature.com/articles/s41566-025-01832-9

②https://www.researchsquare.com/article/rs-8004021/v1

◆ 技术背景与核心诉求

传统硅光子调制器受限于材料本身电光效应较弱的特性,难以满足1600ZR+等新兴标准对200 GBd以上波特率的需求;而薄膜铌酸锂平台虽具备优异的电光响应,却面临偏置漂移、光损伤及CMOS工艺兼容性差(锂污染问题)的挑战。薄膜钽酸锂TFLT的出现恰好弥补了两者短板,其不仅拥有与铌酸锂可比的电光转换效率,还在直流偏置稳定性、抗光折变能力及工艺兼容性上显著提升。imec与上海交大的研究核心均聚焦于:在不重构现有光子平台工艺设计套件(PDK)的前提下,通过异质集成技术将薄膜钽酸锂与成熟的Si/Si₃N₄平台结合,既保留衬底材料的低损耗、高集成度优势,又最大化发挥钽酸锂的超宽带电光调制潜力,同时解决规模化生产中的兼容性与良率问题。

◆ imec:硅基光子平台的后端集成优化方案

imec的研究重点是实现薄膜钽酸锂与标准Si/SiN PIC的后端异质集成,确保与现有平台核心组件的无缝兼容,为硅光子系统的性能升级提供低成本解决方案。

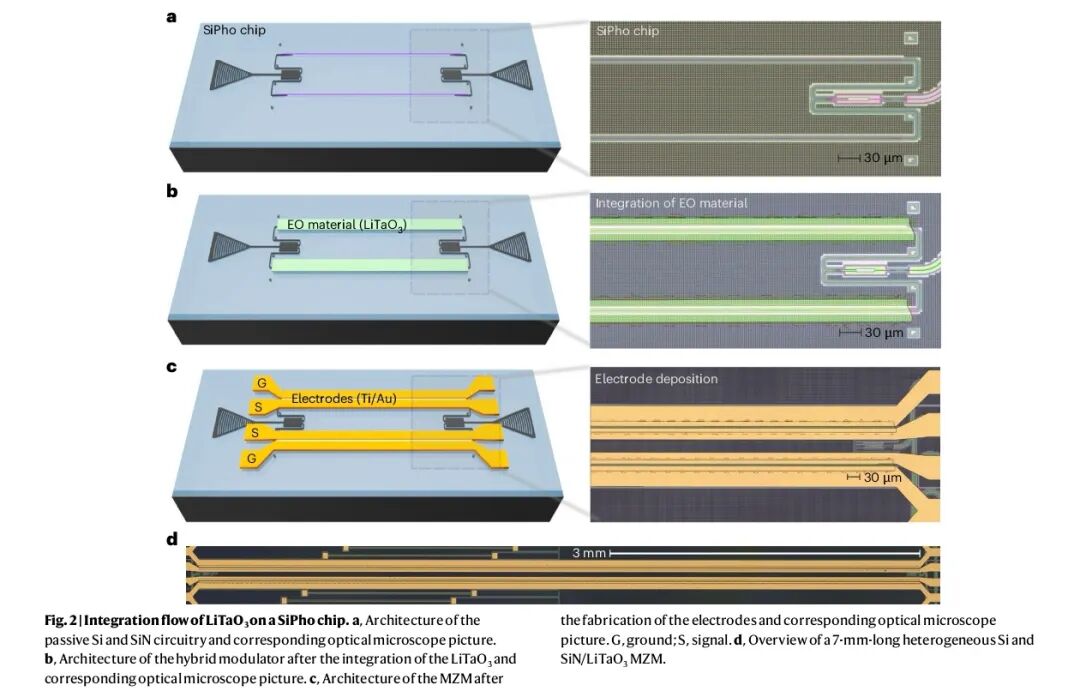

① 器件结构与设计细节

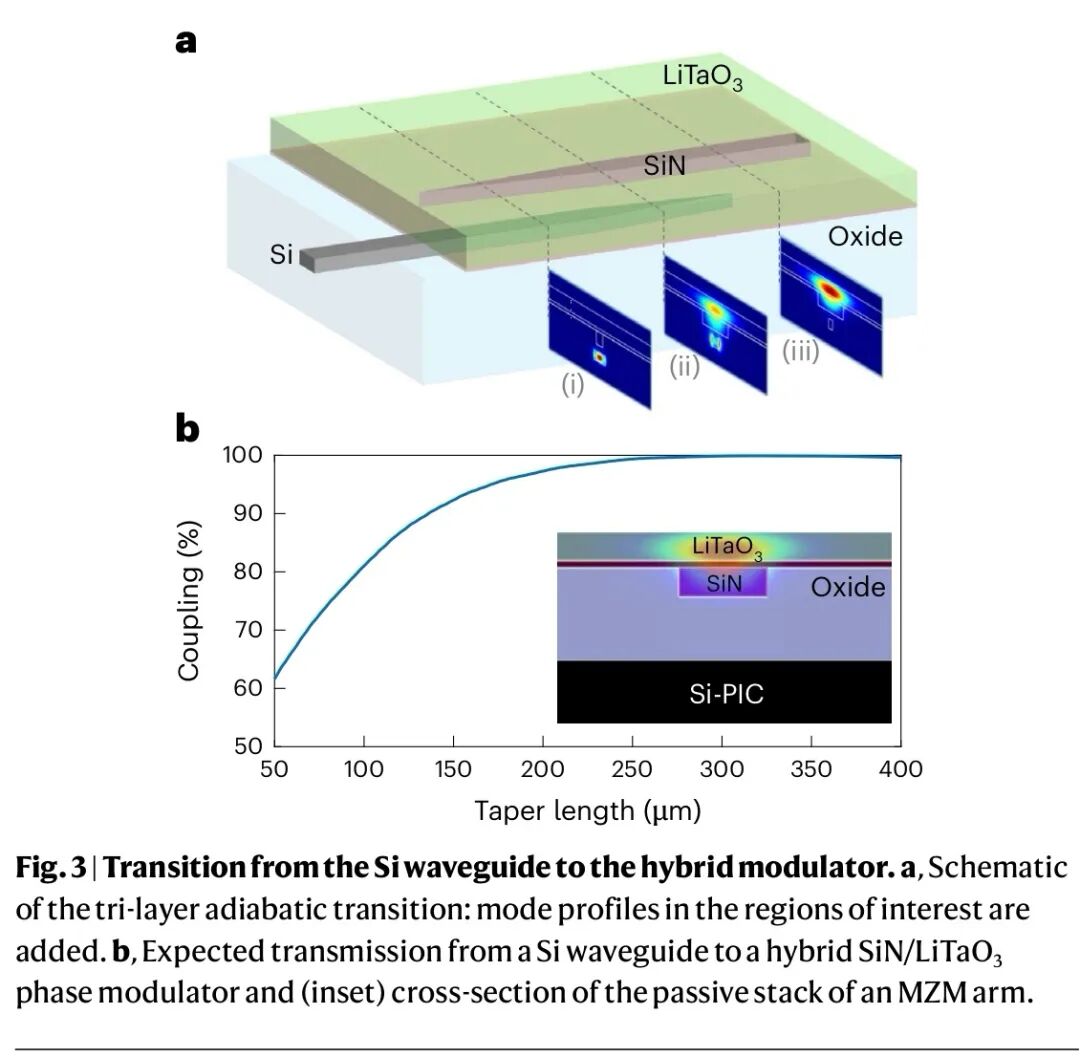

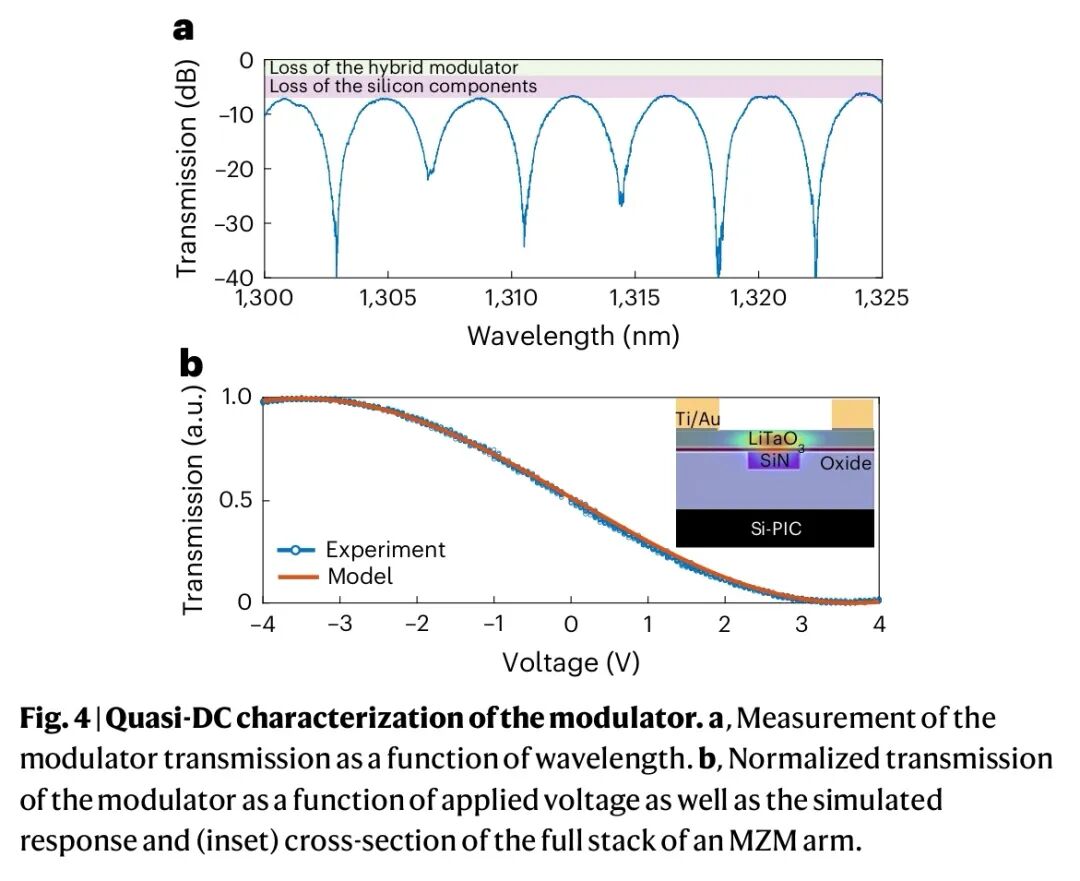

imec采用非等臂MZM作为核心结构,调制器总长度为7mm,其混合相位调制器由300nm厚的TFLT与300nm厚的SiN层构成,集成于硅基平台的Mach-Zehnder干涉仪臂中。为优化射频性能与抗干扰能力,器件采用GSSG差分驱动电极配置,这种设计可有效消除偶数阶谐波,提升调制线性度,同时增强对电磁干扰(EMI)和电源噪声的耐受性,这在多通道设备中尤为关键。

光耦合环节通过三层绝热过渡结构实现硅波导与混合调制器的高效衔接,设计的绝热耦合器不仅实现了超过99%的耦合效率,且在横向错位0.5μm范围内仍能保持稳定耦合,完全适配晶圆级微转印的对准精度要求。在1310nm波长下,器件的消光比达到28dB,展现出优异的调制对比度。

② 核心工艺实现

imec采用后端集成流程完成薄膜钽酸锂与Si-PIC的异质集成,具体步骤包括:先制备包含硅波导、多模干涉仪(MMI)、光栅耦合器等组件的无源Si/Si₃N₄器件;通过微转印技术将LT薄膜精准转移至预设区域,形成混合相位调制器;最后沉积金属电极(热电极与行波电极)并完成封装。

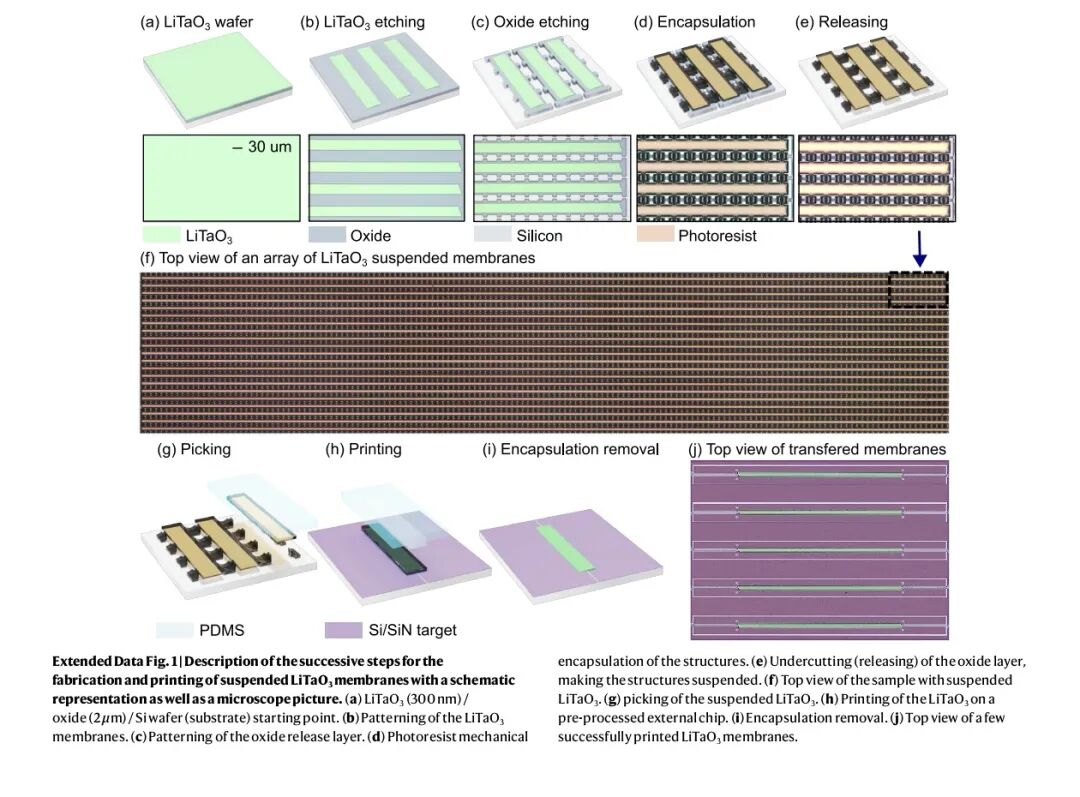

悬浮钽酸锂薄膜的制备以硅衬底晶圆为衬底,第一步采用紫外光刻技术,以适配氩基反应离子刻蚀(RIE)的非晶硅(aSi)作为硬掩模,将钽酸锂层图形化为30 μm×7 mm的矩形结构;随后采用氢氧化钾溶液去除非晶硅硬掩模。第二步通过紫外光刻与反应离子刻蚀对氧化物层进行图形化加工,将氧化物刻蚀至硅衬底表面。

接着添加光刻胶机械封装层:经紫外光刻曝光与显影处理后,光刻胶封装图案会形成硅衬底与钽酸锂薄膜间的机械连接结构,为后续器件释放时钽酸锂薄膜的悬浮状态提供支撑。最终采用缓冲氢氟酸湿法刻蚀剂释放钽酸锂薄膜。最终样品在2 mm×7 mm的样品区域内集成了21个30 μm×7 mm的薄膜,薄膜密度达1.5个/mm²;按此密度推算,4英寸晶圆上可制备的薄膜总数超12000个。

此时,悬浮钽酸锂薄膜已满足异质集成条件,目标衬底的制备遵循硅光子平台的成熟工艺规范:本研究采用imec iSiPP200平台的Si/SiN器件层,以220 nm器件层的SOI晶圆为起始基底,对硅层实施双深度刻蚀(70nm与220nm);随后对晶圆进行平坦化处理,沉积300 nm厚的氮化硅层,对该氮化硅层进行刻蚀后包覆氧化物,最终再次对晶圆进行平坦化处理。 薄膜的异质集成通过商用微转印设备完成:借助聚合物PDMS印章拾取预制的悬浮钽酸锂薄膜;为提升界面粘附性能,印刷前先在目标衬底表面涂覆BCB缓冲层;将薄膜精准放置于目标衬底的预设位置后取下印章,使薄膜固定于最终集成区域;随后采用反应离子刻蚀氧等离子体去除光刻胶封装层,并在280℃环境下对BCB层进行90分钟固化处理。

③ 性能测试与验证数据

器件性能测试结果显示,在推挽幅度调制配置下,半波电压(Vπ)低至3.5V,对应的电压-长度乘积(VπL)为2.3V·cm,与单片钽酸锂平台的最新水平相当。调制器的额外插入损耗为2.9dB,其中1.6dB源于制造过程中的错位导致的金属吸收损耗。

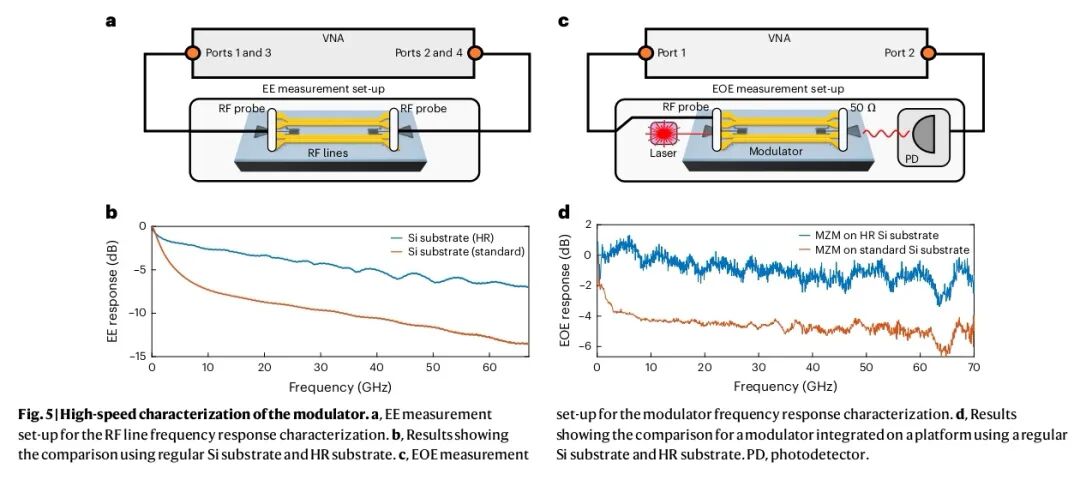

电光带宽实测超过70GHz,受限于矢量网络分析仪与光电探测器的测量上限,理论估计可达90GHz。该测量在两种不同芯片上进行:第一种芯片的调制器制备在常规硅衬底晶圆上,第二种采用高电阻率(HR)硅衬底作为晶圆衬底。两种传输线的对比结果如图5b所示,表明采用高电阻率硅衬底时,由于射频波在衬底中的吸收损耗更低,射频带宽显著提升——高电阻率硅衬底的自由载流子极少,损耗角正切低,硅衬底的射频损耗可忽略不计,此时射频传输线的损耗主要由金属线损耗主导。通过降低这些衬底损耗,可避免衬底射频损耗随频率快速增加,从而提升带宽。

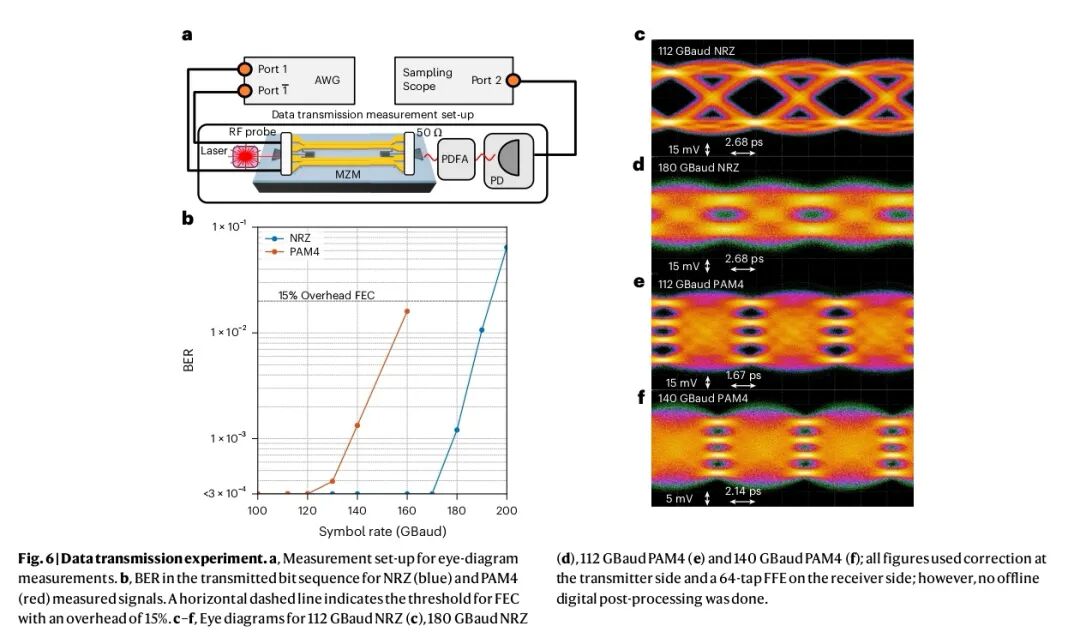

高速数据传输实验中,该调制器成功实现190 GBaud的NRZ符号速率,以及超过320 Gbit/s的PAM4传输,接收端经64抽头前馈均衡(FFE)算法优化后,误码率可降至15%开销前向纠错(FEC)的阈值以下,眼图波形清晰稳定,完全满足数据中心间及数据中心内的大规模高速互连需求。

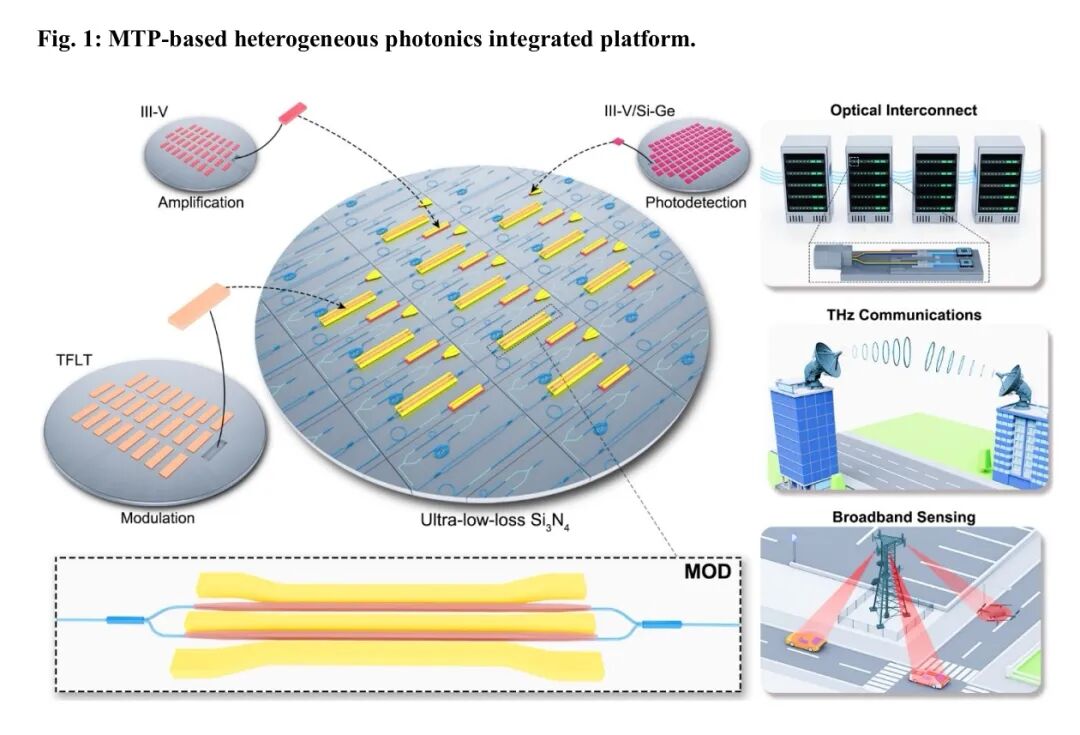

◆ 上海交大/华科:氮化硅平台的晶圆级多场景突破

上海交大的研究方向聚焦于薄膜钽酸锂与纯氮化硅(Si₃N₄)平台的晶圆级异质集成,利用lpcvd氮化硅超低传输损耗的特性,构建覆盖光通信、太赫兹无线通信及雷达传感的多场景适配调制器,在带宽、稳定性及跨频段应用上实现全面升级。

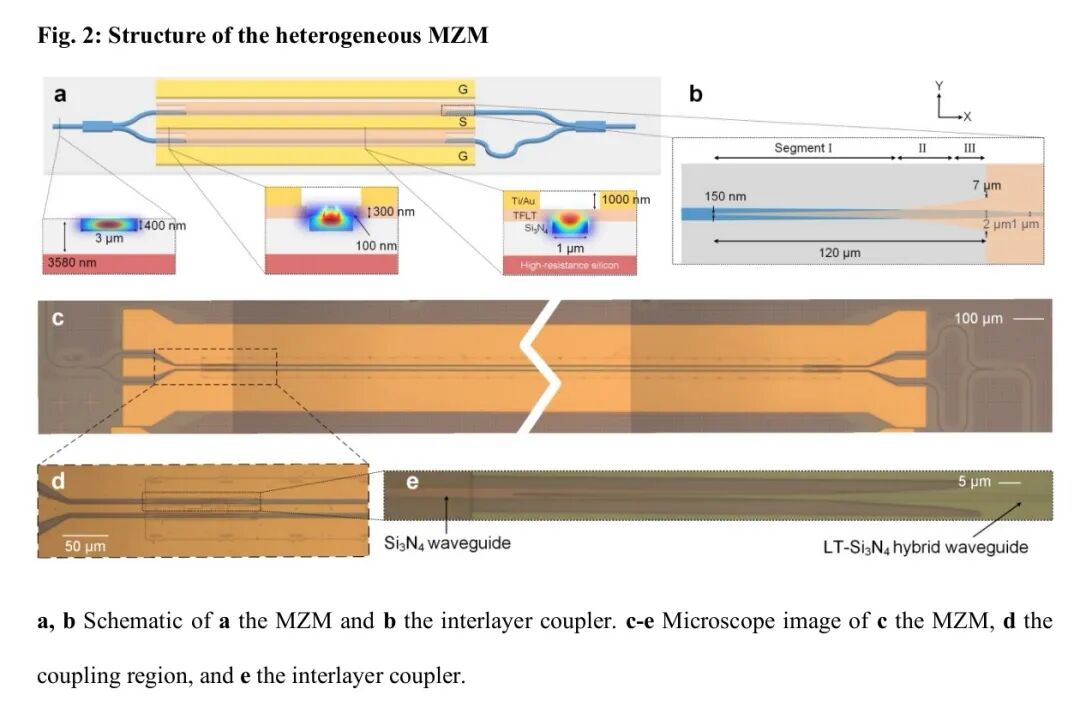

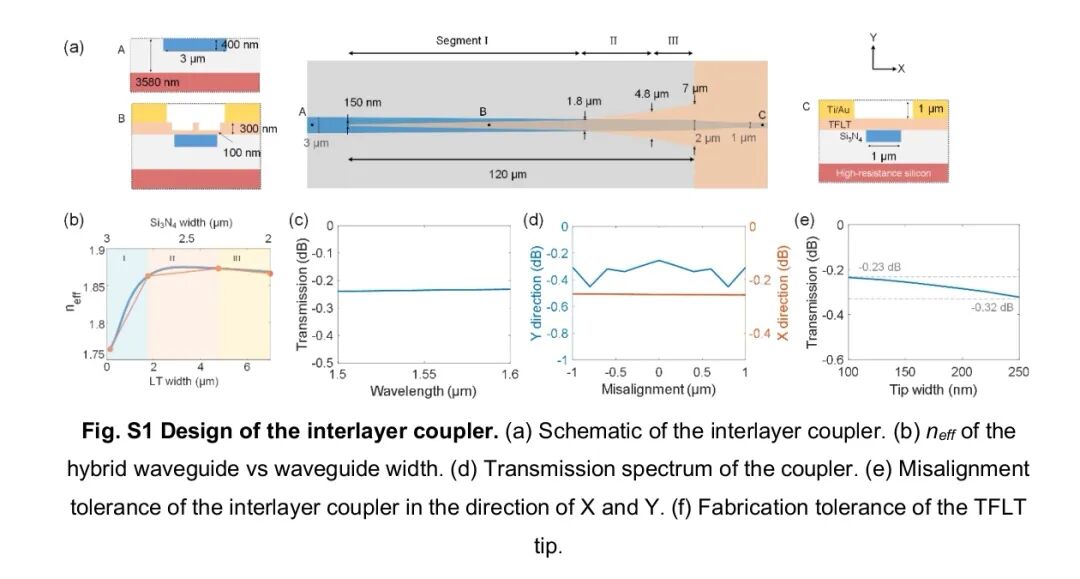

① 器件结构与设计优化

核心器件同样基于Mach-Zehnder干涉仪(MZM),层间耦合器设计是关键优化点,其耦合损耗低至0.23dB/面,且具备±1μm的宽松对准容差,大幅降低了集成工艺中的对准难度。在Y方向±1微米对准偏差范围内,插入损耗为0.23-0.45 dB,且在X方向不受对准偏差影响;当薄膜钽酸锂尖端宽度在100-250nm范围内变化时,损耗仅增加0.1 dB。行波电极采用特征阻抗匹配设计,通过优化电极尺寸与间距,实现约52Ω的特征阻抗,与50Ω标准系统良好匹配,减少了射频信号的反射损耗。

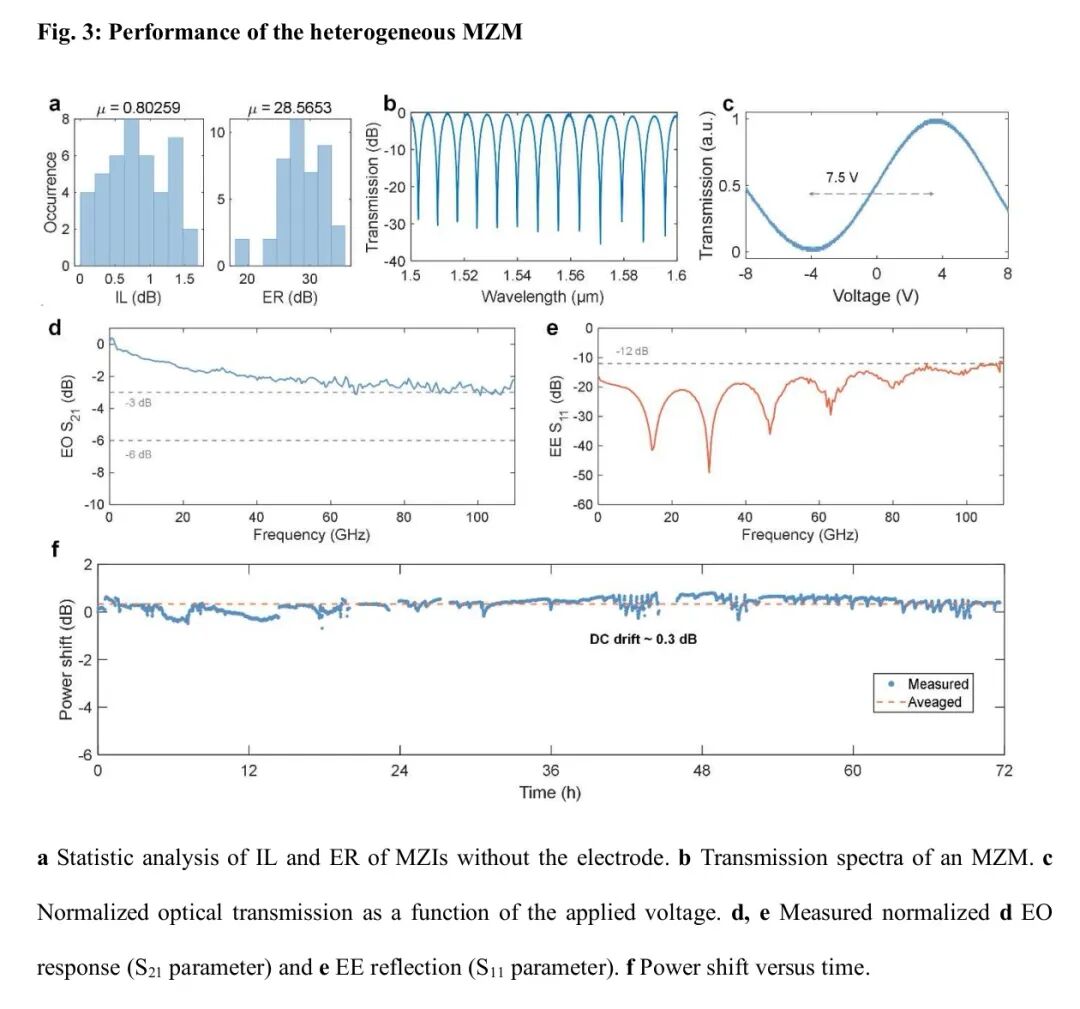

采用SITRI的低损耗400nm LPCVD氮化硅波导晶圆工艺,本身具备超低光学传播损耗(约4 dB/m)和宽透明窗口特性,与薄膜钽酸锂的超快速电光响应相结合,形成了兼具低损耗与宽频响的混合平台。器件制备过程中,所有42个器件在1.52-1.6um波长范围内均表现出稳定的传输特性,消光比普遍接近或超过20 dB,与统计结果(平均消光比28.6 dB)一致,进一步验证了微转印工艺的高一致性与高良率(95%)。

② 核心工艺实现

薄膜钽酸锂(TFLT)芯片由华中科技大学武汉国家光电研究中心(WNLO)制备:通过电子束光刻(EBL)系统(Vistec EBPG5200+)对带TFLT连接结构的器件进行图形化,采用反应离子刻蚀(RIE)工艺刻蚀,经HF基溶液刻蚀释放层后,薄膜钽酸锂芯片单元由连接结构固定并保持悬浮状态。

氮化硅芯片由上海工业技术研究院(SITRI)采用8英寸氮化硅晶圆制备:通过LPCVD技术沉积氮化硅薄膜,波导传输损耗低至0.04 dB/cm;经精密清洗与氧等离子体辐照激活后,目标芯片即可用于微转印(MTP)集成。

微转印过程采用定制设备完成:将带矩形柱的PDMS印章与悬浮的芯片单元对准并接触,快速拾取芯片单元后转移至目标芯片;微调芯片单元与目标芯片的相对位置,使芯片单元通过范德华力温和贴合并键合至芯片表面;通过逐步剥离PDMS印章实现与芯片单元的彻底分离,完成转移印刷过程,整个工艺在室温下进行。

金属化工艺由上海交通大学AEMD及物理与天文学院微纳制造平台完成:采用紫外(UV)接触光刻结合剥离工艺制备电极,调制器的行波电极由20 nm厚钛层与1000 nm厚金层构成。

③ 性能测试与多场景验证

该氮化硅基异质集成调制器在C波段的插入损耗仅为1.0dB,显著低于imec的损耗;电光带宽突破110GHz,为超高速信号调制提供了充足余量。稳定性测试中,器件在72小时连续工作期间的功率漂移仅0.3dB,展现出可靠的长期运行能力,解决了传统铌酸锂调制器的偏置漂移痛点。半波电压(Vπ)为6V,对应的电压-长度乘积(VπL)为4.08V·cm,在宽频范围内保持稳定的电光转换效率。

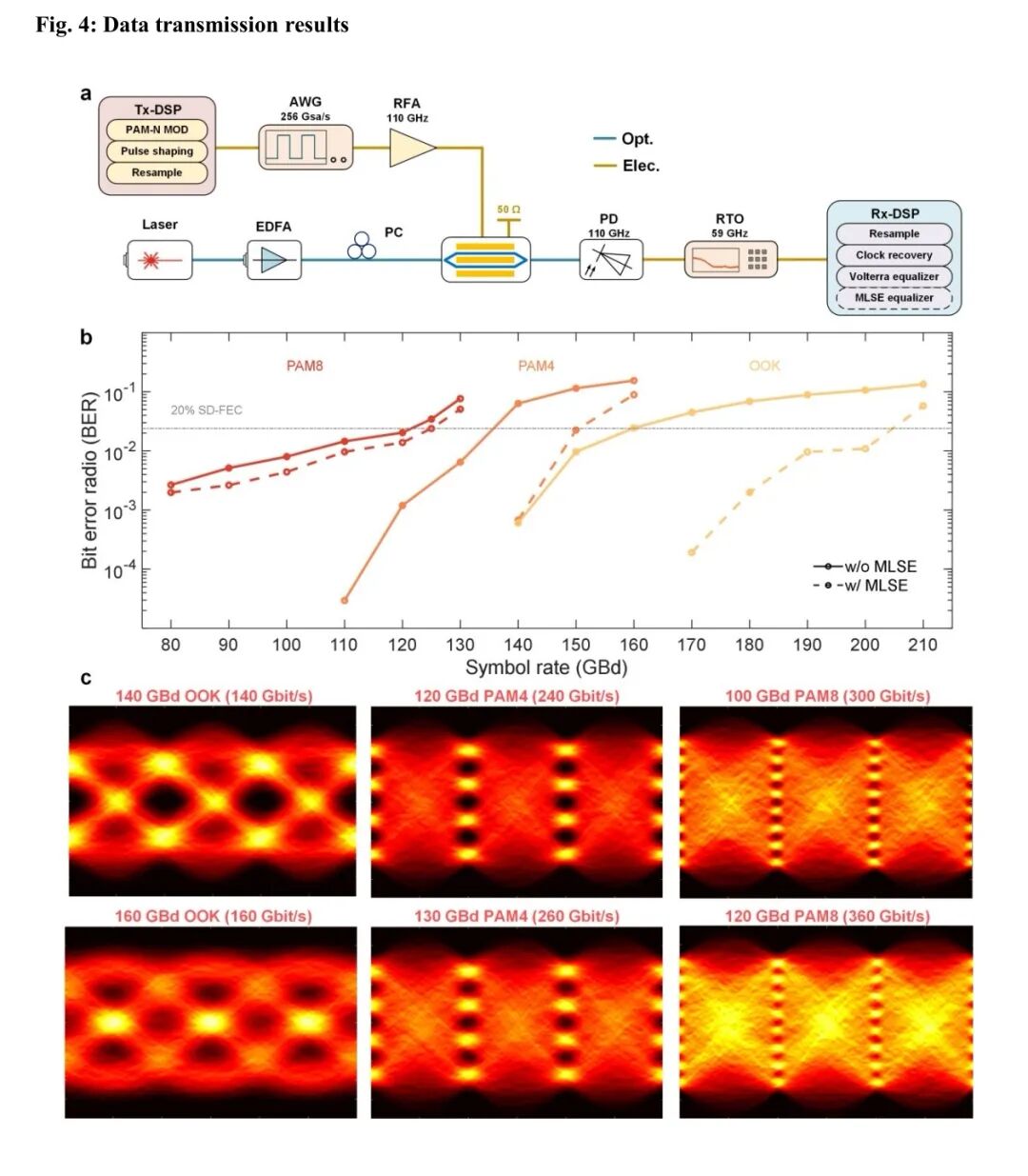

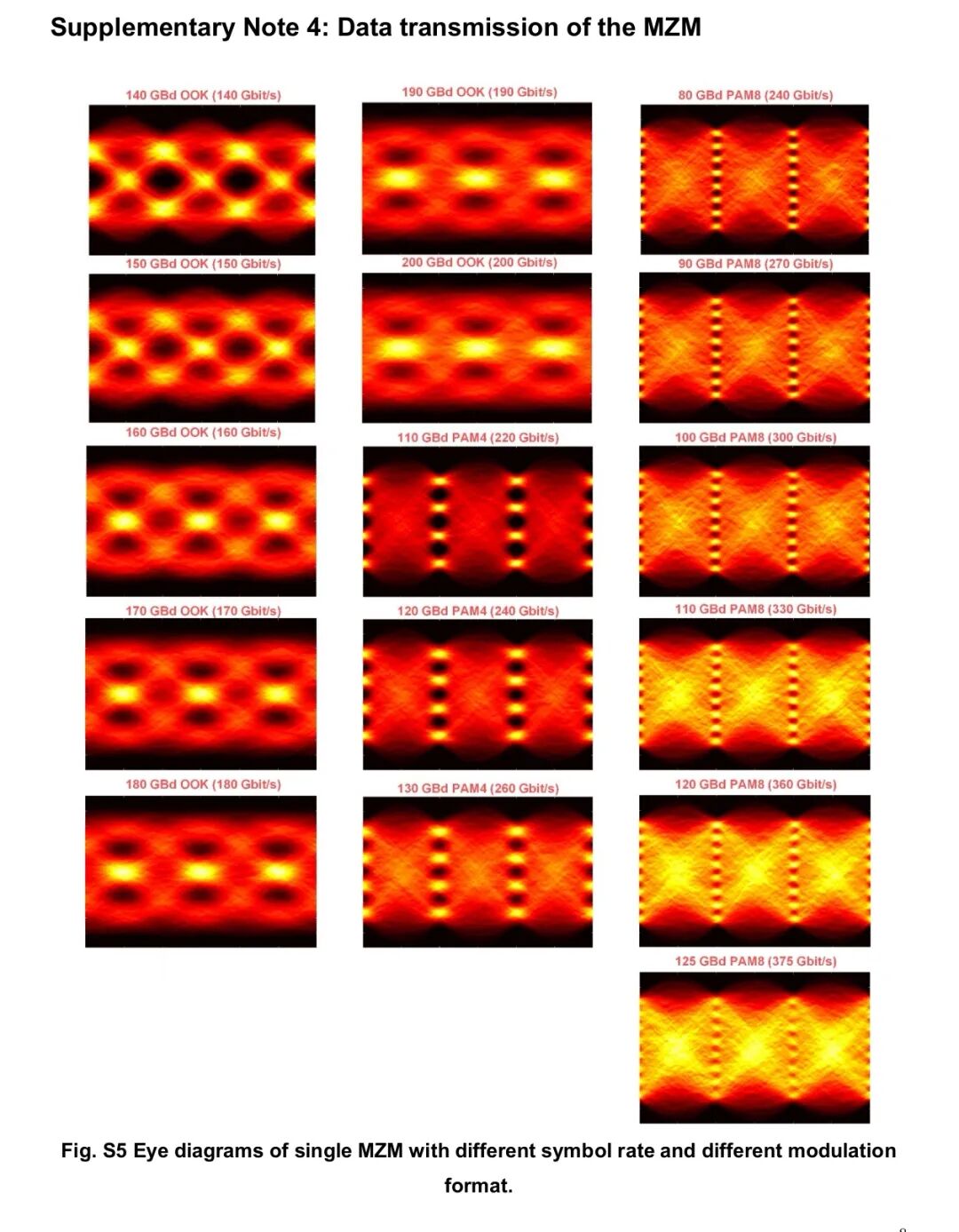

在光传输实验中,实现了200GBd NRZ、150GBd PAM4和125GBd PAM8强度调制的最高实测符号速率,最高调制速率达到375 Gbps,眼图清晰。

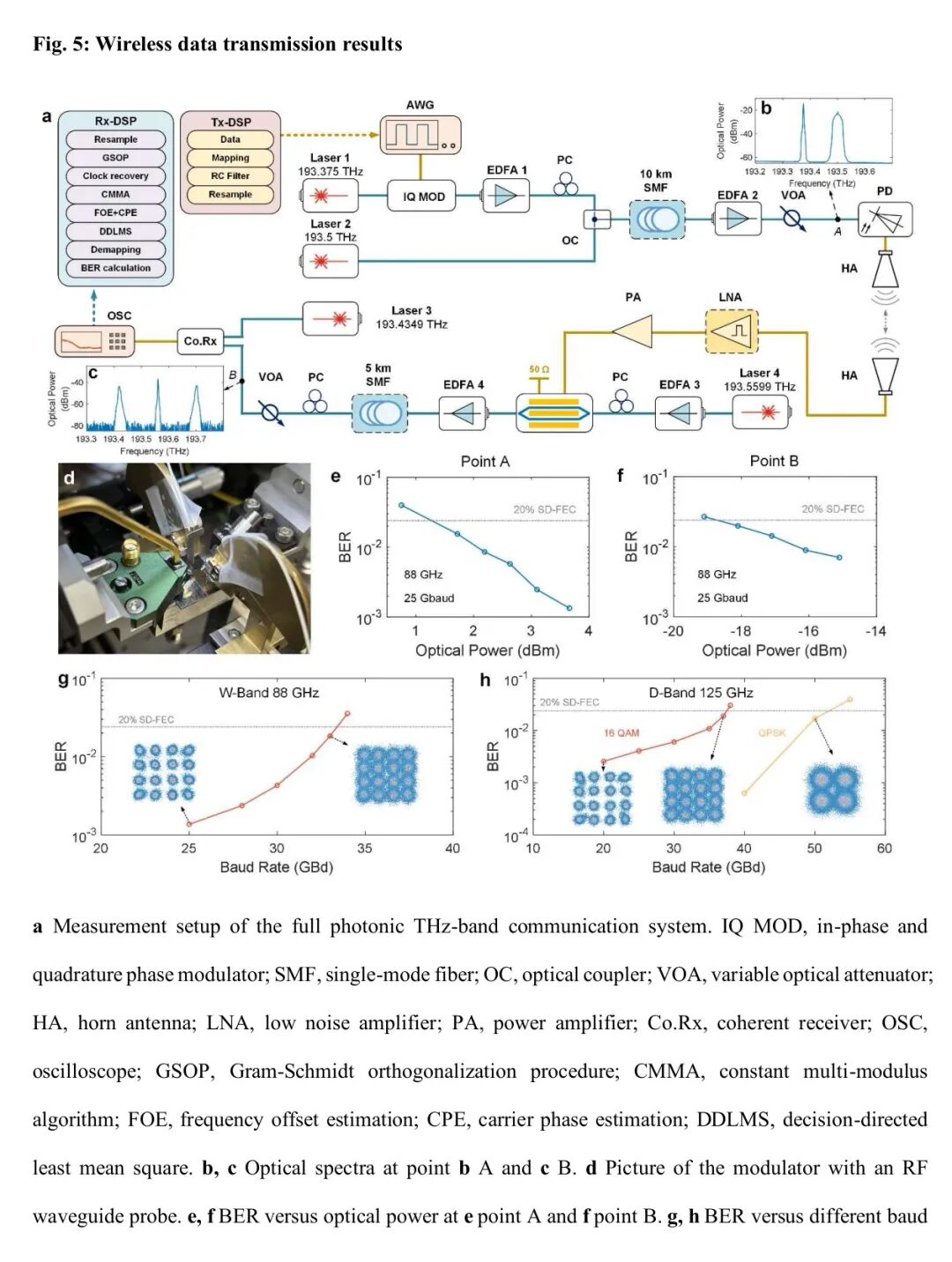

在太赫兹频段,该调制器展现出卓越的无线传输能力:W波段(88GHz)下达成132Gbps的传输速率,D波段(125GHz)传输速率进一步提升至148Gbps,创下该波段光子辅助通信的速率纪录。这一突破为短距离高容量无线通信提供了新的技术路径,有望满足未来5G-A及6G系统的传输需求。

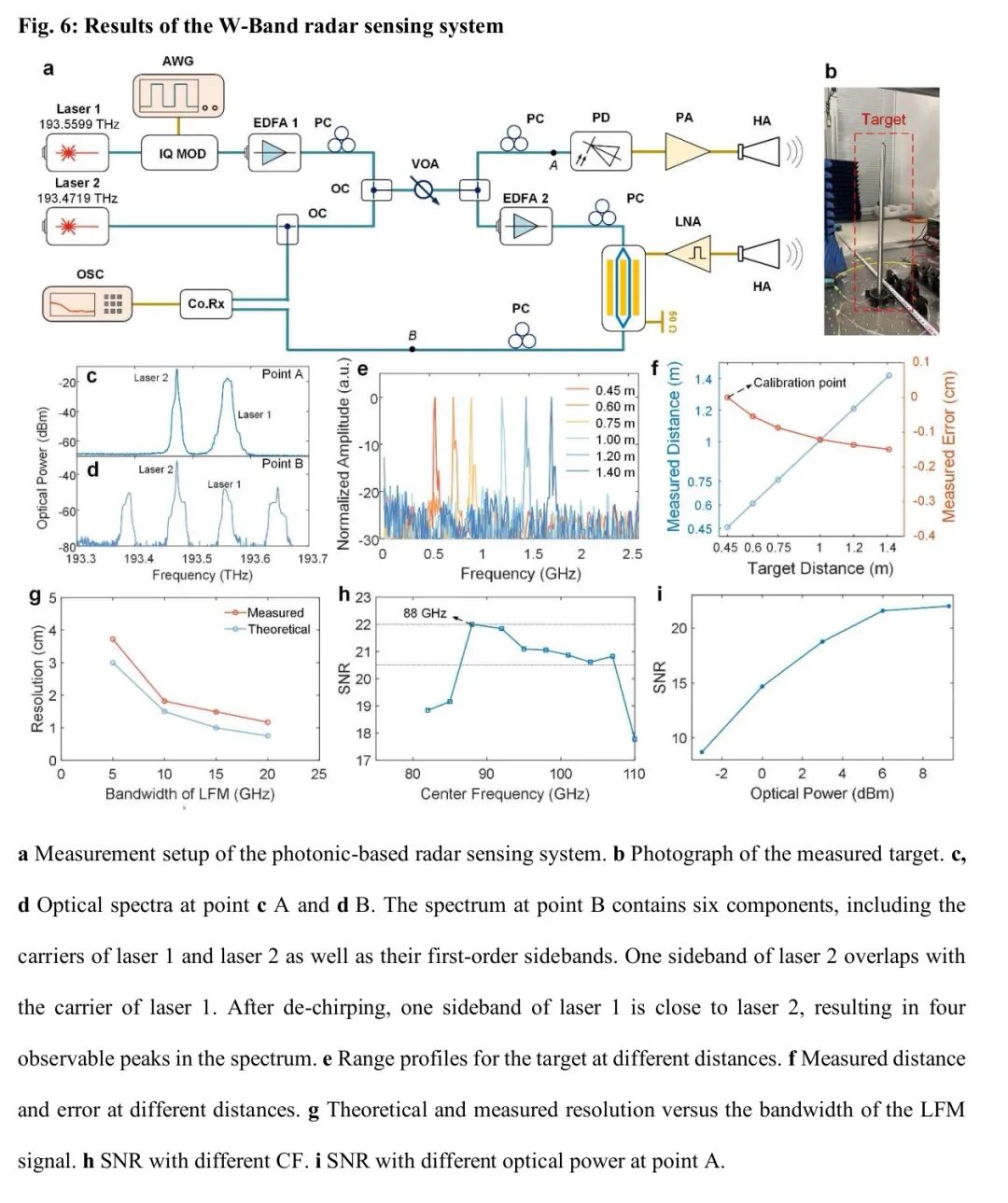

基于该调制器的W波段雷达系统采用调频连续波技术,实现了1.2cm的距离分辨率,测距误差小于2mm,且在88-107GHz频段内保持稳定的信噪比。优异的带宽特性与相位稳定性使得该系统能够精准捕捉目标的距离与速度信息,为高精度雷达传感应用提供了核心器件支撑。

◆ 技术对比与核心价值总结

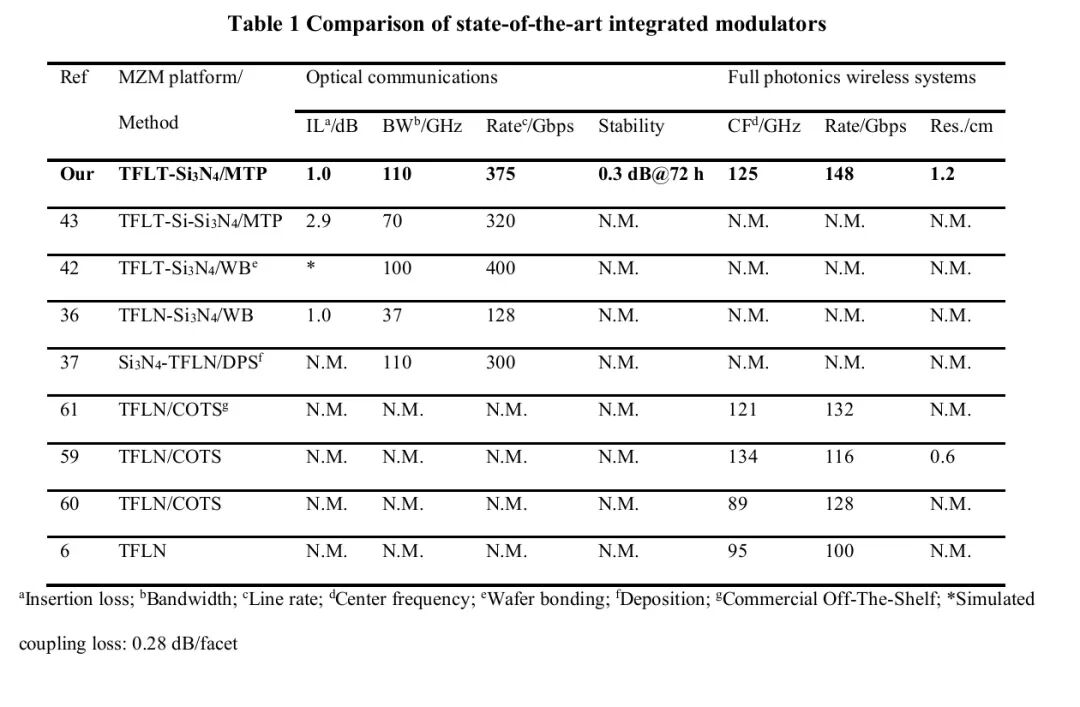

imec与上海交大/华科的薄膜钽酸锂异质集成工作的两款方案均实现了关键性能指标的突破:插入损耗分别低至2.9dB(Si/SiN)和1.0dB(SiN),电光带宽均超过70GHz,数据传输速率>300 Gbps,且在稳定性、良率等工程化指标上表现优异(上海交大良率95%,imec兼容CMOS工艺)。这些成果不仅解决了传统光电调制器的带宽瓶颈、损耗过高、稳定性不足等问题,更验证了薄膜钽酸锂作为下一代电光材料的可行性。

两者的研究共同证明,微转印驱动的薄膜钽酸锂异质集成技术,能够实现“高性能-高兼容性-规模化生产”的统一,为下一代光电集成系统的发展提供了核心技术支撑,有望在光通信、无线传输、传感探测等多个领域引发技术革新。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-01-22,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读