REF60xx:为了小宝贝少一颗运放,我为你集成

精密数据采集系统中ADC尺寸、功耗、分辨率和带宽的平衡(YUNSWJ 重写版)

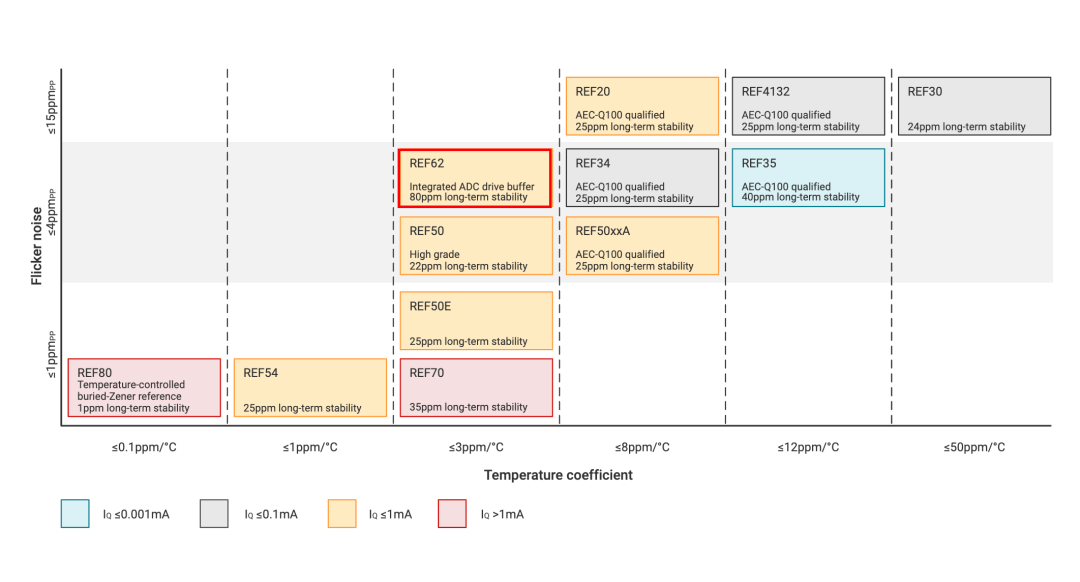

昨天的 ADC 文章看管可否尽兴?没事,今天来看看 TI 为之服务的基准源。如果说 ADI 是勇闯无人之境,那 TI 就是性价比老登。

属于串联电压基准

属于串联电压基准

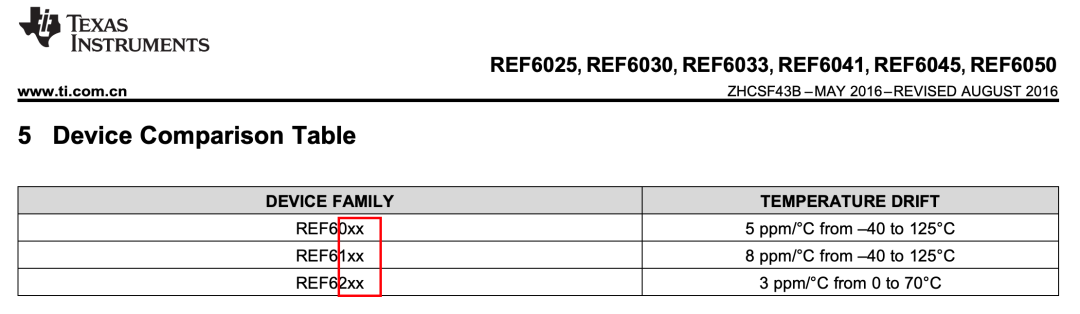

这个6x 家族是分的很细的,感觉就是一片晶圆上面进行了筛选:

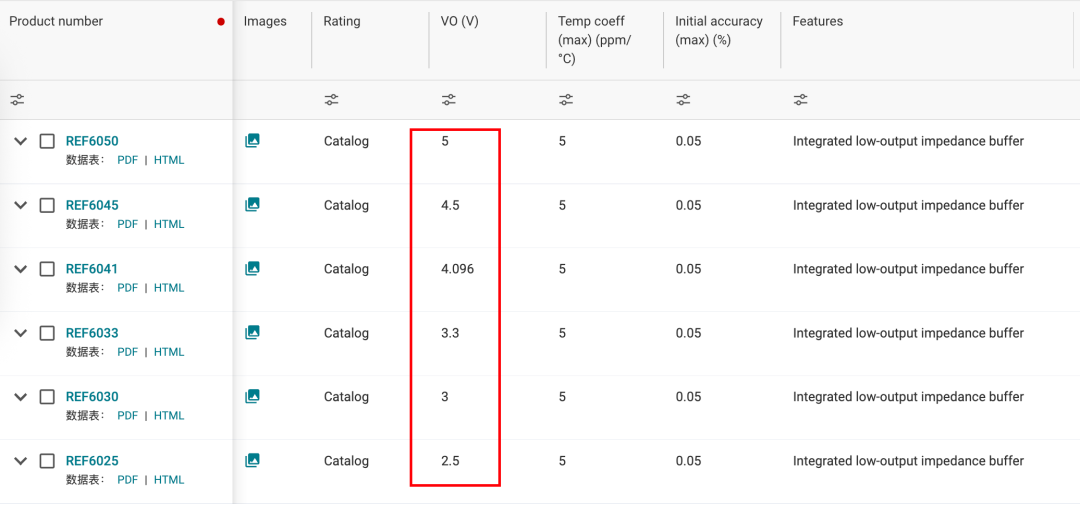

这次看这个 60 系列:

后面表示这个输出电压

后面表示这个输出电压

原来这东西还是属于电源啊?

原来这东西还是属于电源啊?

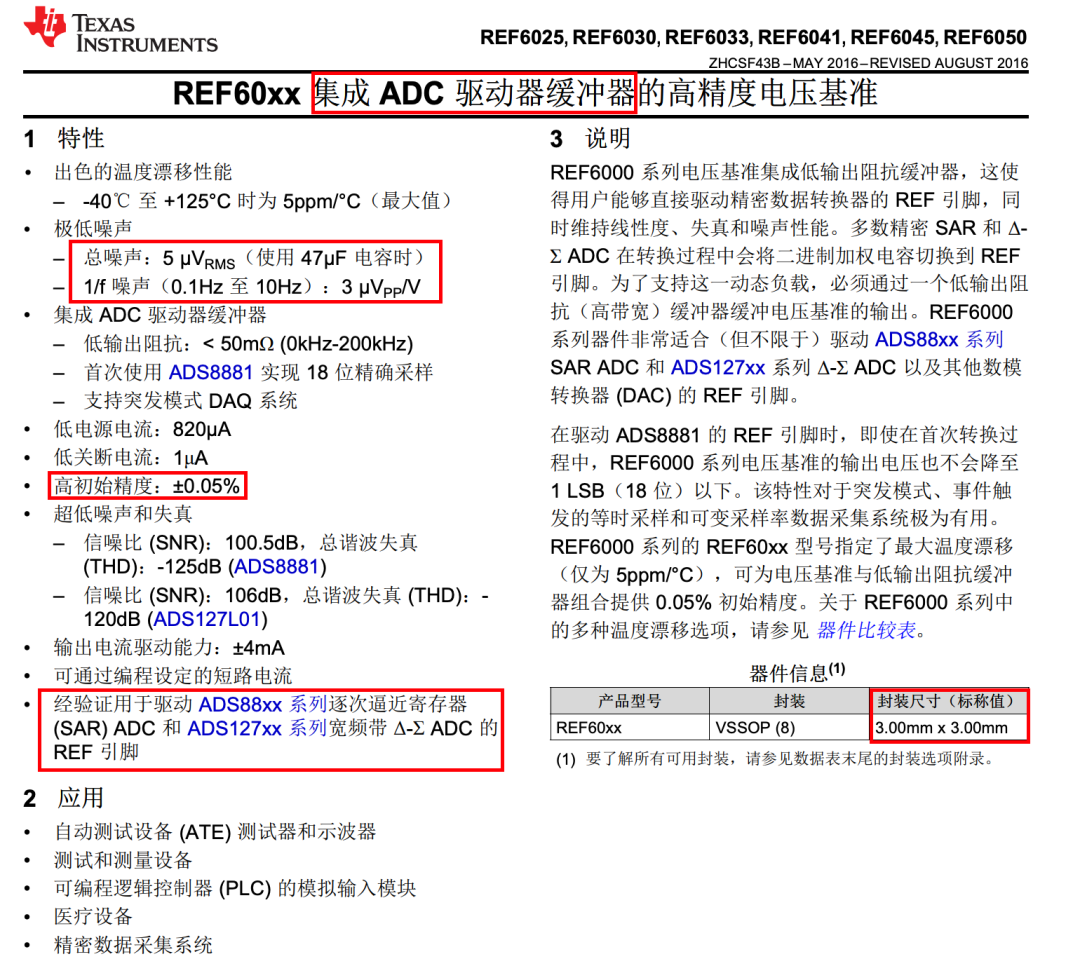

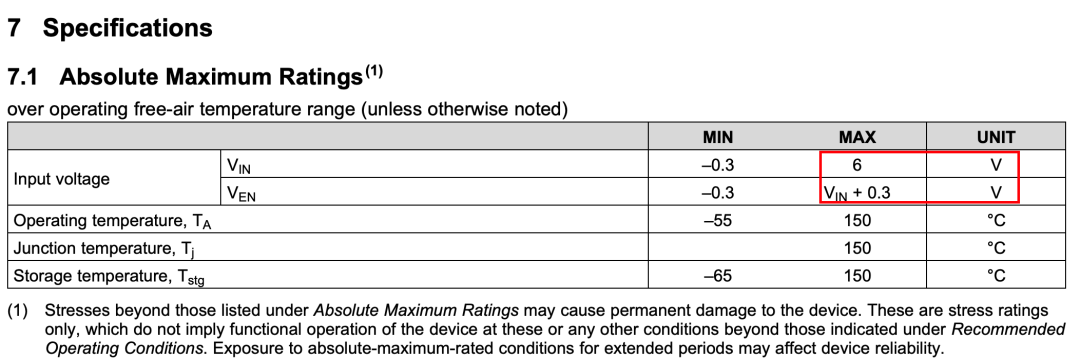

器件就是要看数据手册:

可以看到我喜欢的一些特性,特别是下面官方差不多就明说了,这个基准给谁用的

可以看到我喜欢的一些特性,特别是下面官方差不多就明说了,这个基准给谁用的

就是这样的一种设计,内部加了一个 buffer

就是这样的一种设计,内部加了一个 buffer

😄,直接用官方的资料说明

其实就是“给高精度 ADC 准备的一颗 4.096V 参考 + 专用缓冲运放,一颗芯片顶:基准源 + 参考缓冲 + 过冲 droop 控制”。

型号和定位

REF60xx 系列:REF6025/30/33/41/45/50,只是输出电压不同:2.5V、3.0V、3.3V、4.096V、4.5V、5.0V。

共性卖点:

集成 ADC 驱动缓冲器(ADC drive buffer)

温漂 ≤ 5 ppm/°C(–40~125°C 全温)

初始精度 ±0.05%

总噪声 5 µV_RMS(配 47µF 输出电容)

1/f 噪声 0.1–10Hz:3 µVpp/V

输出阻抗:0–200kHz 内 < 50 mΩ

供电电流典型 0.82 mA

专门用来直接驱动精密 SAR(ADS88xx)和宽带 ΔΣ(ADS127xx)的 REF 引脚,省掉外部缓冲运放。

基本电气规格怎么理解?

精度和温漂

输出精度 ±0.05%对 4.096V 来说:

这只是上电时的初始误差,后面还要考虑校准/标定。

温度系数 5 ppm/°C(Box 方法) 在 –40~125°C 温差 165°C 上:

对 4.096V 是:

所以全温漂+初始误差合起来也就几 mV 级,对 18bit 系统来说是可以通过一次性标定修掉的。

噪声

总噪声 5µV_RMS(CL=22 或 47µF)这个是“全集成噪声”,带宽大约到 1MHz;相当于 4.096V 上的:

0.1–10Hz 1/f 噪声:3µVpp/V对 4.096V:约 12.3µVpp,极低,适合慢速高分辨率采样。

噪声谱图(Figure 13 & 14):可以看到低频 1/f 下面是平的宽带白噪声,配 22/47µF 时噪声谱密度更低。

输出能力和负载

推荐输出电流:

REF6025/30/33/41:±4mA

REF6045:±3.5mA

REF6050:±3mA

输出阻抗:50mΩ(DC~200kHz),意味着即使瞬间抽出 10mA,电压下陷只有:

短路电流由 SS 引脚 + 电阻 RSS 设定,内部公式给出了 ISC 与 RSS 的关系,可以根据系统热设计把短路电流卡在几 10mA。

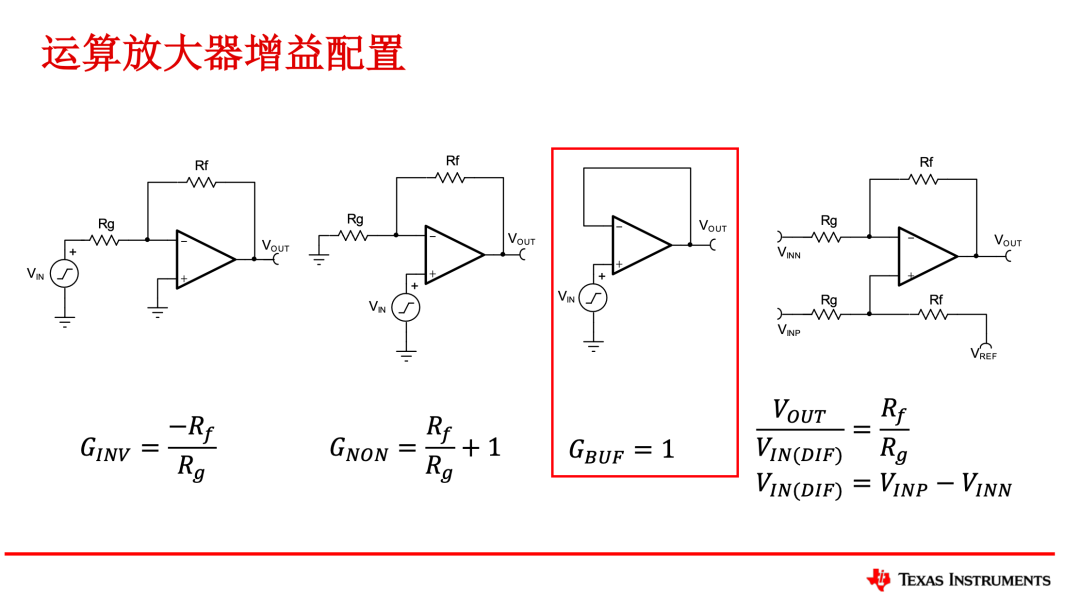

“集成 ADC 缓冲器”到底做了什么?

为什么普通基准不行?

大多数 SAR / 部分 ΔΣ 的 REF 引脚后面是一串二进制加权电容阵列。转换时,这些电容会:在每次转换开始时突然从 GND 翻到 VREF;再在比较过程中不断切换。

这等价于:在 REF 引脚上挂了一个输入信号相关、随时间跳变的电流源。如果只用“普通带隙基准 + 一个大电容”,问题是:参考源输出阻抗在 kHz 以上往往有几欧到几十欧;电容被一次次抽电、放电,电压来不及回到标称值,就会产生 droop(下陷);droop 大小跟输入信号有关 → 等效成非线性失真 + 增益随频率变化。

REF60xx 的做法

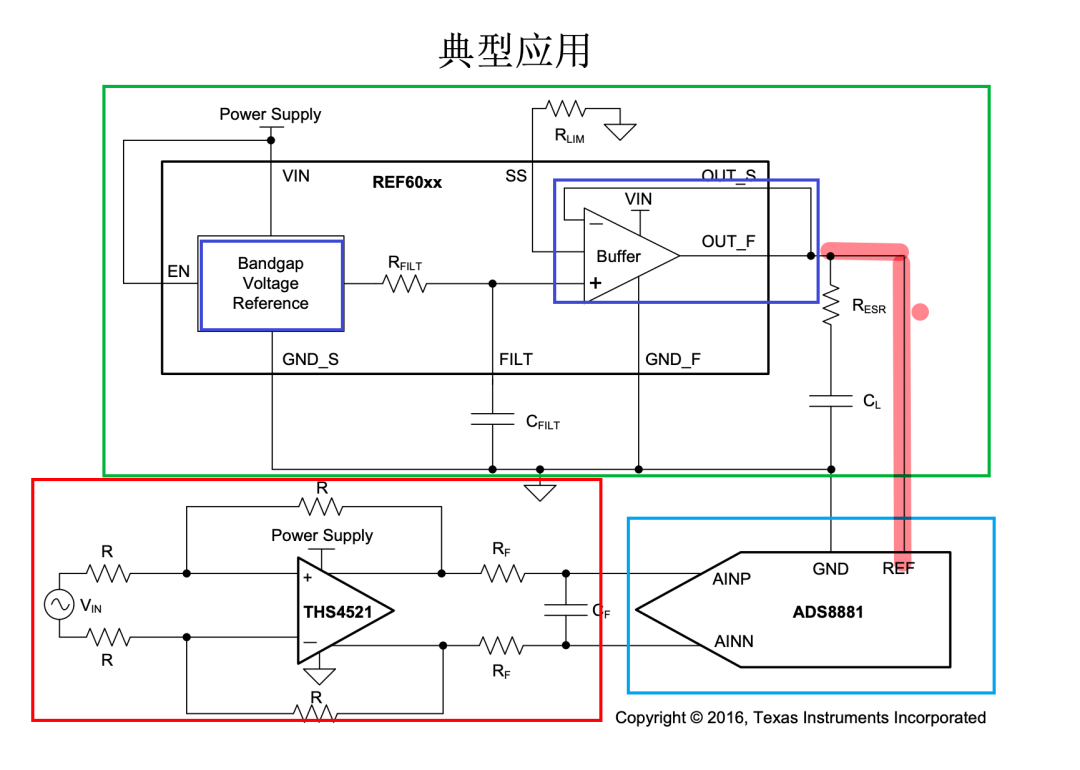

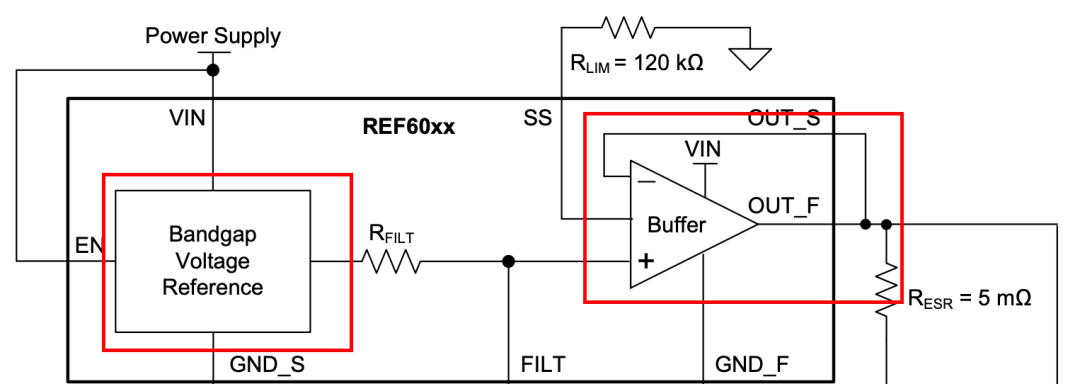

内部结构(Block Diagram):带隙参考 + RFILT + 宽带 Buffer + 两对 Sense/Force 引脚。

内部

内部

参考核心只需要提供缓慢变化的基准电压;高带宽缓冲器负责驱动 REF 电容和 ADC 参考电容,保证超低输出阻抗;OUT_S / OUT_F、GND_S / GND_F 可以 Kelvin 连接,消除走线压降的影响。

文中直接给了一个定量评价:

REF60xx 在驱动 ADS8881 (18bit, 1MSPS) 时,甚至在“第一转换”里,参考电压 droop 也 小于 1 LSB。

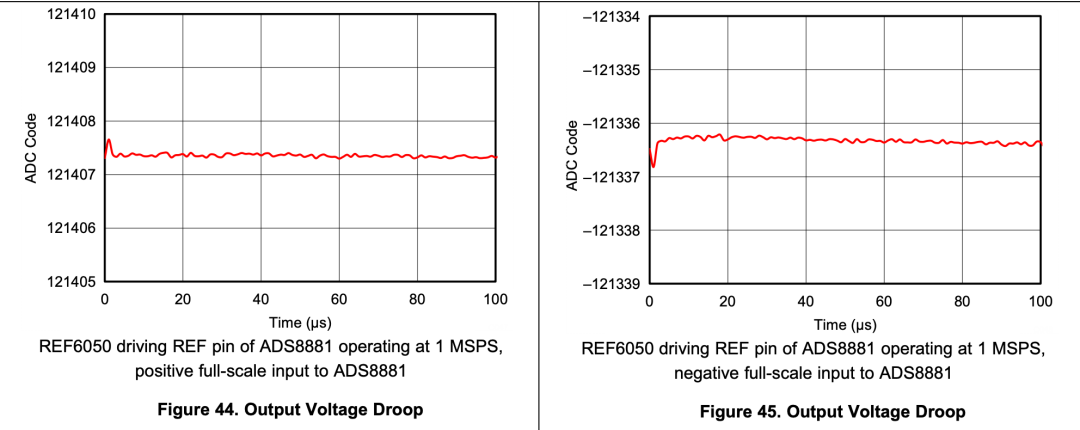

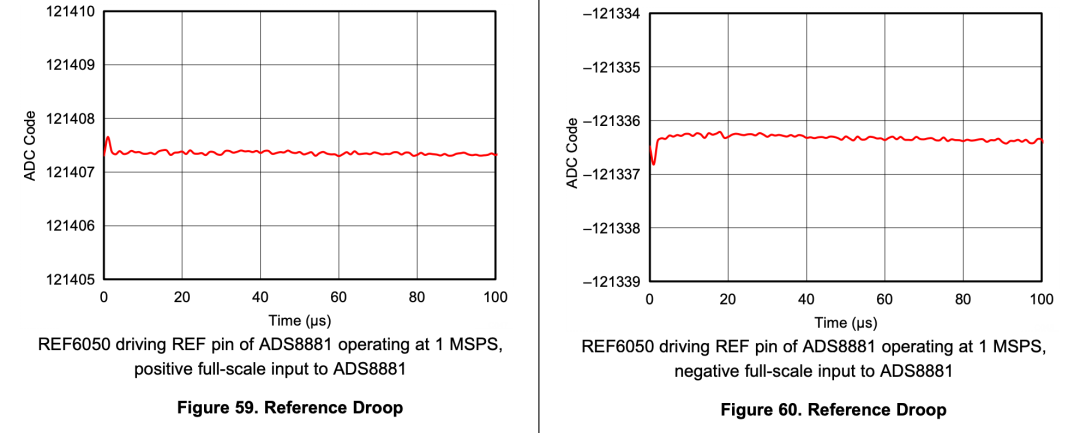

图 44–45 / 52 / 59–60 对比了:

普通参考(REF20xx)+ 输出电容:参考电压在前几次转换里会明显下陷几 LSB;REF60xx:整个 100µs 的 burst 里,droop 保持在 ±1 LSB 内,且无明显随采样改变的偏移。

这就是它敢宣传“burst-mode first sample 18bit 精度”的根本原因。

噪声、THD 和系统性能

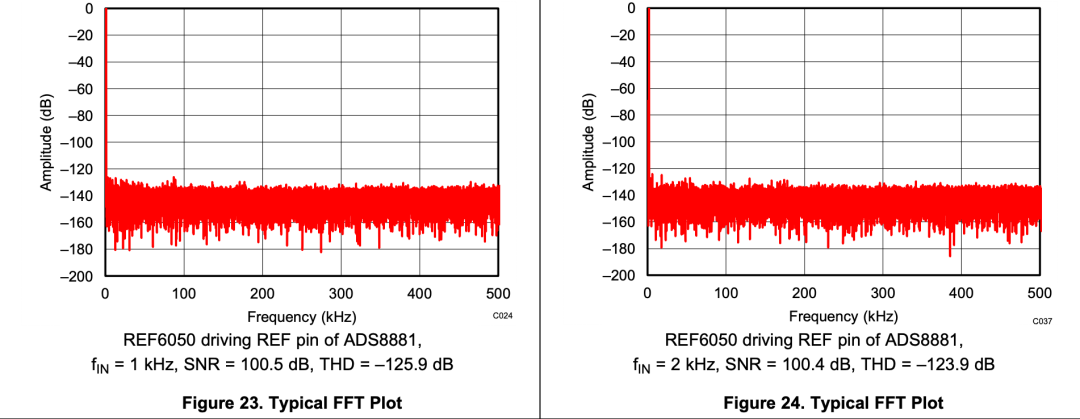

典型应用用的是 REF6050 / 驱动 ADS8881,输入由 THS4551 差分运放驱动。

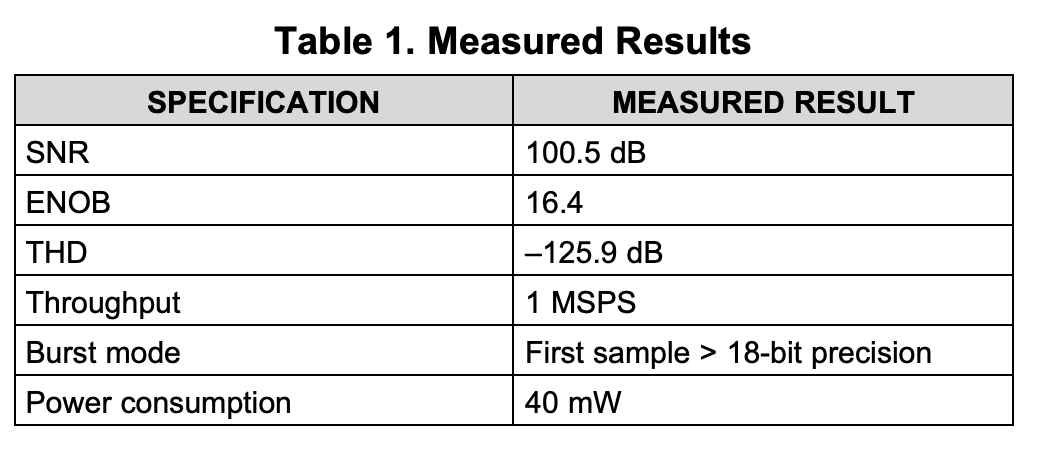

测得指标(Table 1):

SNR ≈ 100.5 dB

ENOB ≈ 16.4 bit

THD ≈ –125 dB

采样率 1MSPS、功耗 40mW

Burst mode 下首个采样也有 18bit 以上精度

频谱图(Figure 23–31)

完全的图可以看手册

完全的图可以看手册

可以看到:

主基波外的谐波都在 –120dB 以下;噪声底接近 ADC 自身理论极限,说明参考并没有拉低系统性能。

这一组图想表达的是:只要按推荐拓扑搭,系统性能会被 ADC 自身限制,而不是被参考拖后腿。

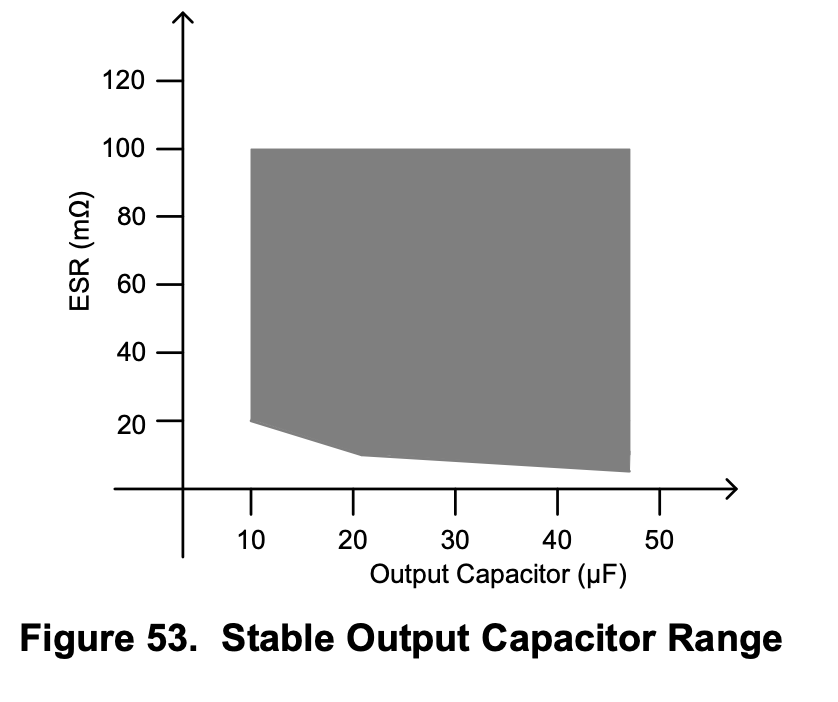

稳定性:输出电容和 ESR 的要求

REF60xx 对输出电容有明确要求,这是“带缓冲器参考”与普通参考最大的实用差异之一。

输出电容 CL:10–47µF

10µF 时,需要 ESR 在 20–100mΩ;

47µF 时,ESR 在 5–100mΩ。 数据手册用一张阴影图(Figure 53)给出了“稳定区域”。

FILT 引脚电容 CFILT:必须 ≥1µF

接在内部带隙和缓冲器之间,用来降低宽带噪声;推荐低 ESR(5–20mΩ),可以用走线电阻 + MLCC 自然形成。

工程实现上一般直接用 10–47µF X5R/X7R MLCC;PCB 走线拉长一点,就顺带把 ESR 从几 mΩ 拉到十几 mΩ,落在稳定区里;如果想增加带宽、改善负载瞬态,可以刻意串一点电阻提高 ESR,但代价是噪声增大。

可靠性:焊接热漂移、热滞后、长期漂移

这部分是很多人会忽略,但对高精度系统很关键。 (关键确实关键,以后写)

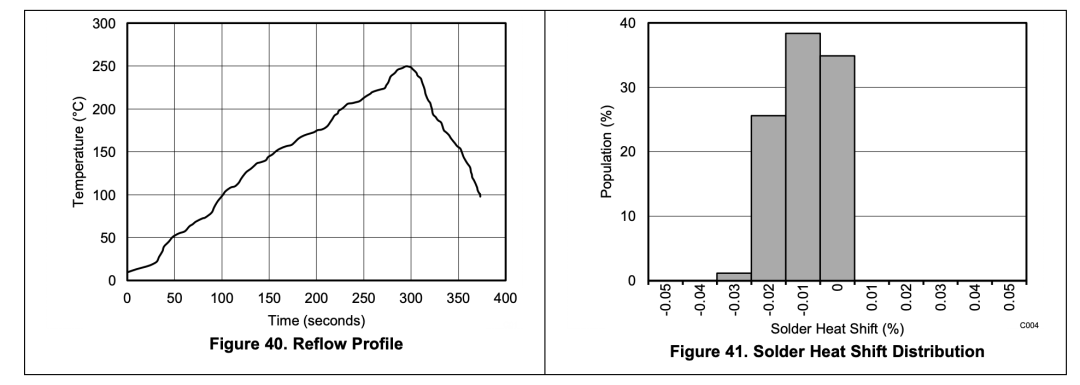

Solder Heat Shift(焊接热致偏移)

实验:128 颗芯片、8 块 PCB,用无铅回流曲线焊接前后对比输出电压。

结果:大部分样品偏移在 ±0.03% 以内。

多次回流会叠加偏移,所以基准尽量在 PCB 最后一面最后一趟回流焊。

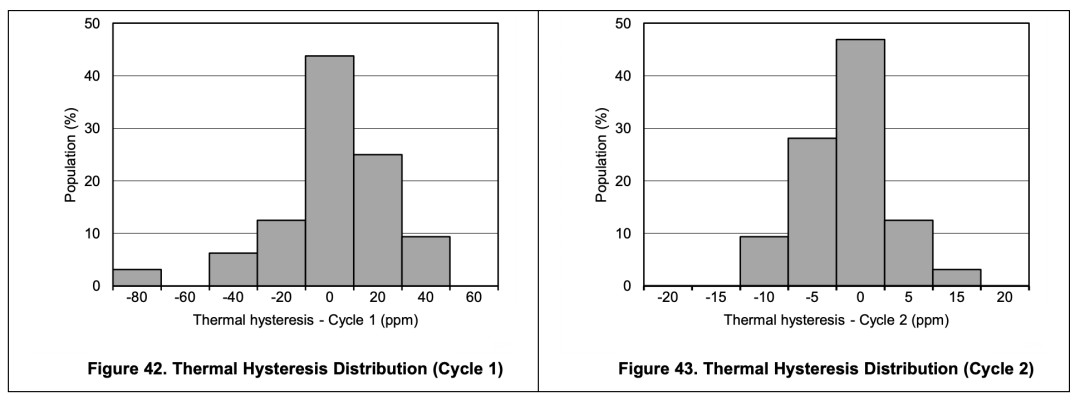

Thermal Hysteresis(热滞后)

image-20251228093746602

定义:25°C → –40°C → 125°C → 25°C,再测输出电压的变化;

典型值:Cycle1 约 33ppm,Cycle2 降到 8ppm;

第一次“热循环”把内部应力释放一部分,后面就稳定下来。

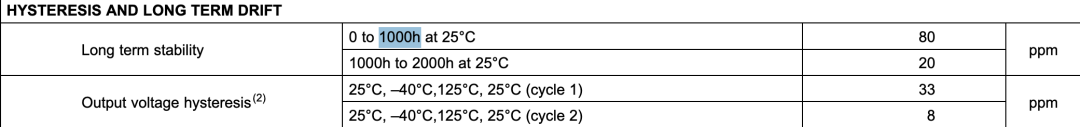

长期漂移

0–1000h:典型 80ppm;

1000–2000h 再追加:20ppm;这对一般工业应用(几年)是可接受的级别。(高端这个东西是一点也上不了)

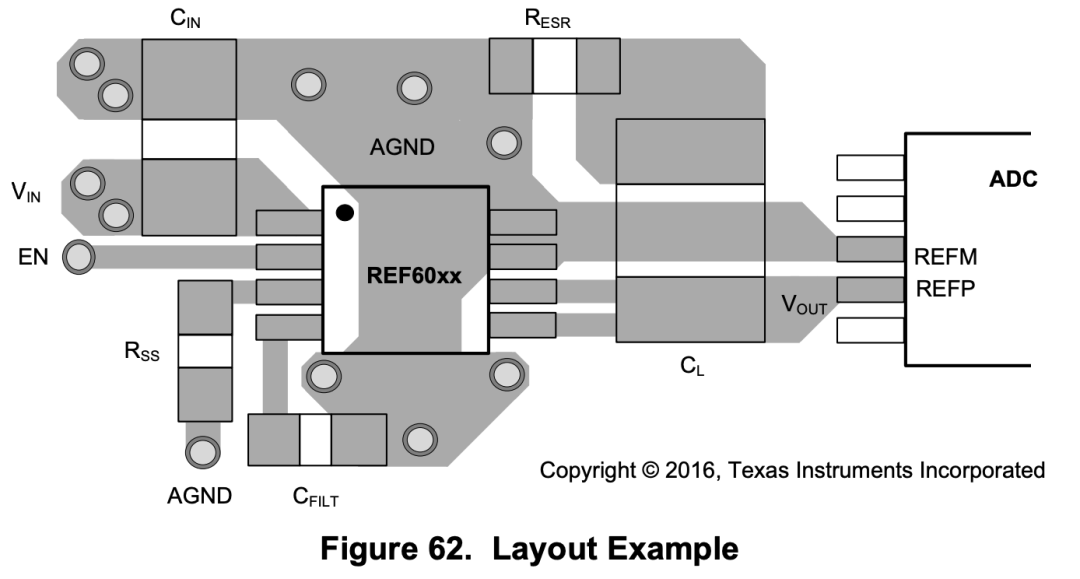

布局建议

数据手册给了一张 layout 示例(Figure 62):

VIN 去地旁边放 0.1µF 退耦;

输出电容 CL 尽量靠近 REF60xx & ADC REF 引脚;

OUT_F 和 OUT_S 各走一条线到 CL,一起再去 ADC REF,引脚尽量短;

GND_F / GND_S 在芯片下方用铜皮连,扩展成模拟地平面;数字线远离参考区域,避免数字噪声耦合。

工程上怎么用这个基准源?

先选电压:SAR ADC 满量程如果是 ±VREF、0~VREF,而想要 4.096V(方便把代码直接当 mV 读),就用 。

供电:给大约 4.3–5.5V,比如和 ADC 同一个 5V LDO。

电源很宽

电源很宽

电容:

REF 输出 → 47µF X7R + 0.1µF 小电容并联;

FILT → 1µF X7R;

附带考虑 MLCC 的实际 ESR,基本能落入稳定区。

驱动对象:

直接挂到 SAR / ΔΣ ADC 的 REF 引脚(比如 ADS8881、ADS127L11、ADCS124S08 这一类);不需要再加 OPAx333 之类的缓冲。

关注 droop 与 ENOB:如果应用是 burst-mode、事件触发采集(比如 CbM、示波器等), 的 droop 表现保证首个采样就能达到 18bit(ADS8881 的例子)。

如果 ADC 没有达到数据表说的 ENOB,至少可以先排除“参考 droop 不够”的锅。

后记

它是一颗“专门为高分辨率 ADC 设计的 4.096V 低噪声参考 + 宽带缓冲器”,它解决的是:参考 droop、线性失真、burst-mode 首采样精度、布局复杂度这些在精密数据采集里很麻烦但常被忽视的问题。按它推荐的电容和布局接上,基本不用再纠结“要不要多加一颗参考缓冲运放”。

https://www.ti.com.cn/cn/lit/ds/symlink/ref6041.pdf?ts=1766883471622&ref_url=https%253A%252F%252Fwww.ti.com.cn%252Fproduct%252Fcn%252FREF6041%253Flogin-check%253Dtrue

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-12-28,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录