为测量基准源 uV 级别跳动设计信号链(完结篇)

为测量基准源 uV 级别跳动设计信号链(YUNSWJ 仿真版)

昨天基准源测量的文章大家还是讨论的挺激烈的,今天把后半段的内容写了;昨天的最后有一个演示说时间轴没有对齐,

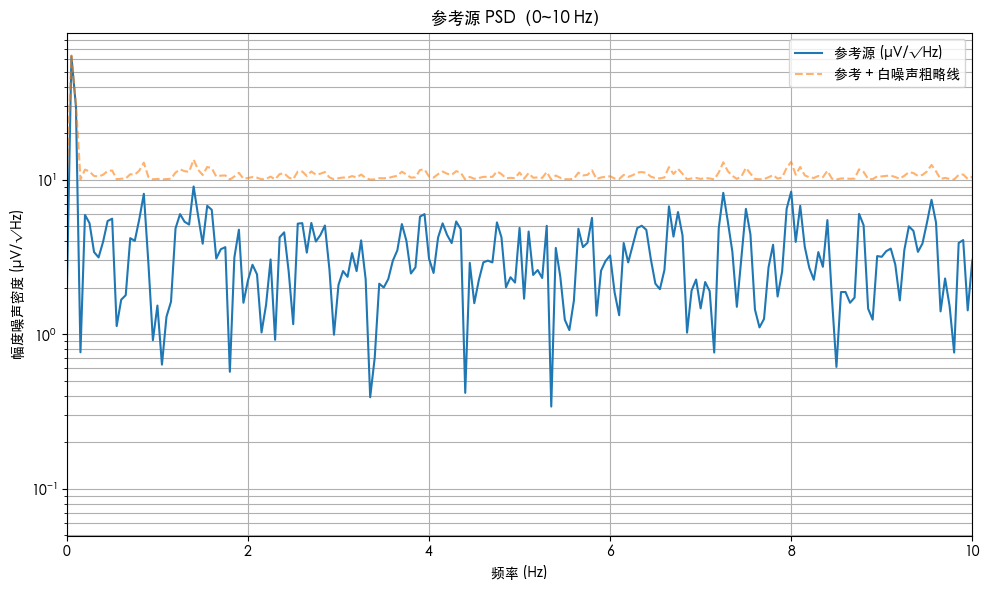

用 FFT / PSD 对滤波前后进行积分,算出真正等效噪声(µV_rms)

重新生成了:

真实参考源 v_ref(t):包含低频漂移(0.05 Hz)、随机游走、40 µV_rms 高频抖动

目标 ADC 测量(10 µV_rms 噪声):模拟了一个与需求接近的“系统噪声”

然后使用严格的Welch 方法计算功率谱密度 PSD(单位 V²/Hz),并在以下带宽内对 PSD 积分计算: 0 ~ 10 Hz; 0 ~ 1 Hz; 0 ~ 0.2 Hz

这些都是真正关心的低频噪声区间。

结果

=== 严格 PSD 积分得到的等效噪声 ===

参考源 0~10 Hz 噪声: 19.53 µV_rms

ADC结果 0~10 Hz 噪声: 19.80 µV_rms

参考源 0~1 Hz 噪声: 16.03 µV_rms

ADC结果 0~1 Hz 噪声: 16.16 µV_rms

参考源 0~0.2 Hz 噪声: 15.57 µV_rms

ADC结果 0~0.2 Hz 噪声: 15.68 µV_rms

ADC 10 µV_rms 噪声基本不会破坏低频波形,看 0~10 Hz:

参考源噪声:19.53 µV_rms

ADC 测量:19.80 µV_rms

也就是说:

在 10 Hz 带宽内,ADC 加进去的的 10 µV_rms 噪声,并不会把系统噪声从 19 µV 推到 50 µV;它只是轻轻“抬高”一点点(差 0.3 µV_rms)。

这是非常好的结果,ADC 目标噪声(10 µV 级)是合理的,不会显著掩盖参考源自身的抖动。

带宽越窄,噪声被 PSD 积分“自然过滤”,差异更小

在 0~1 Hz:

参考源:16.03 µV_rms

ADC 测量:16.16 µV_rms;差异只有 0.13 µV。

看 0~0.2 Hz:

参考源:15.57 µV_rms

ADC:15.68 µV_rms;差异只有 0.11 µV。

也就是说:低频 (<1Hz),ADC 的 10 µV 噪声几乎完全被带宽滤掉了。

更加精细的仿真

在这条链上加:前端运放噪声,电阻热噪声,参考源 1/f 噪声,实际 ΔΣ ADC 的 sinc 滤波器响应,OSR 对低频噪声的影响。

在一个工作点(OSR = 256)下的噪声

=== 噪声预算示例:OSR = 256, 带宽 B = 10.0 Hz ===

参考源 0.1-10Hz 噪声 : 15.000 µV_rms

放大器白噪声 : 0.032 µV_rms

放大器 1/f 噪声 : 1.000 µV_rms

电阻热噪声 : 0.041 µV_rms

ADC 白噪声 (OSR=256) : 1.600 µV_rms

ADC 0.1-10Hz 噪声 : 2.000 µV_rms

量化噪声 : 0.003 µV_rms

-----------------------------------

总噪声 : 15.250 µV_rms

也就是说,在我们假设的这套链路里,0–10 Hz 带宽内:

参考源自己:15 µV_rms

ADC 内部白噪声(经过 OSR=256 的滤波):1.6 µV_rms

ADC 低频 0.1–10 Hz 噪声:2 µV_rms

运放 + 电阻:全部加起来也就几 0.0x µV_rms + 1 µV

量化噪声:0.003 µV_rms,可以忽略

RSS 合成以后,总噪声:

≈ 15.25 µV_rms

几乎完全由基准源本身决定,ADC 和前端只略微“添了点噪声”;这和我们上一轮 PSD 积分看到的“参考 19.5 µV,ADC 后 19.8 µV”是同一个结论:

只要 ADC 噪声控制在 10 µV 级别以内,系统测量的是“参考源的噪声”,而不是 ADC 自己的噪声。

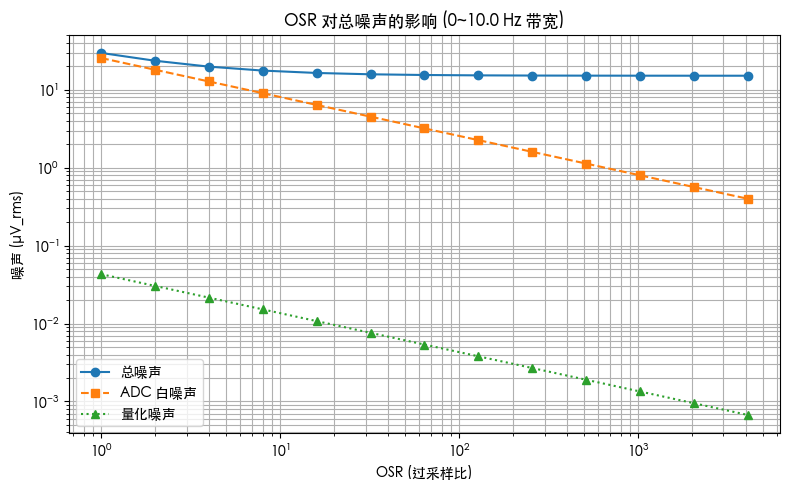

OSR 对总噪声的影响:那张 log–log 曲线

图上三条线:

蓝色:总噪声(系统整体)

橙色:ADC 白噪声(随 OSR 下降)

绿色:量化噪声(更快地随 OSR 下降)

随着 OSR 增大,ADC 白噪声大幅下降:OSR 从 1 → 256,ADC 白噪声大概按 下降,从几十 µV 一直降到 1.6 µV_rms 级别。

量化噪声几乎“消失”;24 bit + 高 OSR 条件下,量化噪声一直在 0.0x µV,完全可以认为“不是问题”。

总噪声曲线在 OSR > 100 左右基本“平了”

为什么?因为这时 ADC 噪声已经降到远低于参考源 15 µV 的水平,再继续加 OSR,降低 ADC 噪声,也不会显著降低总噪声——你已经被参考源本身的噪声 floor 限制住了。

OSR 用来打压 ADC 自己的噪声;当 ADC 噪声低到“比参考还安静”之后,再堆 OSR 就没收益了。

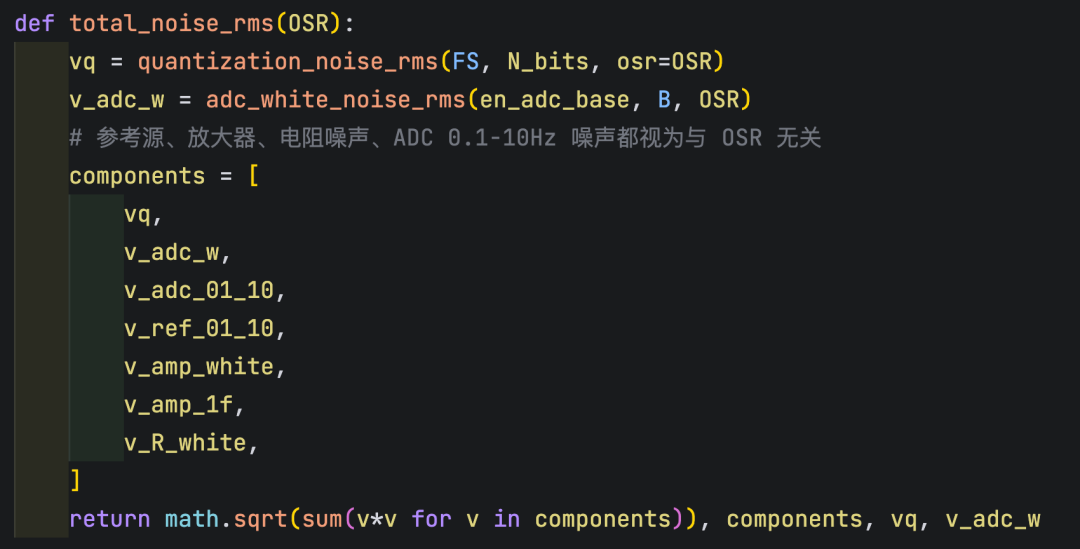

数学关系

量化噪声

满量程 FS,位数 N:

考虑 ΔΣ + 数字滤波,过采样比 OSR 时:

ADC 白噪声(随 OSR 降低)

假设 OSR = 1 时,ADC 内核白噪声密度为 :

我们用“OSR=256 时白噪声 ≈ 1.6 µV_rms”反推出:

这里可以换成真实芯片的数据。

其它噪声源(假设与 OSR 无关)

参考源 0.1~10 Hz 噪声:datasheet 直接给的是 µV_pp 或 µV_rms,直接用。

放大器白噪声:

放大器 1/f 噪声:datasheet 若给 0.1–10 Hz 噪声,直接当一个 RMS 值。

电阻热噪声:

总噪声(RSS)

所有噪声源视为互不相关:

这个就是我们在 Python 里封装的 total_noise_rms(OSR) 函数。

通过这套模型,现在可以非常清晰地说:参考本身低频噪声在十几 µV_rms 量级;若 ADC + 前端设计后,总噪声 ≈ 15 µV_rms(在 OSR≈256 条件下);这时参考本身“摇晃 40 µV”,而且测量噪声只有 15 µV_rms:能清楚地看见抖动;也能做统计(标准差、 Allan variance 等);更重要的是ADC 不会成为主矛盾。

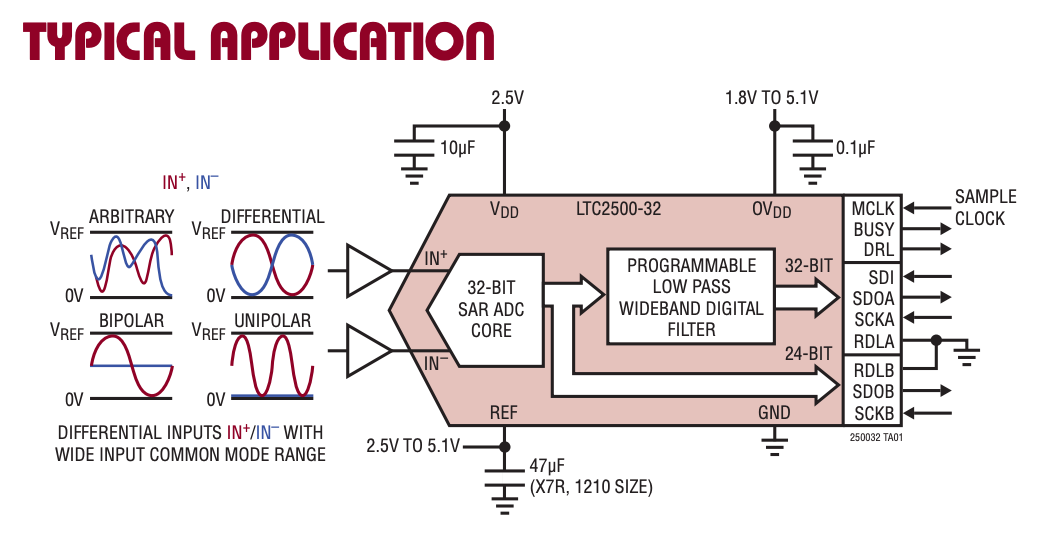

选一个ADC算算:LTC2500

因为有俩路

因为有俩路

LTC2500 有两条完全不同的通路,其“噪声路径”也是两个:

无延时输出(SDOB 那一路)

这个就是 1 Msps 的 32-bit 复合码:1bit 过载标志 + 24bit 差分码 + 7bit 共模码

数据手册给了这一路的 SNR = 104 dB @ 1 Msps, fIN=2 kHz, VREF=5 V ;主要用在宽带、瞬态场景(波形捕获、频域分析)。

带数字滤波的高精度输出(SDOA 那一路)

内部 32-bit SAR + 可配置数字滤波 + 下采样(DF)

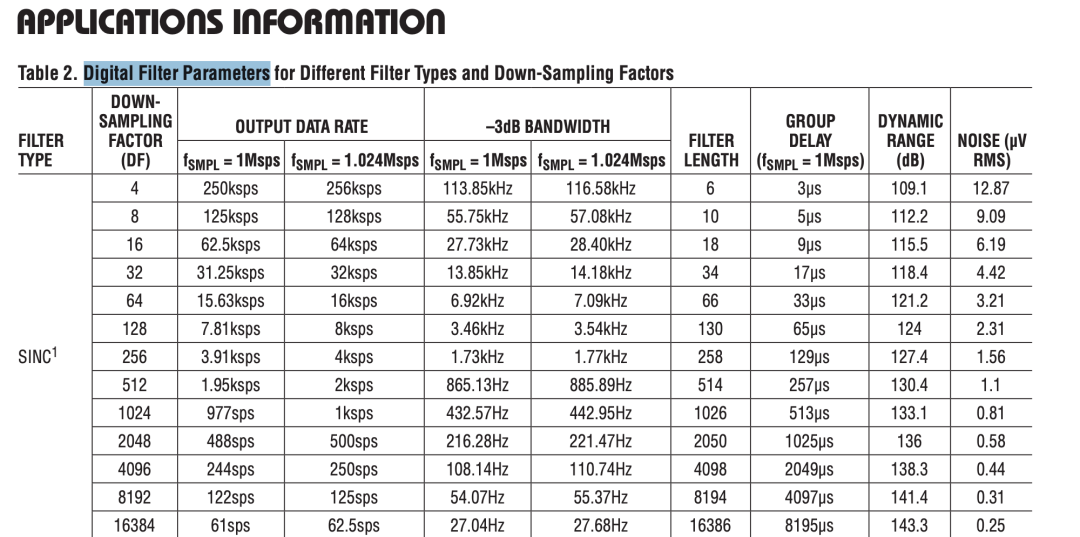

数据手册在 Table 2 “Digital Filter Parameters…” 里,已经给出了每种滤波器、每个 DF 的:

Dynamic Range (dB)

Noise (µV RMS) —— 这是我们要用的那一列

适合慢速、高分辨率测量(比如电桥、应变、压力、地震等);后面要做噪声预算、最小可测量量,基本肯定是用带滤波的那一路(SDOA)。

“偷懒”的方法——直接用 Table 2 的“Noise (µV RMS)”

假设用 VREF = 5 V(datasheet 默认就是 5 V 参考),选择了某个滤波器和 DF,那么:

ADC 输入端等效噪声(RMS):就是表 2 里这一行的 “Noise (µV RMS)” 那个数。

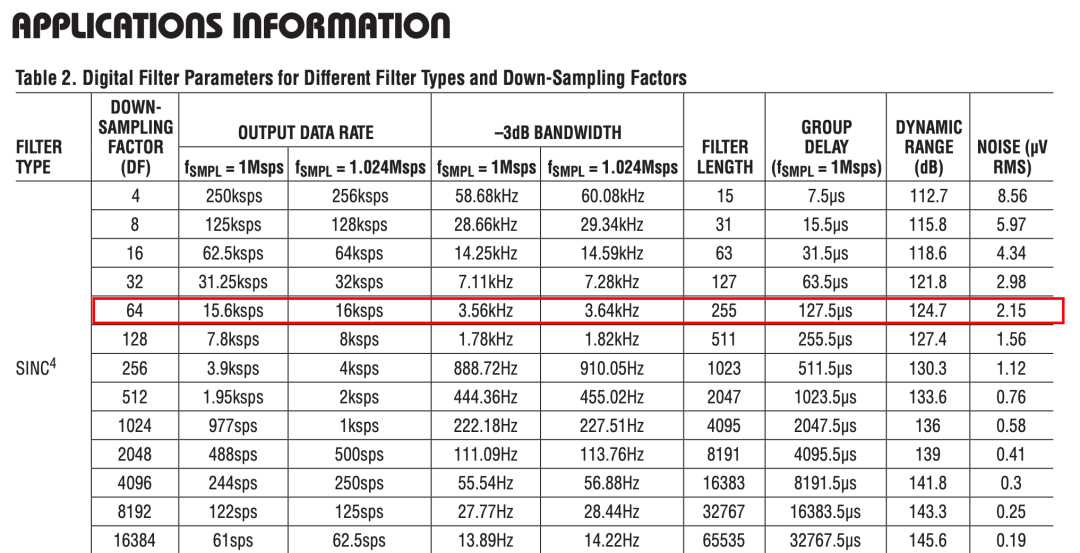

举典型例子(VREF=5 V,fSMPL=1 Msps):

SINC4, DF = 64(常用的一个组合)

表 2 中大致是:

过滤类型:SINC4

DF = 64

输出速率:约 15.6 ksps

动态范围:约 124.7 dB

Noise ≈ 2.15 µV RMS

那么在噪声预算里,就可以直接写:

ADC 输入噪声:

在该滤波器组合下

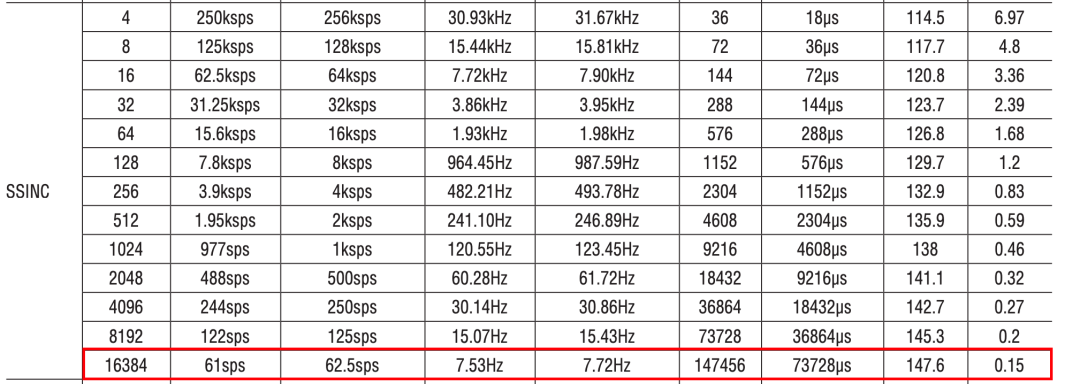

SSINC, DF = 16384(极限高动态范围)

表 2 中 ssinc, DF=16384:

输出速率:约 61 sps

动态范围:≈ 147.6 dB

Noise ≈ 0.15 µV RMS

于是:

这已经对应了 148 dB 左右的动态范围,非常接近“地壳地震仪那一类”的水平。

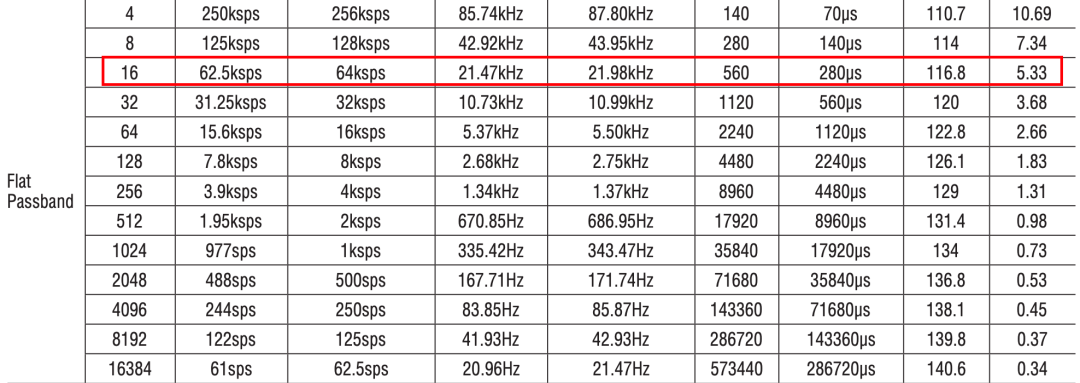

Flat-Passband, DF = 16(需要平坦通带 + 中等带宽)

Flat-Passband, DF=16 行:

输出速率:≈ 62.5 ksps

3 dB 带宽:≈ 21.5 kHz

动态范围:≈ 116.8 dB

Noise ≈ 5.33 µV RMS

噪声就是 5.33 µV RMS,以后在你的系统里当成一项固定噪声源。

如果 VREF 不是 5 V 怎么办?

所有这些动态范围和噪声值,是在 VREF=5 V 下测出来的。因为 ADC 的满量程是 ±VREF,噪声基本正比于 VREF。

所以如果用别的 VREF,可以简单线性缩放:

实际实际

举例:

ssinc, DF=16384, VREF=2.5 V

datasheet 噪声(5V):0.15 µV

实际噪声 ≈ 0.15 µV × (2.5/5) ≈ 0.075 µV RMS

想精细一点:换算成 LSB / 噪声密度

换算成 LSB 数

LTC2500 的 SAR 内核是 32bit,满量程 ±VREF,对应 2³² 个码:

满量程差分电压:FSR = 2·VREF

1 LSB 大小:

以 VREF=5 V 为例:

如果你 ssinc, DF=16384,噪声 ≈ 0.15 µV:

也就是说,虽然是“32 bit ADC”,在这个配置下有效噪声大概是 约 26 bit 有效位 的量级(对应 ~148 dB 动态范围),这和 datasheet 的 DR 对得上。

(在做系统分辨率估算时,用有效位数而不是名义 32bit 会更真实。)

从无延时输出(SDOB)推噪声密度(如果要宽带波形)

对于 SDOB,那条路 datasheet 给的是:SNR ≈ 104 dB(±5 V、2 kHz 正弦、fs=1 Msps)

先求满量程差分的 RMS 电压:

对 VREF=5 V,有:

由 SNR 定噪声:

代入 104 dB:

若假设噪声在 0~fs/2=0~500 kHz 近似白噪声,则噪声密度约:

取等效噪声带宽 B≈500 kHz,则

几十

然后你可以按需要自己在某个带宽内重新积分(做你自己的数字滤波),这就适合你用 FFT + 自己设计的窗函数时的噪声估算;但如果是用芯片自带数字滤波,那就没必要这么绕:直接用 Table 2 的 RMS 噪声就行。

把 ADC 噪声塞进你的整体噪声预算

假设有:

传感器 :输出灵敏度 [V/物理量]

前端放大器:增益 ,自身输入噪声 [V/√Hz],带宽

ADC:等效输入噪声 (由上面 Table 2 得到)

参考源:等效噪声 (LTC6655 有 datasheet 噪声曲线)

则 ADC 输入端合成噪声(RMS) 近似为:

然后:

换算成等效物理量噪声:

得出最小可分辨量 / 噪声地板。

使用滤波器这路

如果你 VREF 降到 2.5 V(更贴近 1.15–1.25 V 区间)

LTC2500 支持 VREF 2.5–5.1 V ,满量程 ±VREF。噪声基本按 VREF 线性缩放:

实际实际

例如仍用 SINC4, DF=16384:

VREF = 5 V:噪声 0.19 µV RMS

VREF = 2.5 V:噪声 ≈ 0.19 × 0.5 ≈ 0.095 µV RMS

要测的 jitter 是 40 µV,量级对比:

被测信号抖动:40 µV

LTC2500+SDOA 自己的噪声:0.095 µV

测量链路比信号本身 “安静” 了 400 倍,完全不会淹没你要看的抖动。

把 LTC2500 SDOA 放回你的信号链噪声预算里

之前我们建过一条“基准测量”噪声模型:

基准自身 0.1–10 Hz 噪声:假设 ~15 µV RMS

运放白噪声 & 1/f:~1 µV 以内

电阻热噪声:0.0x µV

ADC 噪声:之前假设 ~2 µV,只是为了举例

总噪声:RSS 合成 ≈ 15.2 µV RMS(几乎全是基准自己)

现在换成 真实 LTC2500+SDOA:

选 SINC4, DF=16384,VREF=2.5 V:ADC 噪声 ≈ 0.095 µV RMS(可以粗略当 0.1 µV)

其余假设不变:

也就是说:

就算你把运放、电阻的噪声也算上,整条链路还是被基准源噪声主导;LTC2500 SDOA 的噪声几乎可以视作 0。

“测量系统噪声 floor” ≈ 15 µV RMS,基准抖动目标(比如 40 µV RMS)> 测量噪声 ≈ 2.5×;想要“测 1.20000 V,看 10 µV 级别变化”,完全没问题。

LTC2500 SDOA 在任何合理滤波配置下(DF ≥ 64),都远优于 10 µV;甚至在高带宽(kHz 级)时,噪声也只是 2–5 µV 量级。

对1.2 V 基准、40 µV 抖动分析来说真正需要关心的是:基准本身的低频噪声(参考器件的选型,比如 LTC6655 系列);前端运放的 1/f 噪声;LTC2500+SDOA 自己的噪声基本可以忽略不计,不会限制你对 40 µV 抖动的观察能力。

一个新方案

评论区的一位老哥的

评论区的一位老哥的

这种方案直观的看,是降低了 ADC 的压力,但是信号链就在这个链上面,任何一个地方的噪音都影响最终结果。

思路回顾:前置差分放大,放大 10~50 倍

结构大概是:

基准源(≈1.2 V)→ 用 1.20000 V 精密参考做差,得到一个“微小差分” Δ → 低噪声仪表放大器,增益 G = 10~50 → 普通 24-bit ΔΣ ADC(比如噪声几 µV 级)

这样做的核心目的就是:

把关心的小变化(比如 40 µV 抖动)

在 ADC 端变成:G·40 µV = 400~2000 µV;于是 ADC 自身噪声可以放宽一个量级,而整体输入参考噪声仍然很小。

用数字证明:前级放大后,普通 24-bit ADC 确实“很够用”

用一个简单的噪声预算模型算了一下(带宽 0~10 Hz):

参考自身低频噪声:≈ 15 µV_rms(假设)

放大器输入白噪声密度:5 nV/√Hz(比较优秀的精密运放)

在 10 Hz 内白噪声 ≈ 0.016 µV_rms

再假设 1/f 噪声 ≈ 1 µV_rms(典型量级)

ADC:在其输入端噪声 ≈ 5 µV_rms(一颗不算极限的 24-bit ΔΣ)

考虑三种增益:

G = 10

G = 20

G = 50

把 ADC 噪声折算回输入端:

然后做 RSS 合成:

Direct LTC2500 SDOA example:

Total noise ≈ 15.03 µV_rms (dominated by reference itself)

Generic 24-bit ADC + low-noise gain stage:

G = 10: total ≈ 15.04 µV_rms, amp white ≈ 0.02 µV_rms, ADC noise@input ≈ 0.50 µV_rms

G = 20: total ≈ 15.04 µV_rms, amp white ≈ 0.02 µV_rms, ADC noise@input ≈ 0.25 µV_rms

G = 50: total ≈ 15.03 µV_rms, amp white ≈ 0.02 µV_rms, ADC noise@input ≈ 0.10 µV_rms

不管 G=10/20/50,总噪声都在 15.0x µV_rms,也就是说:仍然被参考自身噪声主导,放大器白噪声、ADC 噪声都被压到“只有小数 µV”的级别。

这正好印证了说的:

放大 10~50 倍以后,ADC 的噪声指标可以放宽一大截,几乎任何像样的 24-bit ΔΣ ADC 都可以胜任。

从系统层面看:这条路在理论上完全站得住。

难点确实转移到了“低噪声仪表放大器”上

你也说了:“但低噪声的放大难度也挺高”。确实,主要难在:

1/f 噪声和 0.1~10 Hz 噪声

白噪声用 5~10 nV/√Hz 的运放很容易做到,真正麻烦的是 0.1~10 Hz 的 1/f 噪声。很多运放在这段频带里给的是:0.1–10 Hz 噪声 ≈ 几 µV_pp,等效 RMS 也会到 1 µV 甚至更高。

在 G=50 这种高增益下,如果你前级 0.1–10 Hz 噪声=3 µV_rms,那折算到传感器侧还是 3 µV,但会直接叠到你的参考噪声上。

高增益下的电阻噪声 + CMRR 降低

仪表放大一般用电阻网络设定增益:高值电阻 → 热噪声(4kTRB)会显著贡献;匹配不佳 → CMRR 降低,1.2 V 共模上的波动 / 数字干扰容易漏进差模。对于 1.2 V 这种“直流基准”,任何电源纹波、地弹噪、热漂都可能通过有限 CMRR 混入差分结果。

零点漂移和温漂

要做的是 “测几个十 µV 的变化”,如果放大器的输入失调是几十 µV、随温度漂 0.1 µV/°C,在长时间观测时会很烦人:需要定期归零 / 校准。

常要用零漂运放(auto-zero / chopper) 或 高端仪表放大器,但这类器件在低频下会有 chopper 残留、折叠噪声,需要额外滤波。

两种架构的对比

方案 1:直接上 LTC2500 + SDOA(或同级别高端 ADC)

模拟前端可以很简单(甚至不需要高增益,只做缓冲/滤波);噪声主要由参考源自身决定,ADC 远远不是瓶颈;数字滤波、OSR 都内建,设计难度集中在 PCB + 参考 + 供电。

缺点:器件贵(都玩这个了,还怕贵?)

方案 2:低噪声 INA + 普通 24-bit ΔΣ ADC

ADC 可以选比较便宜、常见的 24-bit 器件,数字接口简单;通过 G=10~50 放大,把 ADC 噪声压回输入端,要求降低一个量级。

缺点非常明显:低噪声、高 CMRR 的模拟仪表放大难度实打实;1/f 噪声、温漂、石英电阻噪声、共模干扰、供电噪声耦合……调 PCB 布局、接地、屏蔽都要非常小心。

这两条路的难度是“换位”的:要么花钱 + 用好 ADC,减轻前端模拟难度;要么用普通 ADC + 辛苦做一颗极干净的前端。

通过搭建低噪声仪表放大,将 1.2 V 基准与 1.2 V 参考做差后,放大 10~50 倍再送入 ADC,可以显著放宽 ADC 的噪声指标要求,使得多数 24-bit 精密 ADC 就能满足输入端 10 µV 级别的测量需求。但与此同时,对前端放大器的噪声(尤其是 0.1~10 Hz 1/f 噪声)、失调漂移及 CMRR 提出了较高要求,使得模拟设计和 PCB 实现的难度相应上升。

新的前放选择

OK,上面的问题很明白了,也和我们的常识认知一样,第一级的噪音对系统的影响至关重要。

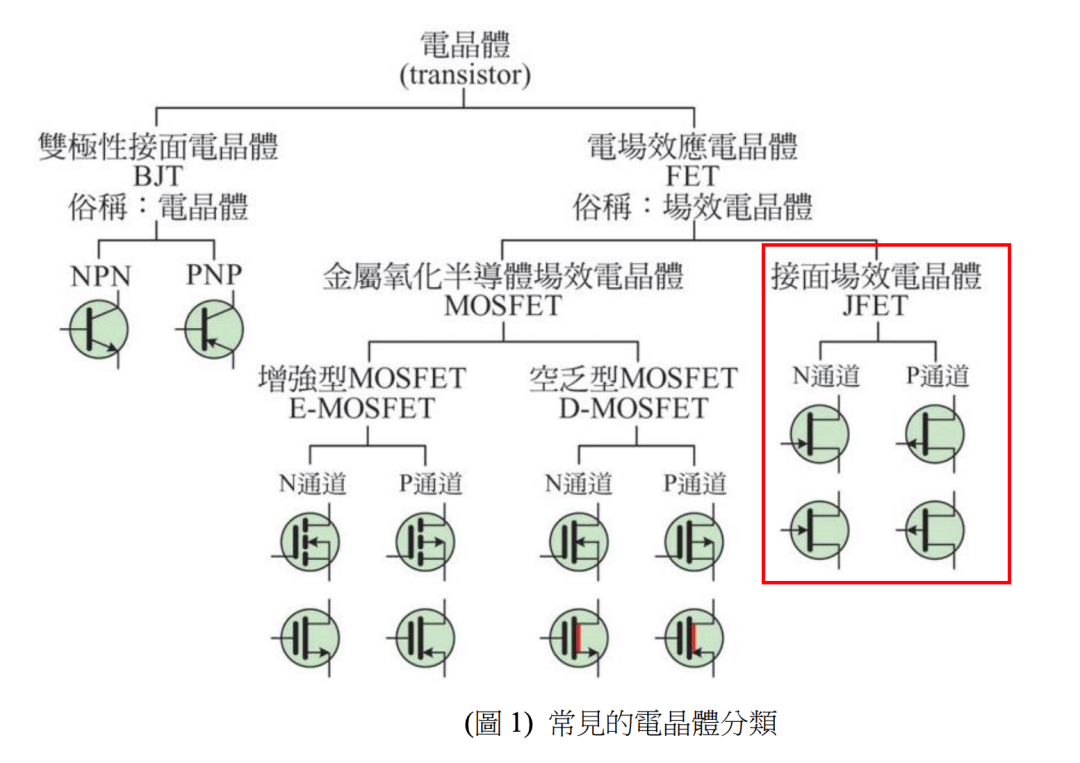

这是半导体世界的子民

这是半导体世界的子民

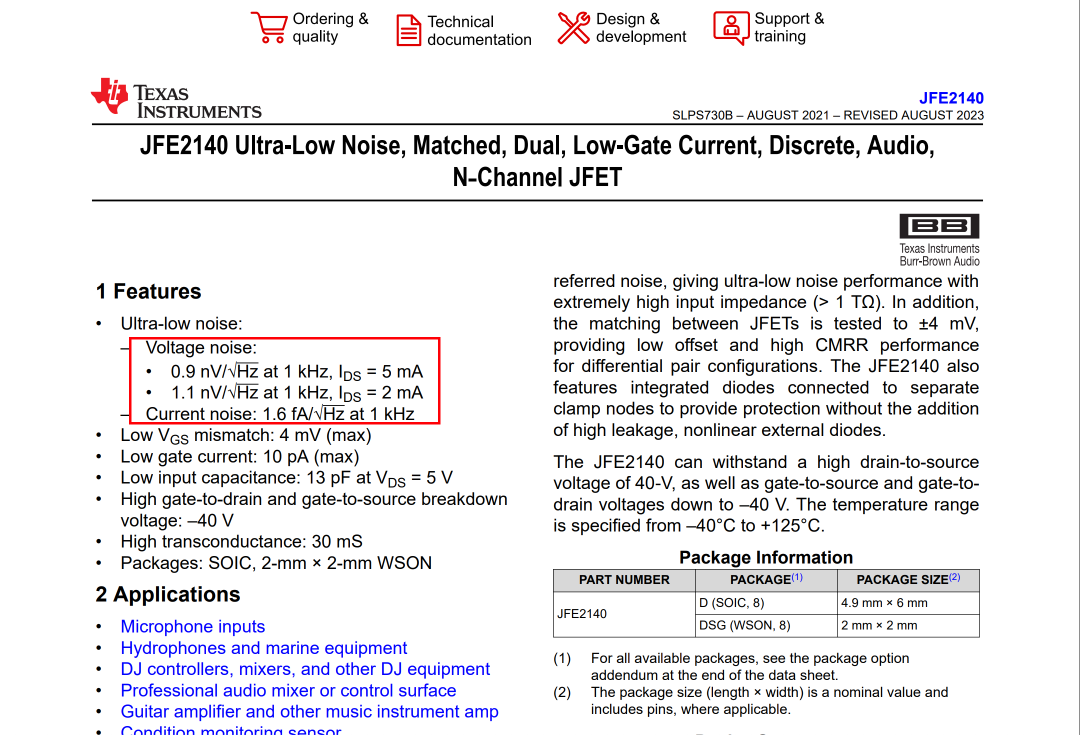

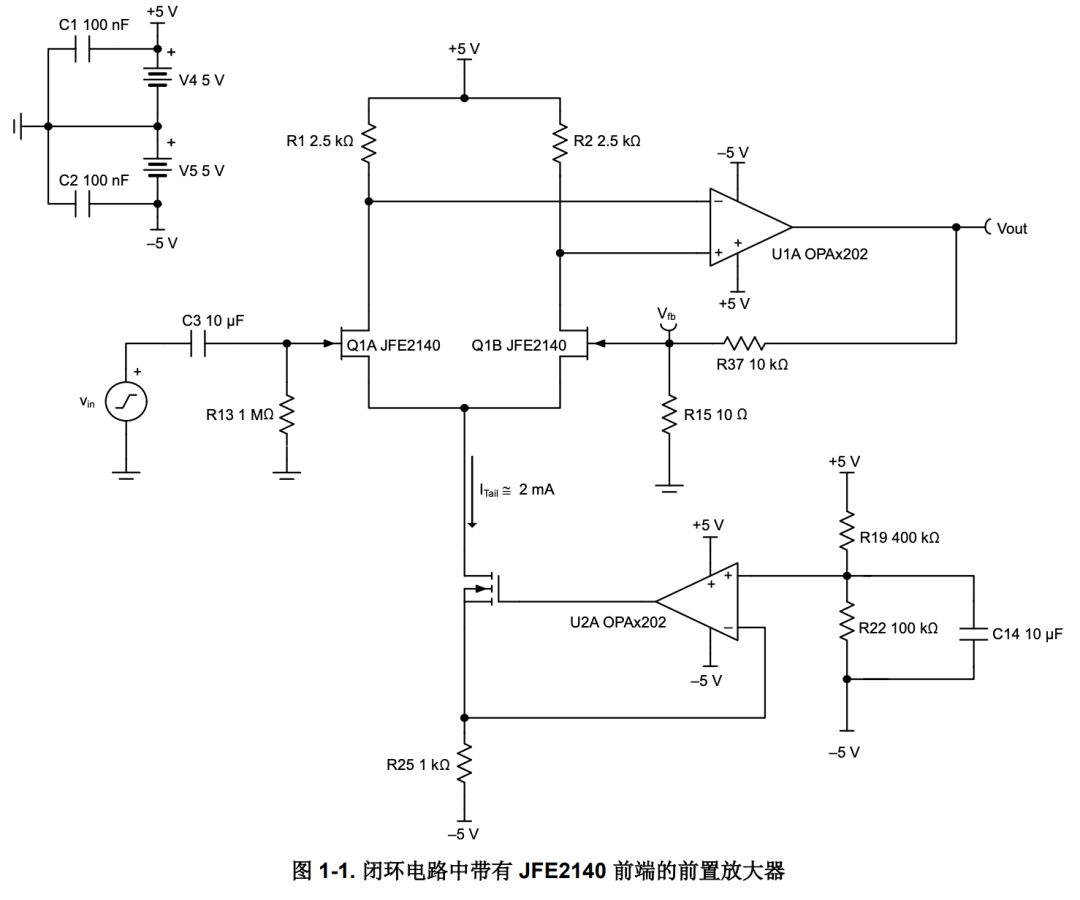

我找了一个 TI 的器件

我找了一个 TI 的器件

大概长这样

大概长这样

那我们就按照:

里面给的这个参数来讨论

里面给的这个参数来讨论

用低噪声 JFET 做前放是一个很“老派但优雅”的路线,而且读者给的这个噪声水平其实非常狠。

我先把数字算一下,再说说它对整体链路的意义和难点。

100.0 nVpp -> ~ 15.15 nVrms

300.0 nVpp -> ~ 45.45 nVrms

G=10: JFET noise at ADC input ~ 454.55 nVrms (= 0.4545 µVrms), fraction of 10 µV target ≈ 4.545%

G=20: JFET noise at ADC input ~ 909.09 nVrms (= 0.9091 µVrms), fraction of 10 µV target ≈ 9.091%

G=50: JFET noise at ADC input ~2272.73 nVrms (= 2.2727 µVrms), fraction of 10 µV target ≈ 22.727%

读者说:

低频噪声可以控制在 100–300 nVpp

假设这是 0.1–10 Hz 范围内的峰峰值噪声,且峰峰值大概对应 ±3.3σ(即总 6.6σ 区间),那么:

100 nVpp → ≈ 15 nVrms

300 nVpp → ≈ 45 nVrms 这是在 JFET 输入端的低频噪声。

加上前置增益之后,送到 ADC 端有多少?

假设用这个 JFET 前放做差分放大,增益 G=10, 20, 50:

(用 worst case 300 nVpp → 45.45 nVrms 来算)

300.0 nVpp -> ~ 45.45 nVrms

G=10: JFET noise at ADC input ~ 454.55 nVrms (= 0.4545 µVrms),

≈ 4.5% of 10 µV target

G=20: JFET noise at ADC input ~ 909.09 nVrms (= 0.9091 µVrms),

≈ 9.1% of 10 µV target

G=50: JFET noise at ADC input ~2272.73 nVrms (= 2.2727 µVrms),

≈ 22.7% of 10 µV target

就算在 最坏的 300 nVpp 情况,

G=10 → 对应 ADC 端只有 ~0.45 µVrms

G=20 → ~0.9 µVrms

G=50 → ~2.3 µVrms

相对于你整条链路希望的 10 µVrms 量级来说:

JFET 前放噪声只占 5–20% 左右,非常可控。

而且这还是在参考本身 15 µVrms(示例) 的情况下,整体仍然是基准自身噪声主导,而不是前放或 ADC。

优点:把 ADC 的压力完全卸掉了

用这么干净的 JFET 前放 + G=10~50,可以做到:在 ADC 端,感兴趣的抖动(比如 40 µV)被放大到 400–2000 µV 级别;ADC 自己哪怕有 几 µVrms 噪声,都可以被 /G 折回输入端,变成 几百 nV 级, 完全被参考噪声淹没。

这就印证了你说的:

“可以把对 ADC 的指标要求降低一个量级,随便一款 24 bit 精密 ADC 都够用。”

理论上确实这样,而且地板非常低。

难点:JFET 这条路为什么“听起来美好,做起来要命”

读者给的这个 100–300 nVpp(0.1–10 Hz)指标,其实已经比很多精密运放还厉害:

常见低噪声运放 0.1–10 Hz 噪声:一般是 几 µVpp,你这边是 0.1–0.3 µVpp,直接低了一数量级。

这意味着你在设计上要非常注意:

比如JFET 本身选型 + 偏置点;噪声最优 Id 区间;Vds、温度点、gm 的折中,还有测 1.2 V / 几十 µV 的差分时,任何几 pA 的漏电 + 兆欧量级电阻都会造成 µV 级误差;另外JFET 的高输入阻抗会“看见”一切地线波动、屏蔽弱点;在 µV 以下玩,焊点热电势、铜/锡/镍的 Seebeck 系数都会被放大出来。

换句话说,你确实把“ADC 的难度”换成了“自己做一颗半定制的低噪前端放大器”。

通过使用低噪声 JFET 管组成的前级差分放大器,在 0.1–10 Hz 频带内将输入等效噪声控制在约 100–300 nVpp(对应 15–45 nVrms),再将 1.2 V 基准与精密 1.2 V 参考的差分信号放大 10–50 倍送入 ADC,可以使前放引入的噪声在 ADC 端仅为 0.5–2.3 µVrms,占整体 10 µV 级别噪声预算的 5–20%。在这种架构下,对 ADC 的自身噪声与分辨率要求被显著放宽,多数 24-bit 精密 ΔΣ ADC 即可满足要求,而系统的主要限制因素转而变为 JFET 前端的低频噪声控制、失调与温漂、以及 PCB 上的漏电与热电势管理。

后记

感谢读者提供的选题,感谢大家的阅读观看;在现代电子设计里面,其实遇到的问题和之前的前辈们遇到的一样;各种半导体公司的东西浩如烟海,我们没有必要再手工搭建,性价比不高,而且新技术一定会碾压旧技术;就一句话,有集成方案就不选分立的。更重要的是,通过几种方案其实更加的明显的验证了:复杂性没有消失,只是在转移。

但是他们依旧生命力旺盛

但是他们依旧生命力旺盛

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-11-19,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录