为TMR 线性磁场传感器设计采集信号链

群友问了一个问题,要有效位 21bit,采样率 10M 的 ADC,给我搞懵逼了,这是什么信号?这么牲口的要求?

完全搞不懂要干嘛

先看看大概可以满足要求的 ADC 有哪些?(根本没有)

最精密,但是采样率不够

最精密,但是采样率不够

这个是最接近要求的 ADC

这个是最接近要求的 ADC

但是我还是迷惑,采集什么啊?

谜底揭晓

谜底揭晓

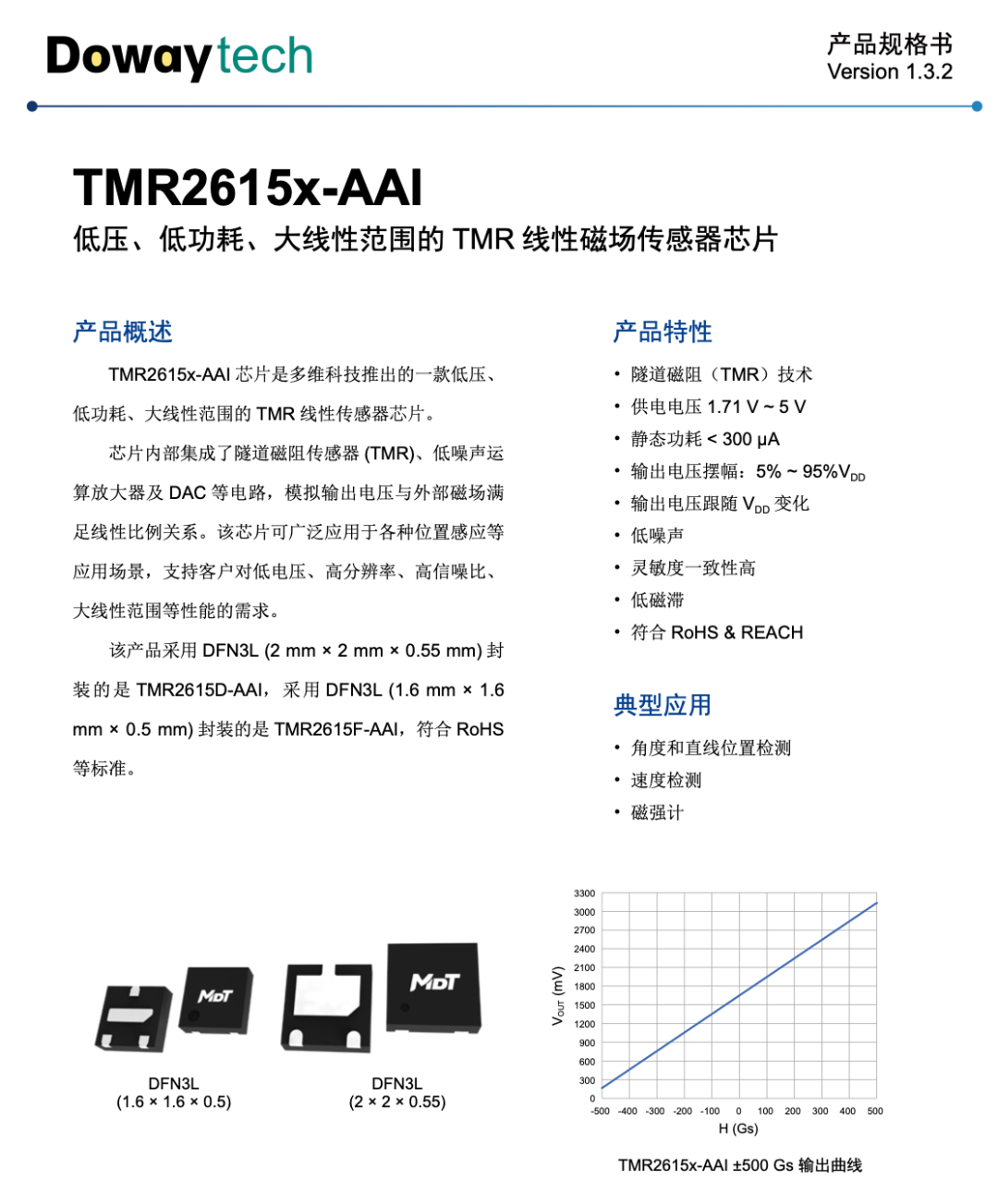

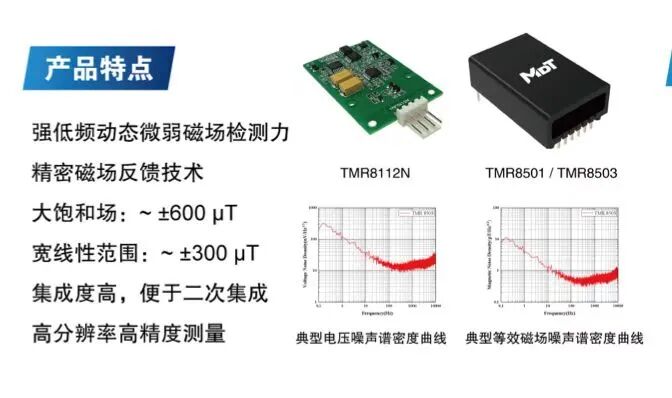

原来是多维科技的后端采集器:

就是这颗芯片了

就是这颗芯片了

传感器解读

大概如此

大概如此

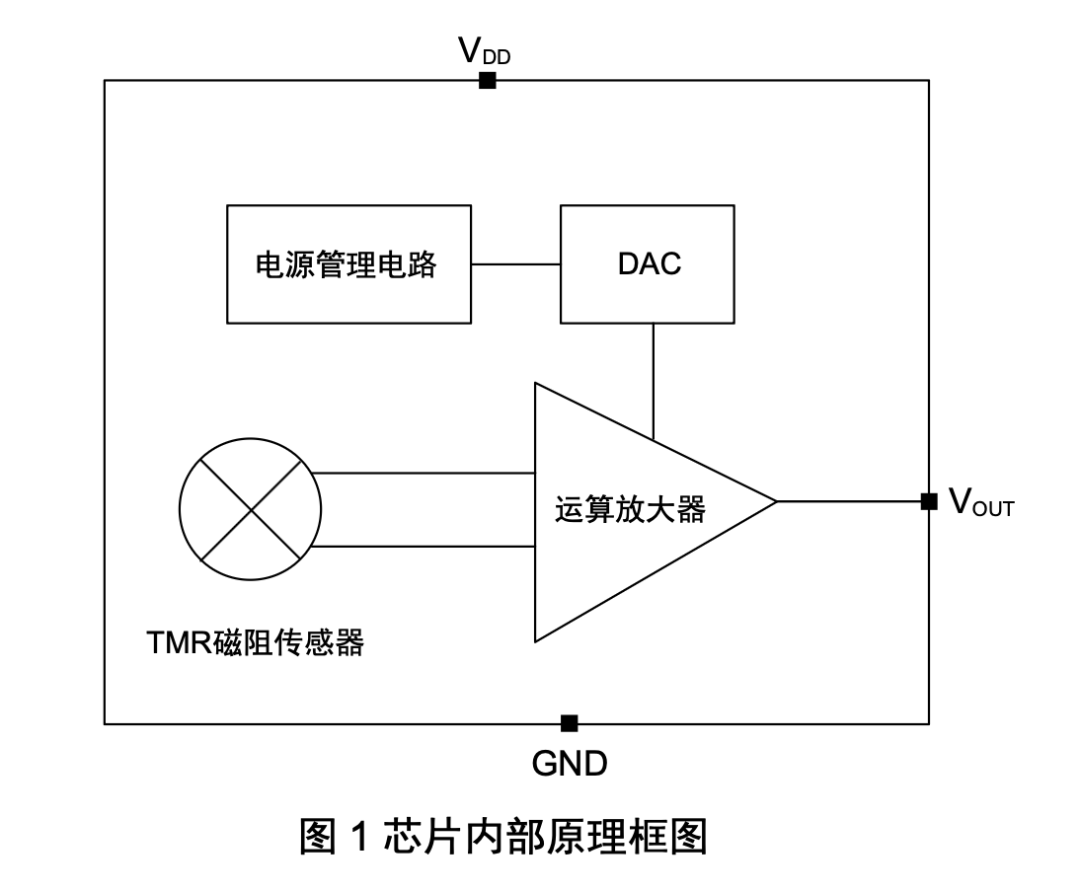

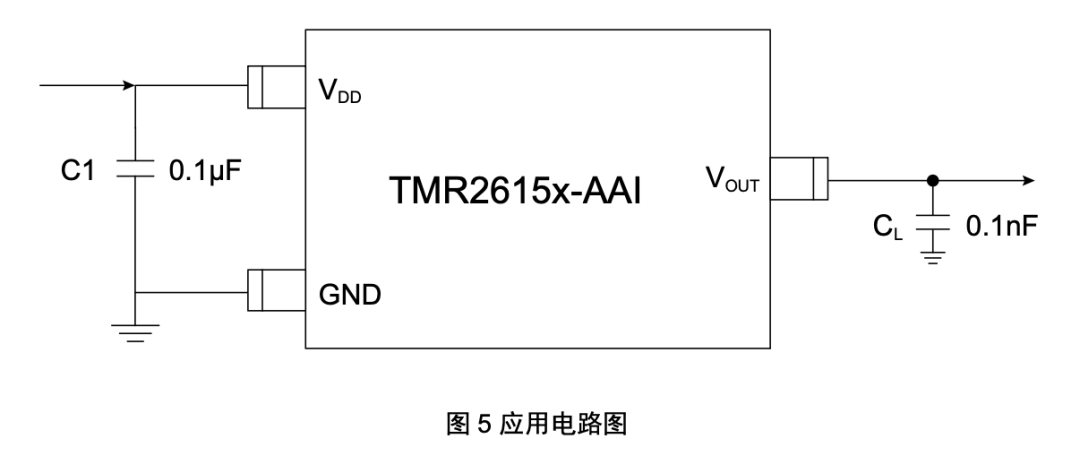

TMR 磁阻桥 + 低噪声运放 + 片上 DAC + 供电/偏置管理,三引脚模拟电压输出(VOUT、VDD、GND);看图这是一个内置前端与缓冲放大的“类运放输出”TMR线性磁场传感器;其中零磁场输出在 VDD 的 50%,输出对 VDD 比例缩放(ratiometric)。

image-20251101173638233

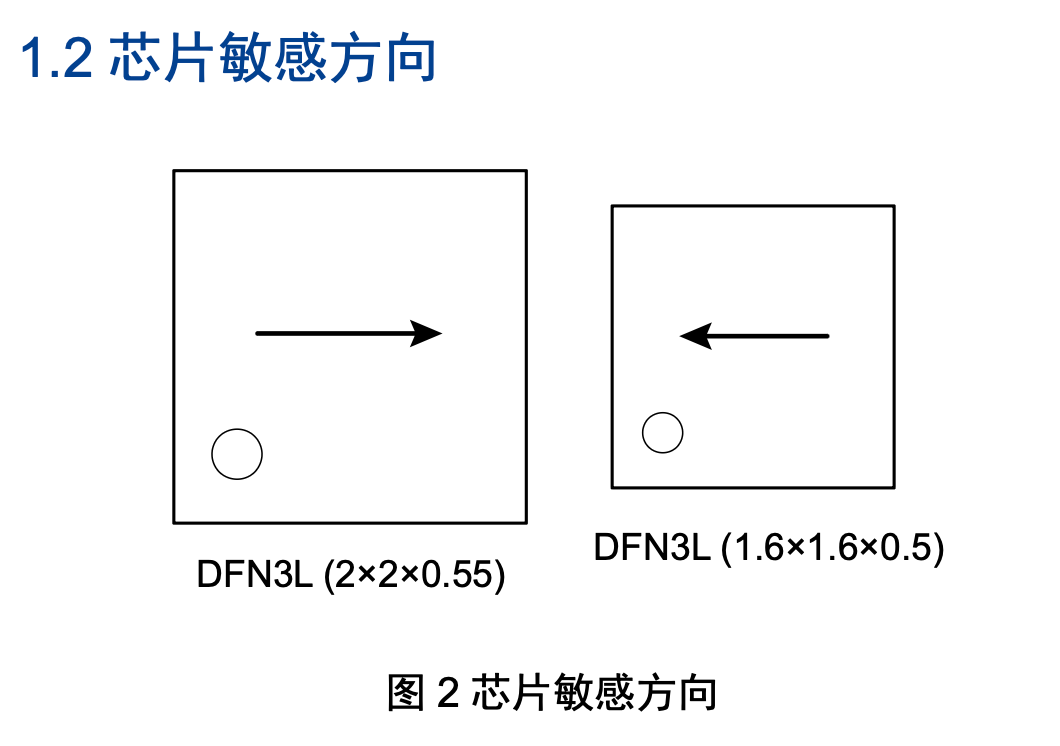

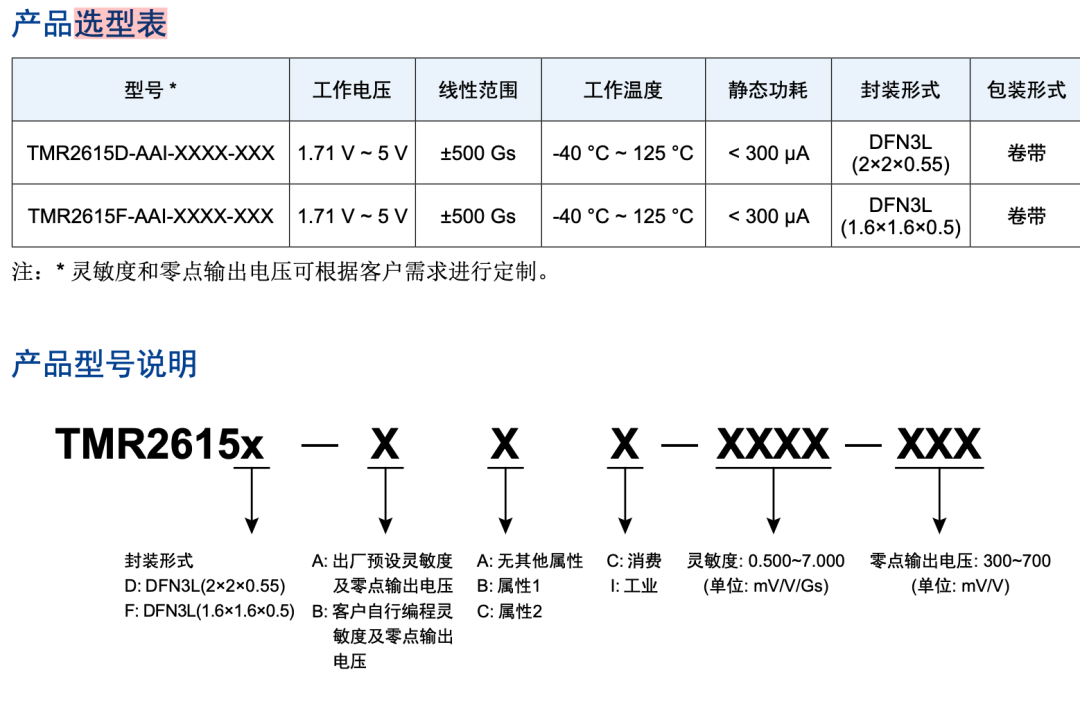

封装顶面标注了 TMR 敏感方向;两种 DFN3L 封装(2×2×0.55 mm 与 1.6×1.6×0.5 mm),引脚同为 3 脚:VOUT、VDD、GND。

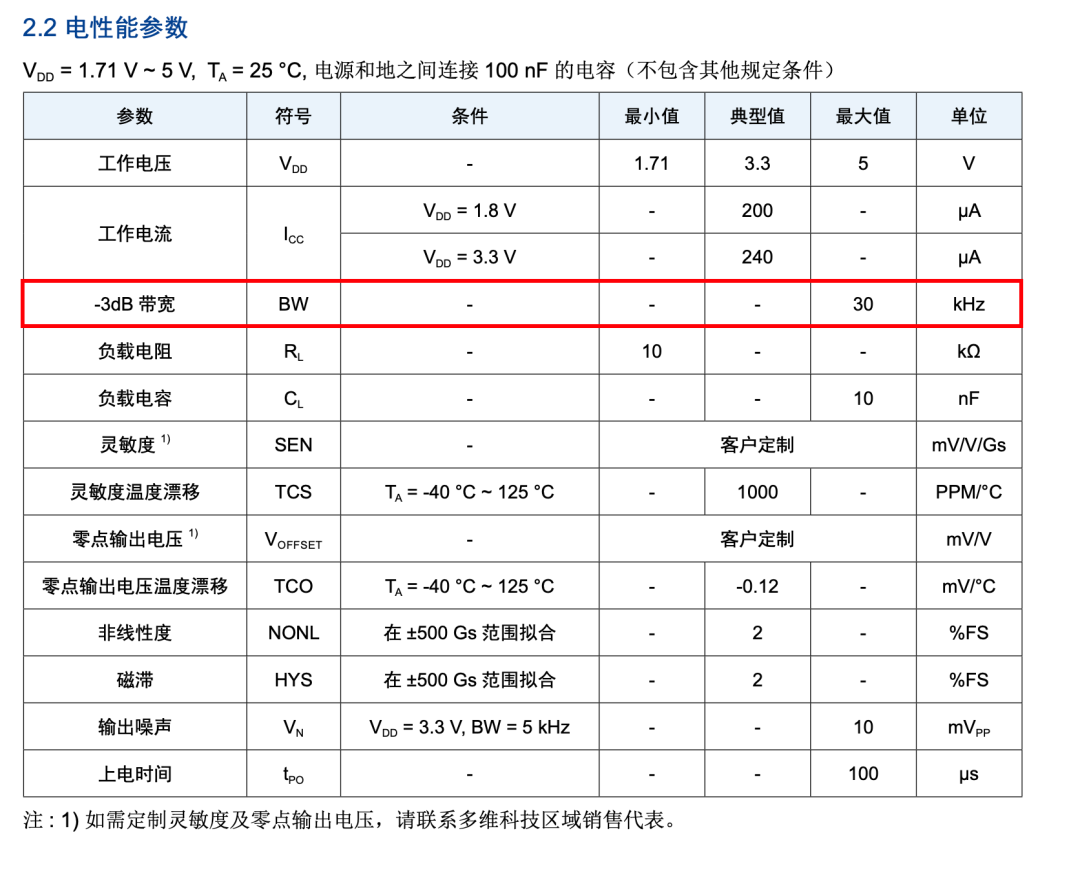

关键电气/磁特性

供电:1.71–5 V;静态电流典型 200 µA@1.8 V、240 µA@3.3 V(超低功耗);其中输出摆幅 5%–95%·VDD,零场 ≈50%·VDD。

输出可驱动 1.5 mA,建议 RL≥10 kΩ,CL≤10 nF;上电到稳定 <100 µs。ESD(HBM) 4 kV。

电信号

电信号

−3 dB ≈ 30 kHz(典型),等效一阶时间常数 τ≈1/(2π·30 k)≈5.3 µs,对速度检测/闭环控制很友好。

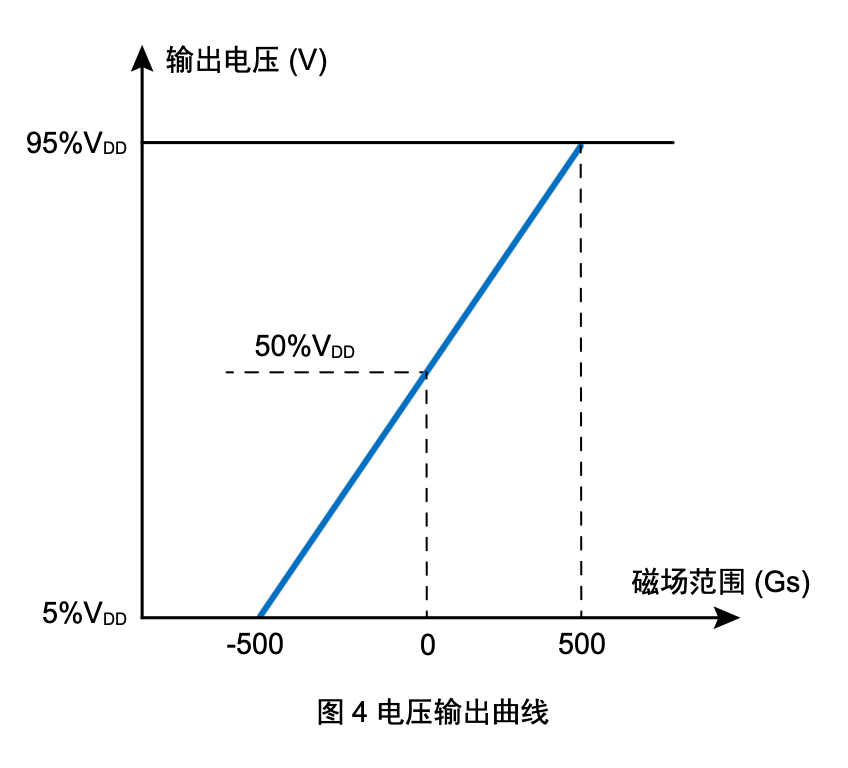

线性与磁参数:标称 线性范围 ±500 Gs(±50 mT),非线性度 ≤ 2%FS,磁滞 ≤ 2%FS;典型曲线显示 −500→+500 Gs 时 VOUT 从 5%VDD 线性到 95%VDD。

非常的线性

非常的线性

灵敏度/零点可定制:SEN=0.500–7.000 mV/V/Gs,零点 VOFFSET=300–700 mV/V(即 0.3–0.7·VDD)。温漂:TCS≈1000 ppm/°C,零点温漂 TCO≈−0.12 mV/°C(按 mV/V 标称)。某些料号为“出厂预设”,也提供“客户可编程灵敏度与零点”的变体(料号位 B),但文档未公开编程接口细节,需联系厂家。

输出噪声

输出噪声

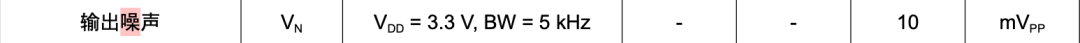

VDD=3.3 V,BW=5 kHz 时 Vn ≤10 mVpp(最大值);该 pp 指标与 RMS/谱密度并非一一对应,若粗略按高斯 6.6σ 估计,10 mVpp≈1.5 mVrms,等效白噪声密度 (仅供量级参考,精确值以厂家更详细噪声谱为准)。

应用电路,信号链视角

非常简单,供电,输出

非常简单,供电,输出

VDD 与 GND 间放 0.1 µF 贴片去耦(尽量靠近引脚);负载电容 ≤10 nF。文档示例即为 3 引脚直接出模拟电压;与 ADC 配合的时候建议做“比例式(ratiometric)”采样:把 ADC 参考 VREF = VDD(或同源 LDO 经缓冲),因 VOUT 按 VDD 比例缩放,可自动抵消供电波动带来的增益误差。

带宽与抗混叠:器件本体 BW≈30 kHz。如果下游 ADC 采样率 不足以把 30 kHz 完整采样,需在 VOUT 端加 RC 低通(Rout‖RL 与 CL 形成极点,注意 CL≤10 nF限制;必要时加前级缓冲运放+外部 RC)。

计算选型

目标抗混叠带宽 5 kHz,可选 、(单端驱 外置缓冲 时),;若直接在 VOUT 上并 C,需保证 且 ADC 采样保持电容充放电误差满足指标;器件最大 1.5 mA 驱动,但官方推荐 RL≥10 kΩ、CL≤10 nF。

如果 ADC 的 SH 电容较大或采样窗口很短,应加电压跟随器(低噪声、轨到轨输入输出、CMRR 高、带宽≥1 MHz 的运放)防止抽样瞬间压降/畸变。

VOUT 在零场≈0.5·VDD,摆幅到 5%–95%·VDD。若系统希望单极性 ADC(0–VREF)满量程利用率高,可在 MCU 侧做两点标定把 5%–95% 映射到 0–FS;或硬件上用差动放大/偏置搬移到 0–VREF。

灵敏度、量程与磁路配对

典型曲线给出:±500 Gs → VOUT 从 5%VDD 到 95%VDD,即总摆幅 0.9·VDD;换算平均斜率约

因此若供电 3.3 V,对应灵敏度约 时能覆盖 ±500 Gs 而不饱和。

若选到 更高灵敏度(例如 5–7 mV/V/Gs),则满量程磁场会大幅缩小(很适合近距离弱磁/小位移测量);这与“选型表可定制 0.5–7.0 mV/V/Gs”的说明是一致的:线性区与灵敏度是一对权衡。

这里

这里

磁体/气隙快速预估:1 Gs ≈ 0.1 mT。如果使用 N35 钕铁硼棒磁在 2–4 mm 距离常有 5–30 mT(50–300 Gs)量级的可用磁场;结合上面灵敏度换算即可倒推可用行程与ADC 分辨率是否满足需求。

分辨率估算

以 VDD=3.3 V,S=1.0 mV/V/Gs → 3.3 mV/Gs。配合 12-bit ADC(VREF=3.3 V)分辨率约 0.8 mV/LSB,对应磁分辨率 。若按前述噪声粗估(~μV/√Hz 量级),并在 1 kHz 带宽内低通,磁分辨率还能改善到亚高斯级(需实测噪声谱/平均时间常数来精算)。

对于非线性/磁滞的要求来说:典型 ≤2%FS。对高精度直线位移,可在出厂时做多点场-电压标定表(如每 50 Gs 采一点),在 MCU 里 LUT + 线性插值;磁滞可通过单一磁极工作、稳定磁路、避开矫顽力低的磁材来减小。

封装/装配与布局要点

这种传感器对安装非常的敏感,一定要好好的校准。封装为:DFN3L(2×2×0.55 mm) 与 DFN3L(1.6×1.6×0.5 mm),顶面为感应面;底部有传感区域示意。

注意引脚1标记与敏感轴方向一致安装,保证磁场矢量与标称方向对齐;传感器到磁体的机械公差、倾角、距离是误差主因;优先做机械重复性与温漂路径控制。

PCB 上就近 0.1 µF 去耦,敏感节点(VOUT)避免长走线与强场导线并行;必要时加地参考铜皮+过孔栅栏隔离电机相线/开关电源回路。

详细采集方案

默认 VDD=3.3 V、TMR2615x 模拟输出:零场≈0.5·VDD、线性区约 5%–95%·VDD,器件本体带宽≈30 kHz,输出驱动≤1.5 mA,建议负载 R_L ≥10 kΩ、C_L ≤10 nF。

方案 A|最低功耗直连 + 轻量抗混叠(单端 SAR,ratiometric)

传感器直接推小电容 + 小串阻形成一阶 RC 抗混叠;ADC 用 VREF=VDD 做比例式采样,自动抵消供电波动对增益的影响;若 ADC 采样电容较小/采样窗较宽,可不加缓冲。

[TMR2615x VOUT] -- R_S (100–300 Ω) --+---> SAR ADC IN+ (VREF = VDD)

|

C_S (≤10 nF to GND)

GND ----------------------------------+---> SAR ADC GND

VDD -------------------- decouple --->+---> SAR ADC VREF (=VDD)

选 作为抗混叠极点。无外缓冲且受限于 C_L≤10 nF,若希望 可取 R_S≈330 Ω、C_S≈10 nF → f_c≈48 kHz。

与 SAR 采样保持(S/H)兼容性:若 ADC 采样电容 和采样窗 已知,源等效电阻 须满足

时

例如 → ;如果ADC 仅 100 ns,,R_S 取 100–200 Ω 更稳妥;在 ADC 上面找低功耗 12–16 bit、≥250 kS/s 的单端 SAR(带外部 VREF 引脚)。

方案 B|缓冲放大 + 二阶抗混叠(单端 SAR,ratiometric)

在 VOUT 后加 低噪声、RRIO 零漂/低失真运放作电压跟随或微增益,允许更大的外接电容做二阶 LPF;ADC 仍用 VREF=VDD。

VDD ── LDO ──┬─ decouple ──> [VREF of SAR] (ratiometric)

│

TMR VOUT ─→ [RRIO OpAmp BUF] ── R1 ──+── R2 ──> SAR IN+

│

C1

│

GND

GND ──────────────────────────────────┴────────> SAR GND

运放选择零漂/低噪声、RRO/RRI、GBW ≥ 1–3 MHz、输出能稳定驱动 C_LOAD ≥ 47–100 nF(或在 R1 前做隔离);比如OPA333/OPA320、AD8628/OPA350、ADA4505/ADA4528 等(按功耗/带宽取舍)。

选 Bessel 或多重反馈(MFB)二阶以获得平滑相位;目标 典型取 (若 ,);给一个参数R1=330 Ω,C1=33 nF → f_c≈14.6 kHz,再配合运放内部补偿或二阶网络设到 30–50 kHz;因为有缓冲后 近似为 R1(几十~几百欧),易满足 16 bit 的建立时间。

方案 C|单端→差分转换 + 差分 SAR/ΣΔ(高动态/高带宽)

TMR 单端先用低漂 BUF 定义源阻,再用低噪声全差分放大器(FDA)做 SE→Diff,设定差分增益与VOCM=VREF/2,在差分端做对称 RC 抗混叠,驱动差分 SAR 或中高速 ΣΔ(AD400x/ADS886x/AD7768-1/ADS127Lxx 等类目)。

TMR VOUT → [RRIO BUF] → [FDA (gain≈1, VOCM = VREF/2)]

┌─ Rf ──+─ C_f ─→ ADC IN+

VREF/2 ─────┤ │

└─ Rg ──┴─ C_g ─→ ADC IN−

VDD ── LDO ──> VREF (also to FDA VOCM pin) GND

运放选选择THS4551 / ADA4940-1 / ADA4945-1 / OPA1632(按带宽功耗取舍)这些;然后差分也是需要抗混叠,每支路用 R_d(10–49.9 Ω) + C_d(330 pF–2.2 nF) 形成成对极点;再配合 FDA 内部补偿/二阶拓扑获得所需带宽。

将 TMR 的 5%–95%·VDD(约 0.165–3.135 V@3.3 V)经 BUF→FDA 变换到 差分±(0.45·VREF) 左右并居中于 VOCM=VREF/2。

电源供电建议

因为输出和电压有着强相关,所以用同一个 LDO 供 TMR 的 VDD 与 ADC 的 VREF;或把 VDD 先经低漂缓冲后送 VREF。好处是VDD 漂移 → VOUT 与 VREF 同比变化,增益误差自抵消,只剩传感器灵敏度温漂与运放/ADC漂移。

传感器本体 −3 dB≈30 kHz;如果 ADC 采样率 仅 100–200 kS/s,必须在外部把 限到 左右;若要测更窄带(例如 5–10 kHz),外部 RC/MFB 先限带,既降噪又放宽 SAR 建立时间约束。

S/H 建立时间(16 bit )

、、 → ;直连(方案 A)时把 R_S 控制在 100–330 Ω,并确认 ≤10 nF;带缓冲(方案 B/C)时由运放承担快速充放电。(因为电容不好选择,可以先确定电容)

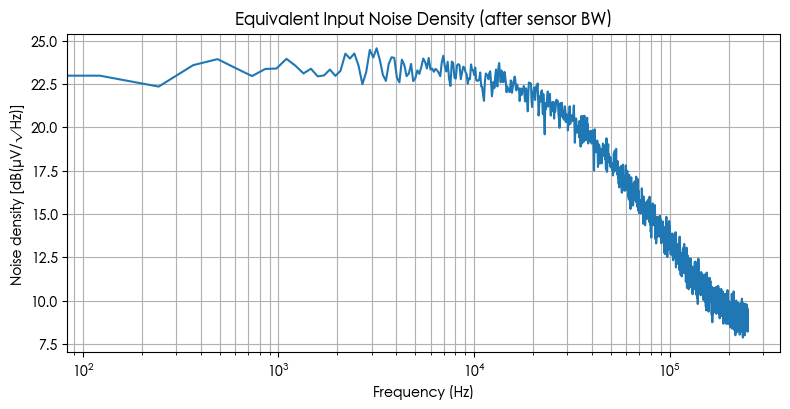

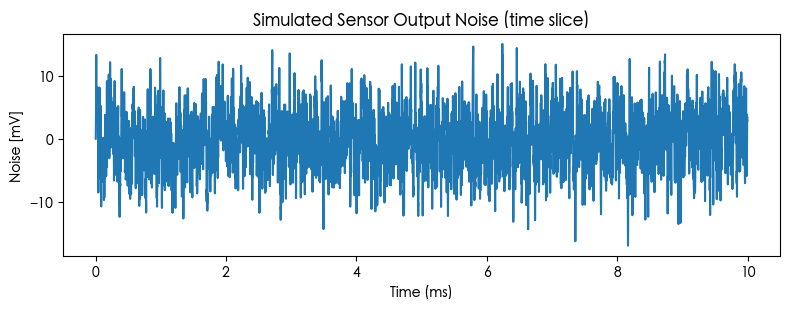

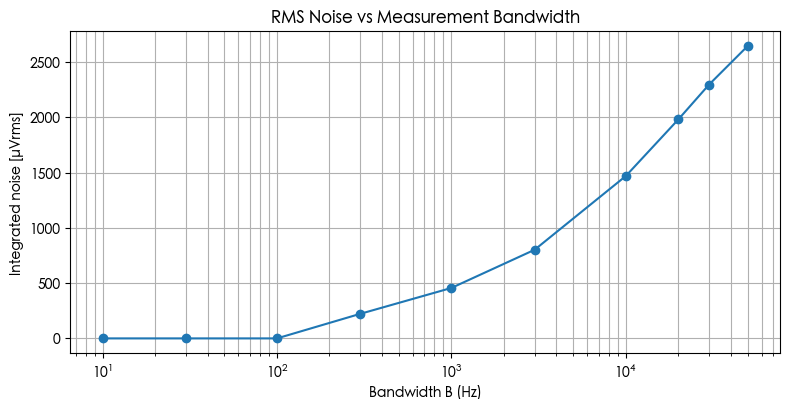

噪音仿真

作为信号链爱好者,不可能不算噪音的;直接从 PDF 里面抓取然后计算的;(解析到“5 kHz 带宽下约 10 mVpp 噪声”)→ 换算 ≈1.515 mVrms;等效白噪声密度 ≈21.4 µV/√Hz(按高斯 pp≈6.6σ 近似)。

假设器件本体为 一阶 30 kHz 带宽(数据手册典型值),并叠加一个保守的 1/f 转折 ~50 Hz:30 kHz 内整带 RMS ≈ 3.28 mVrms(仿真值)。

另外测量带宽缩窄可显著降噪:B=1 kHz→~0.47 mVrms,B=10 kHz→~1.49 mVrms。

与 3.3 V 供电、ratiometric 16-bit SAR(LSB≈50 µV) 配合:若 B≈1 kHz 时噪声 ~0.47 mVrms ≈ 9.4 LSB_rms;经 16×OSR(等效 B 降)后可进一步压到 <3 LSB_rms;如果满带 30 kHz 使用,需外加低通/过采样+平均来降低噪声并满足 S/H 建立时间。

=== 器件噪声换算(由10 mVpp@5 kHz)===

Vn_rms ≈ 1.515 mVrms, en ≈ 21.43 µV/√Hz, f_c(1/f)≈50 Hz(假设)

=== 30 kHz 传感器带宽内模拟噪声 ===

Vrms_total ≈ 3.275 mVrms

=== RMS 噪声 vs 测量带宽 B(已含传感器30 kHz极点)===

B= 300 Hz : 232.4 µVrms

B= 1000 Hz : 472.3 µVrms

B= 3000 Hz : 824.6 µVrms

B= 10000 Hz : 1493.6 µVrms

B= 20000 Hz : 2022.0 µVrms

B= 30000 Hz : 2333.5 µVrms

B= 50000 Hz : 2678.0 µVrms

噪声密度曲线(含30 kHz极点后)

噪声密度曲线(含30 kHz极点后)

时间片段(输出噪声波形,mV)

时间片段(输出噪声波形,mV)

RMS 噪声 vs 测量带宽 B

RMS 噪声 vs 测量带宽 B

后记

说到底还是一个单纯的输出电压的传感器,比较简单,但是磁场容易受干扰,可能难点在校准和安装上面。

这是他们最弱的测量产品

这是他们最灵敏的测量产品

实物

实物

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-11-01,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录