OFC 2025:低插损硅光端面耦合器(旭创/GF/台积电)

收集了OFC 2025上的三篇关于硅光端面耦合器的工作,分别来自旭创/Global Foundries/TSMC,都是采用SiN材料来做的,这是因为SiN实现低插损无需很小的线宽(130nm工艺就绰绰有余),工艺容差大,厚度/位置灵活,并且在CPO等潜在应用中能够承受高功率,以上这几点都是Si材料难以实现的。这几篇文章的结果虽然比不上台积电去年所报道的COUPE,不过也都基本达到了1 dB/facet的水平。

一、旭创在8英寸硅光平台实现的全固态氮化硅端面耦合器

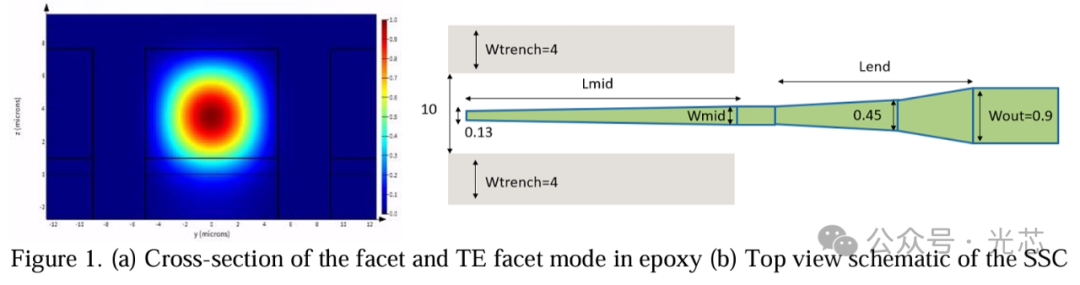

旭创报道了一种氮化硅单taper的端面耦合器设计,通过调整了氮化硅的厚度(应该<400nm),并且在两侧进行了刻槽处理,在尖端宽度为0.13um下实现了光斑的扩大和横向限制,可能还调了SiN层的位置或者使用了中道工艺的SiN层来做,一般第一SiN波导层的上下包层厚度是不对称的,不过这里看起来模斑还是比较居中对称的,因此这款端面耦合器是全固态无需掏空做悬臂梁结构,机械稳定性和长期可靠性有保证。

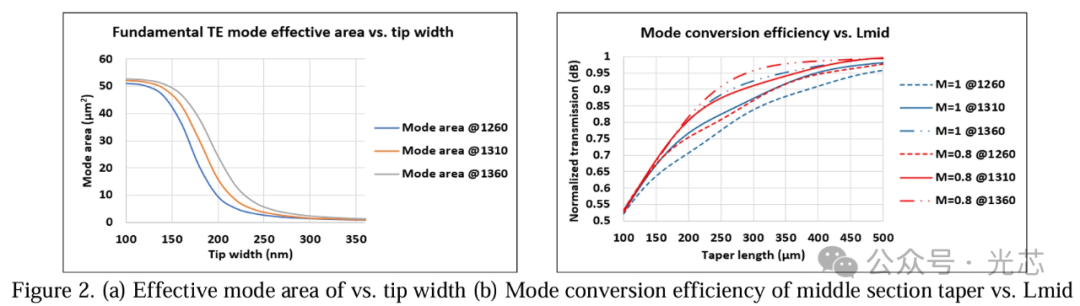

仿真显示,在两侧Trench结构无填充时光斑尺寸 MFD 约 7.85 μm(与 SMF28 的重叠率 89%,理论耦合插损0.5 dB),在E3810胶水填充时中 MFD 约 8.8 μm(重叠率 95%,理论耦合插损0.22 dB)。从0.9um的走线波导缩小到0.13um的尖端这一段采用了多段式taper设计,有助于减小整体耦合器的长度。本工作选择多项式阶数 M=0.8 的渐变形状以提高效率,并因封装限制采用 370 μm 的渐变长度。末端段渐变区采用分段线性形状(图 1 (b)),通过 3D FDTD 仿真显示 O 波段内模式转换损耗可忽略不计。

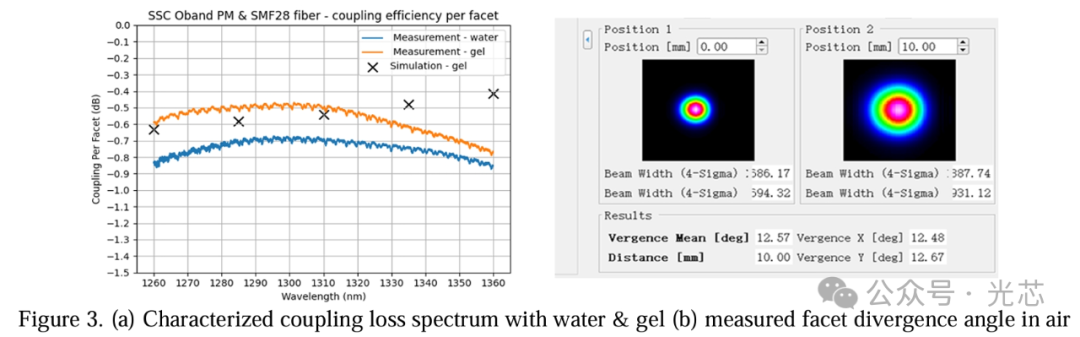

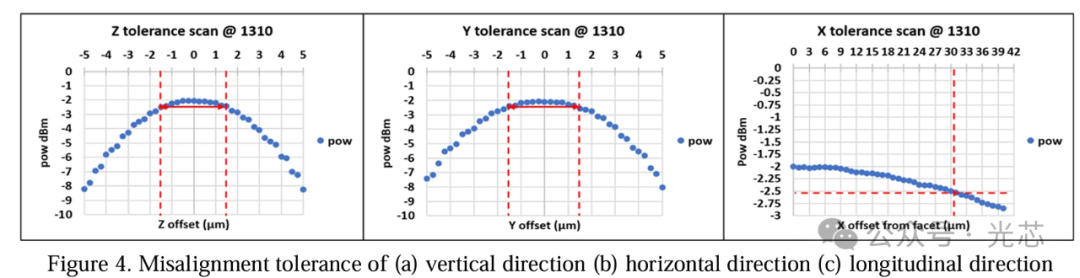

实测结果显示,该耦合器在1260-1360nm范围均能实现小于1dB/facet的插损,波长相关损耗小于0.3 dB,胶水包层下模斑更匹配,比水作为包层(折射率约1.3)时有0.2 dB的改善,在1310 nm处达到最低0.5 dB/facet的插损,实测水平 MFD 为 7.65 μm,垂直 MFD 为 7.54 μm,很圆润跟仿真也很接近。0.5dB耦合插损的上下左右位置容差为±1.5 um,前后容差为30 um。

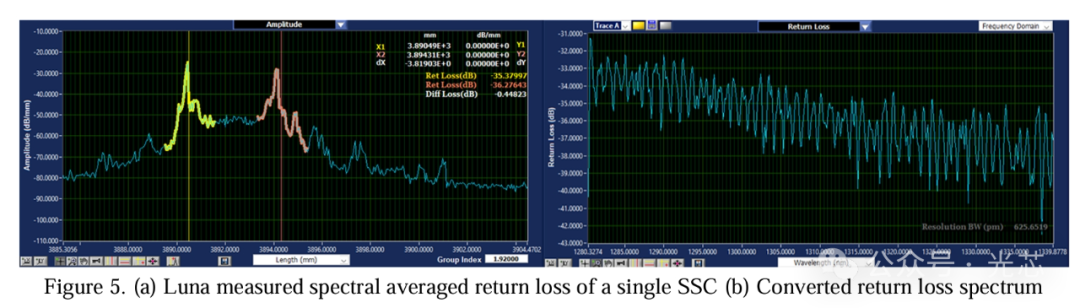

在光斑匹配的情况下,折射率差就很小了。因此对应的测得回波损耗光谱平均值为 - 34.5 dB,O 波段最坏情况为 - 31 dB。本工作完全基于代工厂可获取的8英寸标准工艺,因此是一种与标准单模光纤耦合的通用解决方案,对于激光器耦合也有收益。

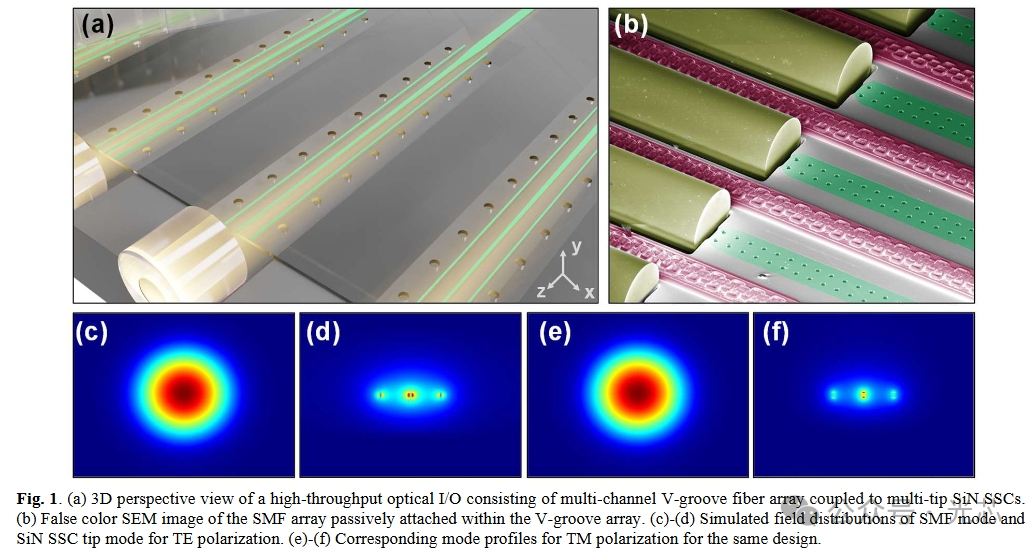

二、GlobalFoundries 12英寸硅光平台的三叉戟氮化硅耦合器

前面旭创用的是单根波导的模斑转换器,而GF这里则是采用了三根波导的结构,这种结构的工艺容差会更好一些,同时两侧的波导也能够起到横向限制光场的作用,无需两侧开槽,模斑虽然看起来没有那么圆,但跟光纤模场的重叠积分算下来也是很高的。同时这款设计的PDL特性也是比较好的(上一个旭创的工作没有提到PDL特性)。同时GF也结合了它做光纤V Groove实现无源耦合的传统艺能以及耦合器两侧打一排孔做衬底掏空,最终也是形成悬臂梁结构。前两年GF在悬臂梁结构上也花了不少功夫去优化,包括镀氧化铝抗水汽,提升长期可靠性。(不过我觉得三叉戟结构已经实现了横向限制的效果,适当调整氮化硅的厚度/位置或者三叉戟的尺寸,也还是可以全固态实现低插损)。

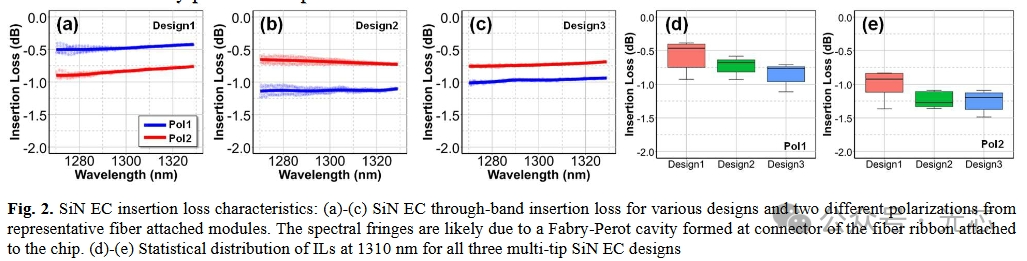

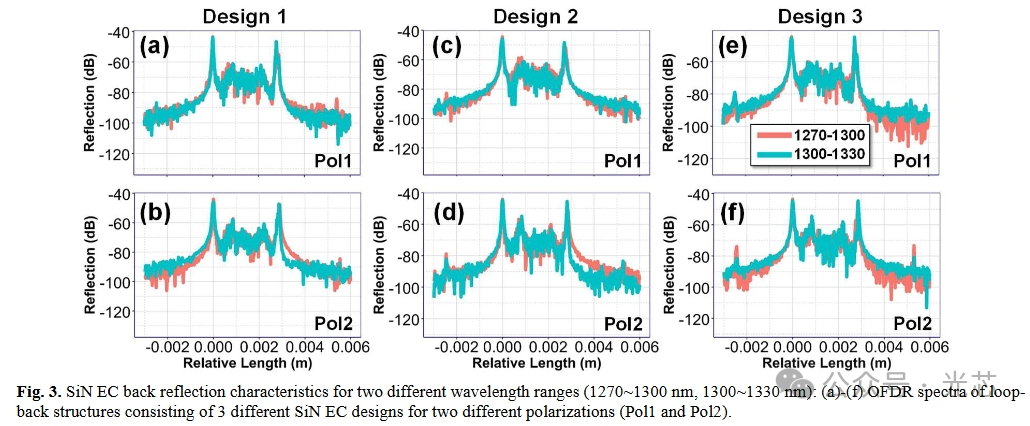

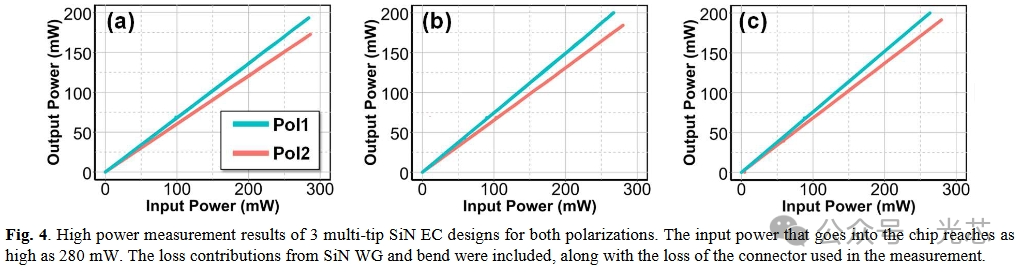

该工作设计并制作了基于 V 型槽的测试结构,测量三种不同设计的多尖端 SiN ECs 的 IL 和 ORL。结果显示,在 1300nm 为中心的 60nm 带宽内,所有设计对两种偏振态都有低 IL,Design 1 的 IL 最低,其中一个偏振的插损在1265-1335nm范围的插损都可以小于0.5dB,PDL<0.4dB;而Design 3 的偏振相关损耗(PDL)表现出色<0.25 dB。且所有设计波长相关性小,适合宽带应用。考虑所有因素,Design1 和Design3的插损均小于1dB/facet,也是挺不错的结果了;其回损均小于 - 40dB,有效管理了背向反射。

另外该工作对三种设计的多尖端 SiN ECs 进行高功率测试,在 1310nm 波长下,输入功率高达 280mW 时,输出功率与输入功率呈线性关系,且往返测试曲线重合,证明其适用于高功率应用。

看了一下GF去年报道的单个氮化硅taper的悬臂梁耦合器插损是0.6/0.8 dB@TE/TM模,前年基于亚波长光栅的Si悬臂梁耦合器也是0.6/0.8 dB的插损,年年会出一款新设计。也许明年就是三叉戟的亚波长光栅氮化硅波导设计了。

三、TSMC 12英寸硅光平台的PECVD氮化硅光纤耦合器

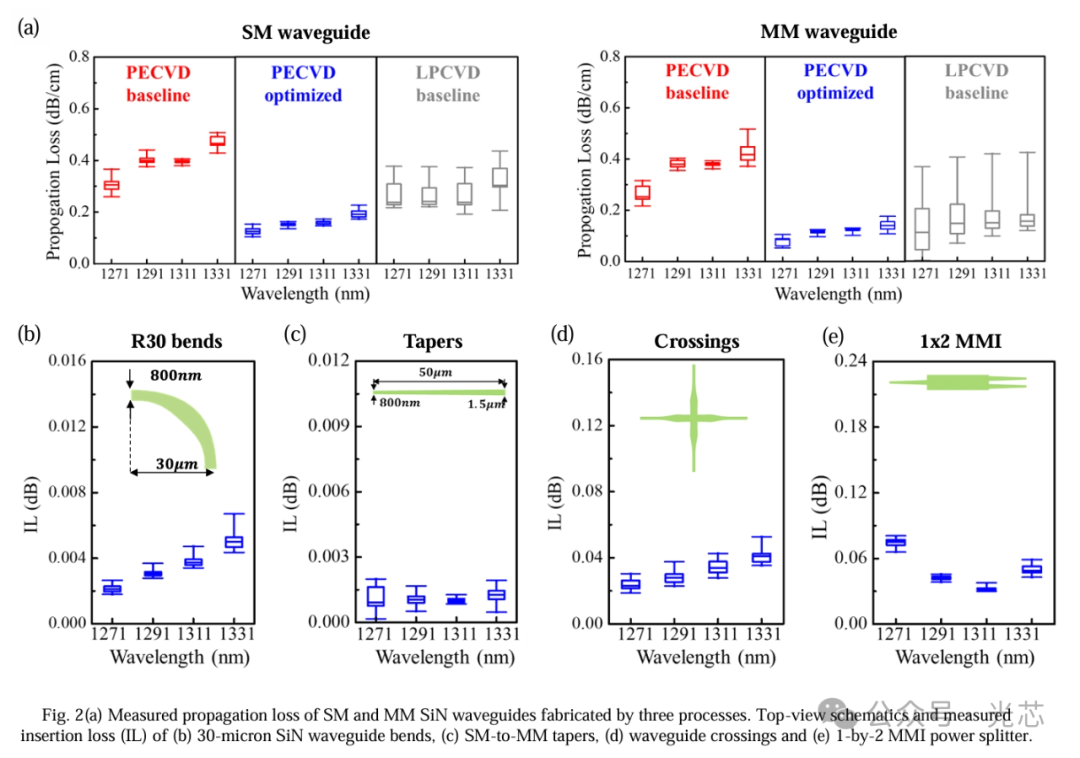

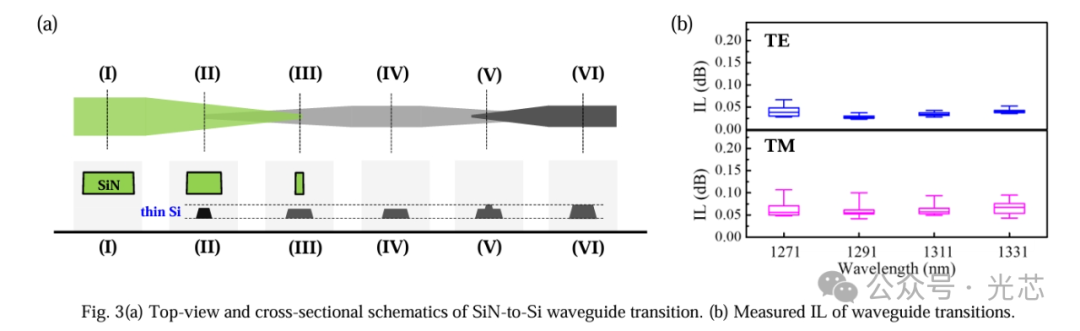

TSMC的工作主要聚焦于优化PECVD SiN-on-SOI的工艺,波导损耗已经能够降低到0.2 dB/cm以下,在同类平台算比较好的,也开发了一些器件库,插损特性也是挺不错的。TSMC的顶硅层采用的是270nm的厚度,与常用的220nm有些区别,不知道有何考量,但他的Si-SiN transition做得很好,双偏振的插损只有0.06 dB,主要特点是底下的Si波导也做了双层的刻蚀,是一个SiN→薄Si条形波导→Si脊型波导→270 nm厚Si波导的耦合,Si taper尖端尺寸<90nm。这个transition的设计和工艺控制做得是真好,GF之前花了挺长时间设计了好几种结构,最后通过左右错位的形式才获得了0.05/0.11 dB的插损。

(有关PECVD/LPCVD/SiN-on-SOI的工艺可以参考之前这两篇:①氮化硅SiN集成光波导平台(一):SiN-on-SOI平台 ② 氮化硅SiN集成光波导平台(二):SiN-based 平台)

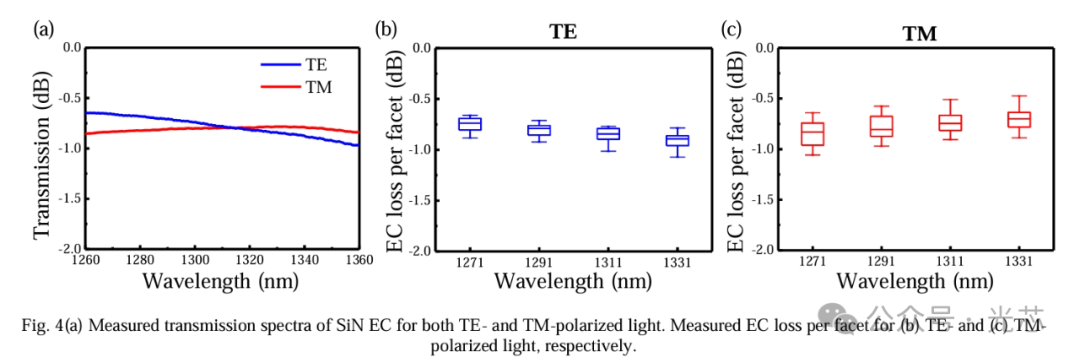

而针对耦合这一块,这篇文章报道的还是一个5um模斑的小模场耦合器的设计,实现了O波段插损<1dB/facet,PDL小于0.2 dB的数据。这个插损算是比较正常,不算是很亮眼的一个数据,亮点主要还是在于它的12寸晶圆一致性可以控制到标准差0.1 dB以内,这是比较好的。不过未来肯定还是要瞄着更大模斑的通用单模光纤耦合器去做,毕竟前两篇文章包括近几年各大代工厂的工作都展示了氮化硅与单模光纤的插损理论上可以做的很低,重点还是在于晶圆一致性的管控。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-04-01,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读