ISSCC 2026:Broadcom基于7nm ASIC+硅光MZM的3D集成6.4Tb/s 4.5pJ/b CPO

ISSCC 2026:Broadcom基于7nm ASIC+硅光MZM的3D集成6.4Tb/s 4.5pJ/b CPO

光芯

发布于 2026-03-02 21:54:02

发布于 2026-03-02 21:54:02

基于此,Broadcom在2026 IEEE国际固态电路会议(ISSCC)上发布了一款用于51.2T交换的6.4Tb/s CPO专用ASIC,该7nm ASIC与硅光芯片PIC进行3D封装,能量效率达到4.2pJ/b。在单路106.25Gb/s速率下,其PAM-4格式TIA的灵敏度优于-11dBm,误码率下限(BER floor)优于1E-9;发射的PAM-4光眼图实现1.48dB的TDEQ和4.57dB的消光比(ER)。

◆ 整体系统架构

发射路径中,模拟前端(AFE)后接时钟数据恢复(CDR)模块,对来自主机的输入数据进行重定时和串并转换,CDR由发射锁相环(TXPLL)产生的4倍时钟(clk4t)驱动。串并转换后的数据流通过发射数字信号处理器(TX DSP)送入MZM驱动器,其中PAM-4信号的温度计编码支持利用最高有效位(MSB)数据同时驱动两个调制器分段。接收路径采用数字信号处理器(DSP)适配型TIA,其输出通过有机基板直接驱动Host ASIC。此外,ASIC内部集成320个mPD读数接口和320个heater数模转换器(DAC),用于PIC的光学传感与控制。

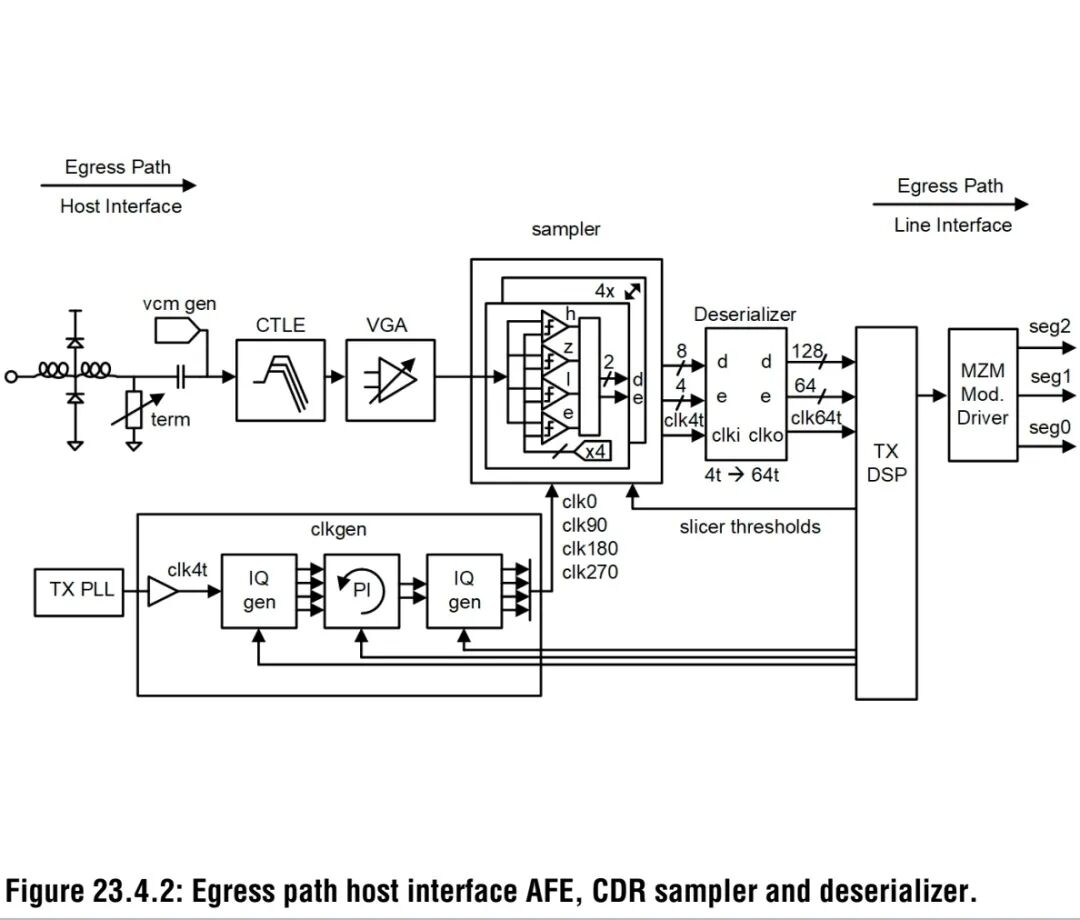

◆ 发射路径Host接口

图23.4.2展示了发射路径的主机接口架构:输入信号通过校准终端电容耦合至连续时间线性均衡器(CTLE),该终端采用带宽扩展T型线圈T-coil实现输入静电放电(ESD)保护;CTLE的输入共模电压由可编程DAC设定,其输出驱动可变增益放大器(VGA),进而连接4倍时间交织采样器;CTLE和VGA均采用电阻校准和T型线圈技术扩展带宽。

CDR的4个采样相位由时钟生成(clkgen)模块基于TXPLL的clk4t时钟产生:clkgen模块内部,数字适配型延迟锁定环(DLL)基正交时钟生成器(IQgen)驱动相位插值器(PI),后续第二个IQgen生成0°、90°、180°和270°的采样相位。4组限幅器组将数据和误差信息送入解串器,在64倍时钟(clk64t)速率下输出128位数据和64位误差位至TX DSP;TX DSP内置CDR适配模块实现时钟恢复环路,最终将PAM-4的MSB和最低有效位(LSB)数据送至线路侧。TX DSP中的限幅器电平适配算法通过16个9位DAC调节每个采样器组内4个限幅器的阈值电平。

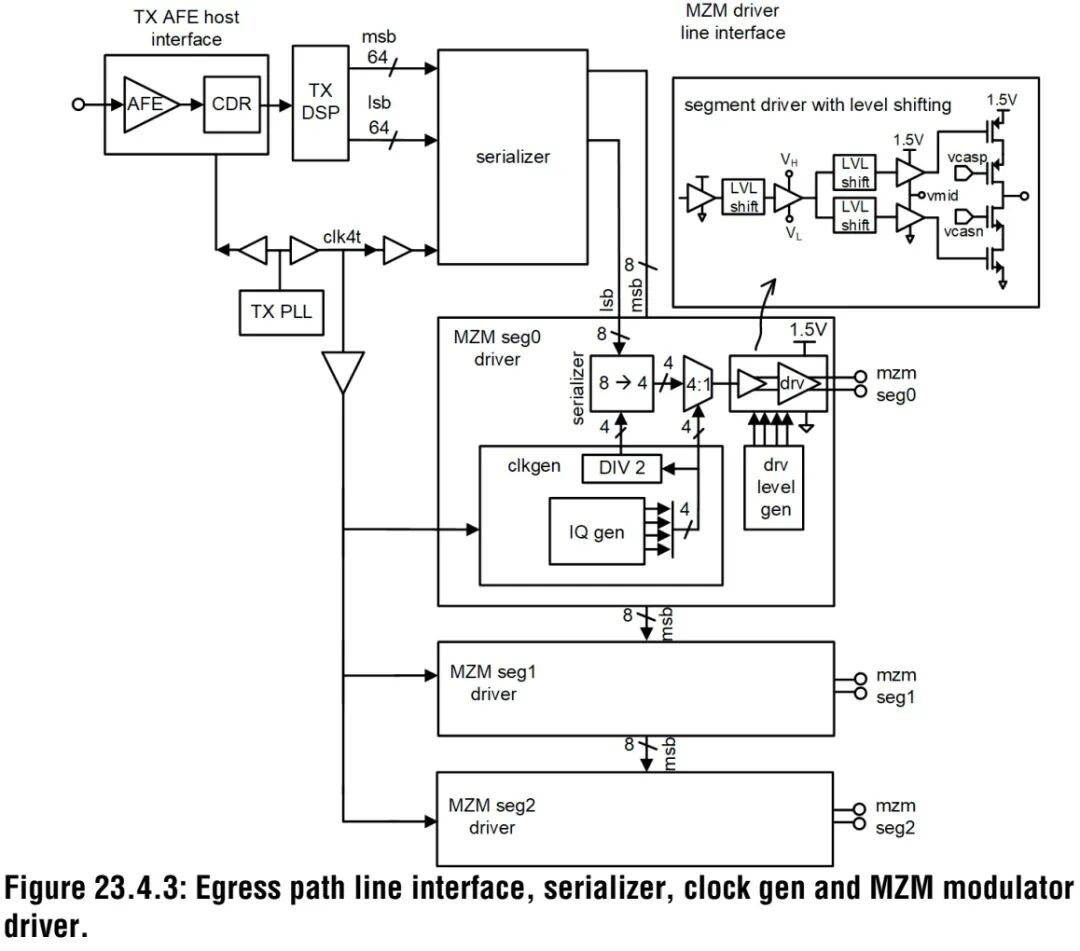

◆ 发射路径线路侧接口

如图23.4.3所示,串行器首先将来自TX DSP的64位重定时并行MSB/LSB数据转换为8位数据流,这些位于8倍时钟(8t)域的数据流被分配至3个驱动器分段——第一个分段分配给LSB,后两个分配给MSB。TXPLL的4倍时钟(4t)沿3个MZM驱动器分段分布,每个分段的本地时钟生成器校正时钟失真,并通过正交时钟生成模块产生4个相位;来自IQgen的校准后8t和4t时钟驱动分段驱动器的最后两级串行器,4:1多路选择器输出经两级电平转换预驱动器转换为1.5V不归零码(NRZ)信号,驱动堆叠输出级的PMOS和NMOS栅极;预驱动器和共源共栅电压电平分别由分段内的电平生成低压差稳压器(LDO)和DAC提供。

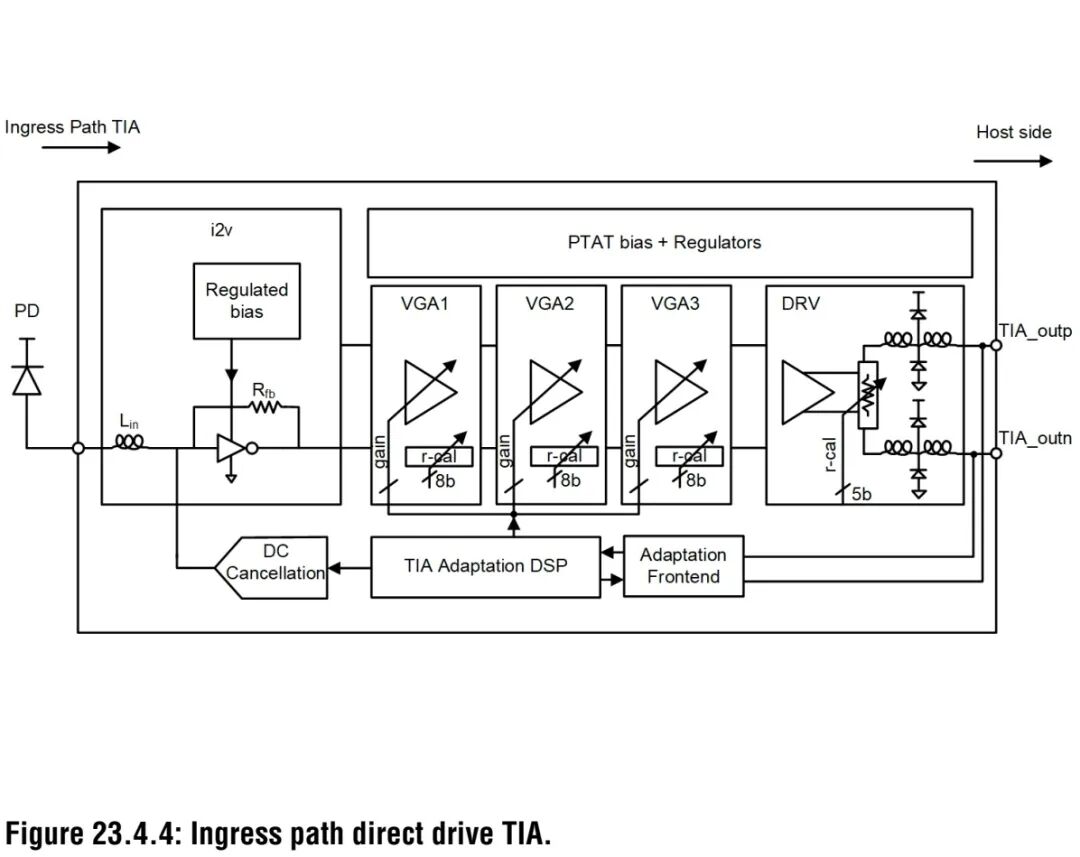

◆ 接收路径直接驱动TIA

接收路径的直接驱动TIA架构如图23.4.4所示:线路侧的PD阳极与电流-电压转换器(i2v)对接,输入线圈(Lin)通过与输入寄生电容谐振扩展带宽;i2v核心基于带反馈电阻(Rrb)和稳压偏置电流的反相器设计,其输出以伪差分形式驱动第一级VGA(VGA1),后续通过VGA2、VGA3至输出驱动器的信号路径均采用全差分结构。VGA向驱动器扇出信号,通过T型线圈扩展带宽,并采用8位可调校准负载电阻,增益通过数字增益调节码控制;输出驱动器采用5位终端校准和T型线圈技术扩展带宽,驱动ESD保护电路和输出凸点。

TIA差分输出通过有机基板直接驱动主机交换ASIC,每个通道的TIA由本地DSP实现数字适配——驱动VGA增益控制字以调节幅度,并通过连接至TIA输入的直流抵消DAC补偿直流偏移;适配前端向DSP提供适配信息,每个VGA的增益约为6dB,可编程步长0.2dB。该TIA的标称输入电流噪声密度为15pA/√Hz,功耗低于50mW,且每个TIA通道内部集成本地与绝对温度成正比(PTAT)偏置和电源调节模块。

◆ 芯片实现与性能测试

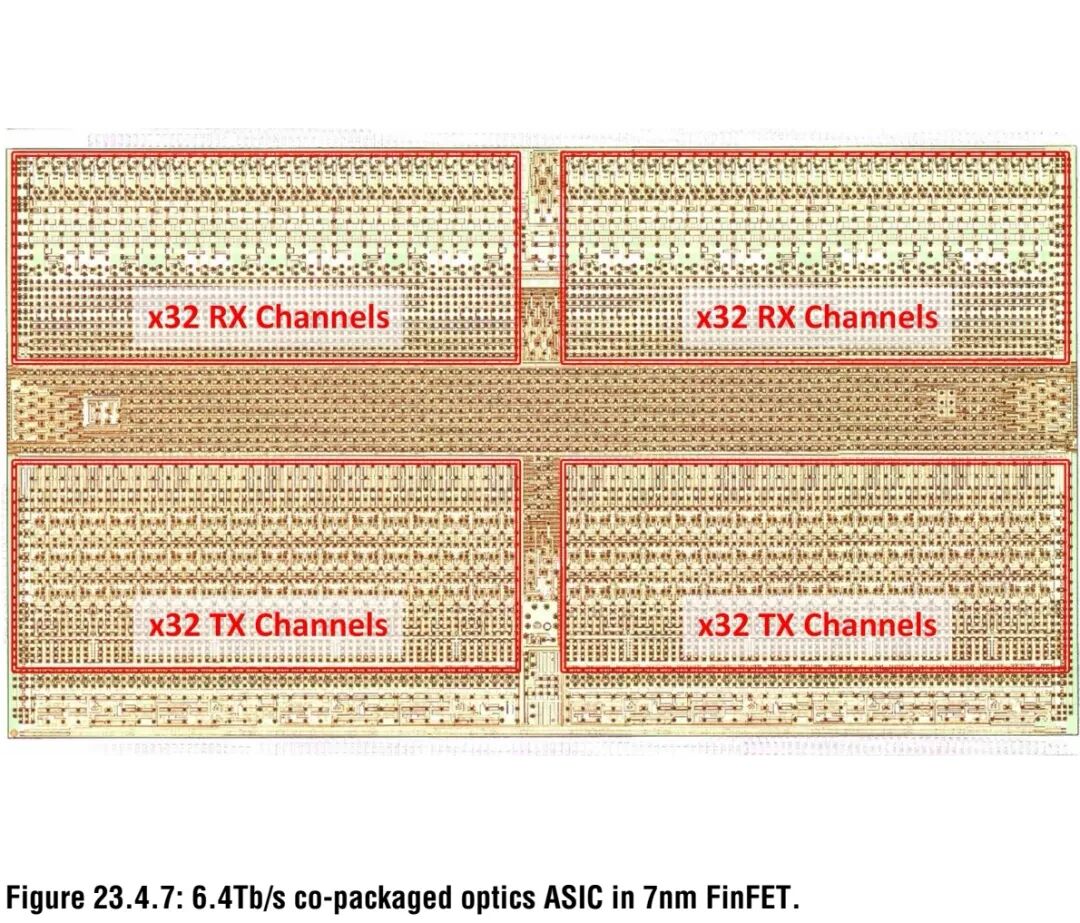

该CPO ASIC采用7nm FinFET工艺制造(图23.4.7),单片裸片集成64条发射/接收通道、TXPLL、辅助公共电路及ADC/DAC组件;6.4Tb/s光引擎通过7nm ASIC与PIC硅片的3D封装实现,多个光引擎与主机网络ASIC共封装以支持可扩展吞吐量。

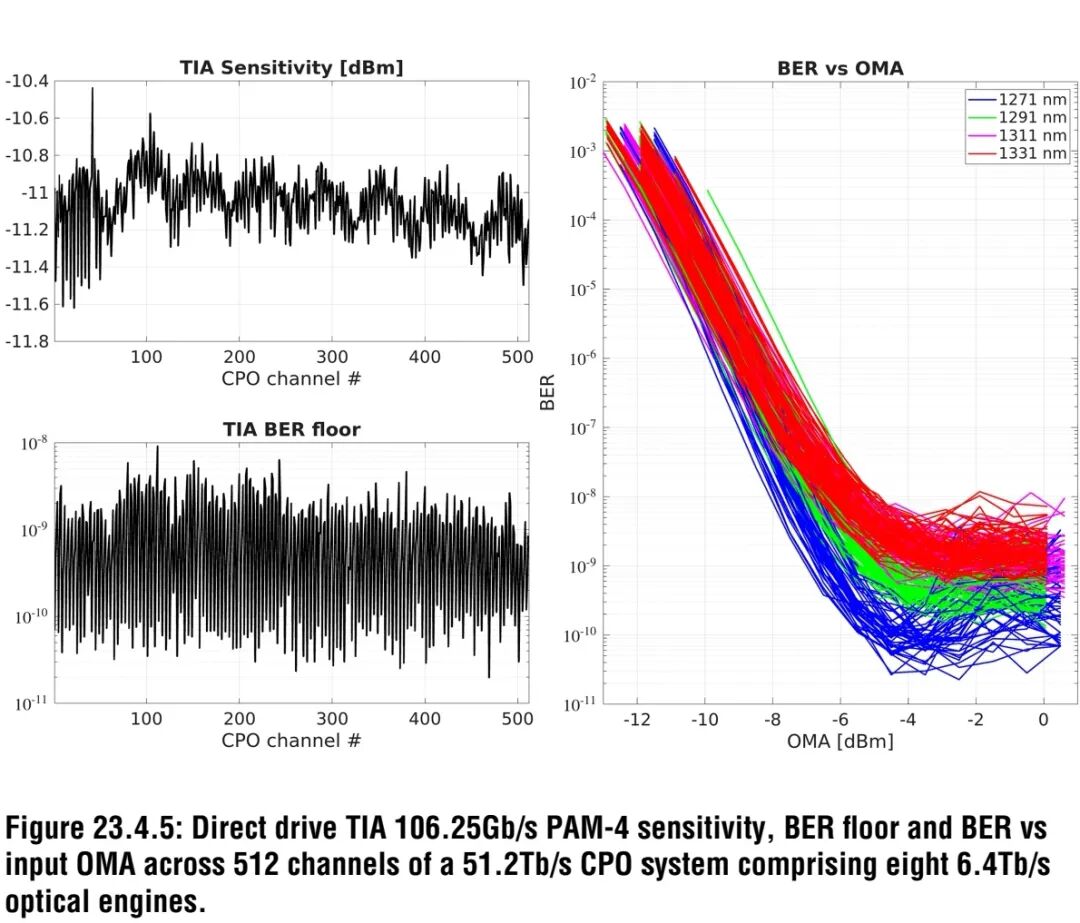

接收路径直接驱动TIA的性能测试结果如图23.4.5所示(经host网络ASIC均衡后):在由8个6.4Tb/s光引擎组成的51.2Tb/s CPO系统中,512条通道在4种波长下的测试表明,TIA平均灵敏度优于-11dBm(符合IEEE802.3标准中106.25Gb/s PAM-4的2.4E-4误码率要求),平均误码率下限优于1E-9。106.25Gb/s PAM-4速率下,发射路径的前向纠错(FEC)前误码率优于1E-9,99.98%以上通道无差错。

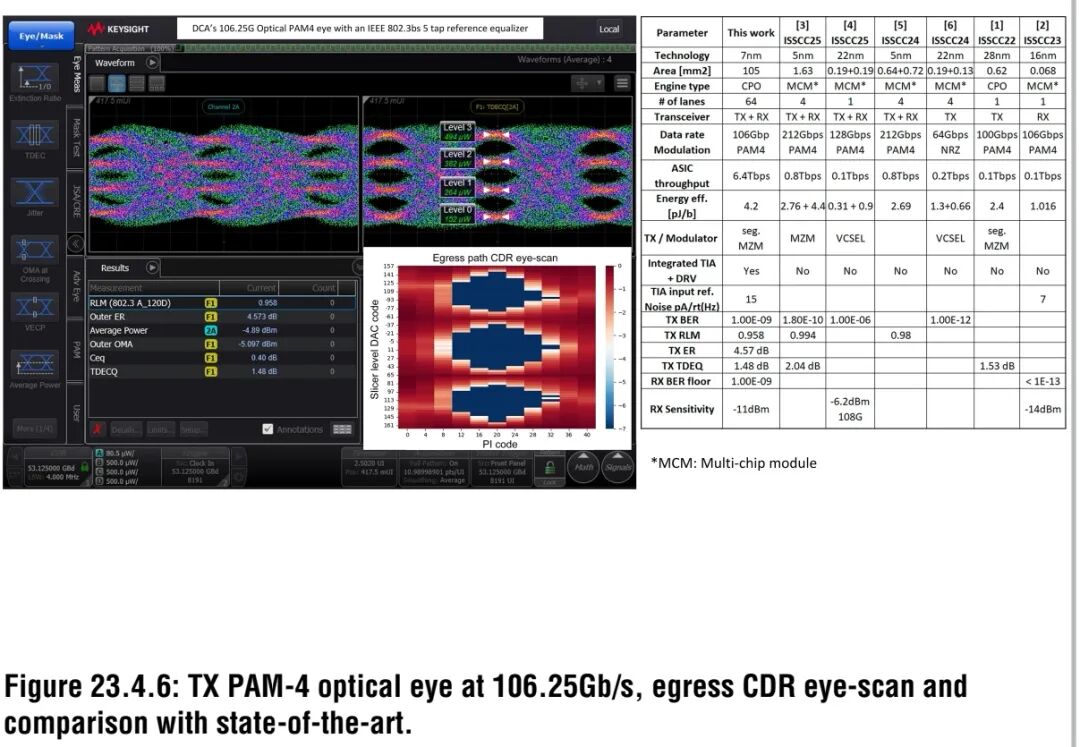

图23.4.6展示了发射路径CDR的眼图扫描结果和PRBS-13码型的PAM-4光眼图(采用IEEE 802.3bs标准接收均衡器及5抽头FFE测量):发射机实现1.48dB的TDEQ、4.57dB的外部消光比(ER)和0.958的RLM。与现有先进光接口收发器的对比表明,该6.4Tb/s CPO ASIC通过64条106.25Gb/s PAM-4通道实现最高集成度和吞吐量,同时保持4.2pJ/b的极具竞争力的能量效率。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-02-22,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读