从国产迅芯微电子看高性能示波器设计架构(附带读者问题回复)

今天来看一个国内厂家的应用手册:

高速示波器的设计

高速示波器的设计

这份文档本质上给出了两类系统:

多通道示波器前端(针对 250MS/s – 2.5GS/s 级别)

高带宽示波器前端(10GS/s – 40GS/s 级别)

并配套说明VGA(Variable Gain Amplifier)增益放大器,高速 ADC(8 bit,高速 LVDS 接口),时钟芯片(GHz 分频器、PLL/VCO),多通道同步采集架构;这基本就是现代数字示波器模数前端的典型结构。

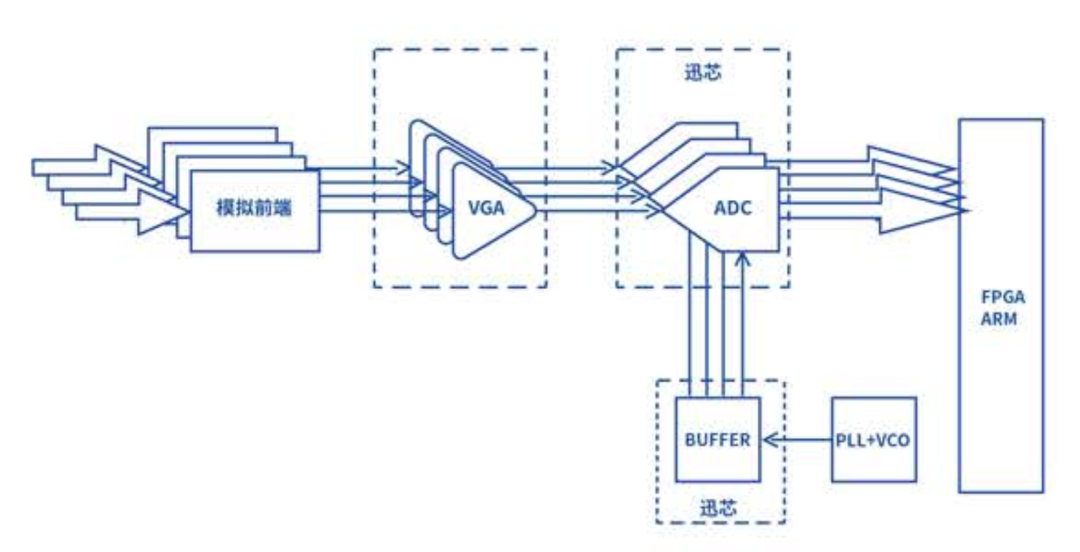

多通道示波器前端

多通道示波器前端

多路输入(多个探头的前置放大)

VGA:用于调节输入动态范围

ADC(250MS/s – 2.5GS/s 8bit)

FPGA:负责采样数据接收、Trigger 深度采样

PLL/VCO:产生高速采样时钟

BUFFER/Trigger:做触发通道,这就是一个典型的示波器前端结构。

为什么示波器前端必须用 VGA?

示波器要测1mV 小信号;200V 大信号,动态范围跨度巨大,不可能依赖 ADC 自身输入范围。

VGA 的作用:

输入信号 | VGA 增益 | 送到 ADC |

|---|---|---|

小信号 10 mV | 放大 ×20 | 200 mV |

大信号 5V | 衰减 /10 | 0.5 V |

所以 VGA 是示波器前端必备。

为什么 ADC 选 8 bit?不是应该更高?

示波器不等于高精度仪表,它更强调:带宽(GHz),上升时间,捕捉快瞬态

8-bit 可以提供足够 SNR(48dB),换取:极高速,极低输入电容,极高 SFDR 于高频,因此 8-bit 是行业标准(Tek、Keysight 的前端同样如此)。

指标不写可以直接猜

指标不写可以直接猜

型号 | 速率 | 接口 |

|---|---|---|

AAD0802500 | 250/500/1000MSps | 8-bit LVDS |

AAD0852500 | 1.0/2.5GSps | 8-bit LVDS |

AAD08112000 | 1GSps | 8-bit LVDS |

AAD12Q1000 | 1GSps | 12-bit(研发) |

2.5GSps 已经很高,可以用于 1GHz 示波器,LVDS 接口说明需要 FPGA 进行高速解串/采集。

文档推荐的 VGA(AVGA4000)

带宽:4GHz(-3dB);典型示波器前端必须要 >3× 带宽的放大器,以保证:快脉冲不失真,上升沿更干净,保证时间域测量精度

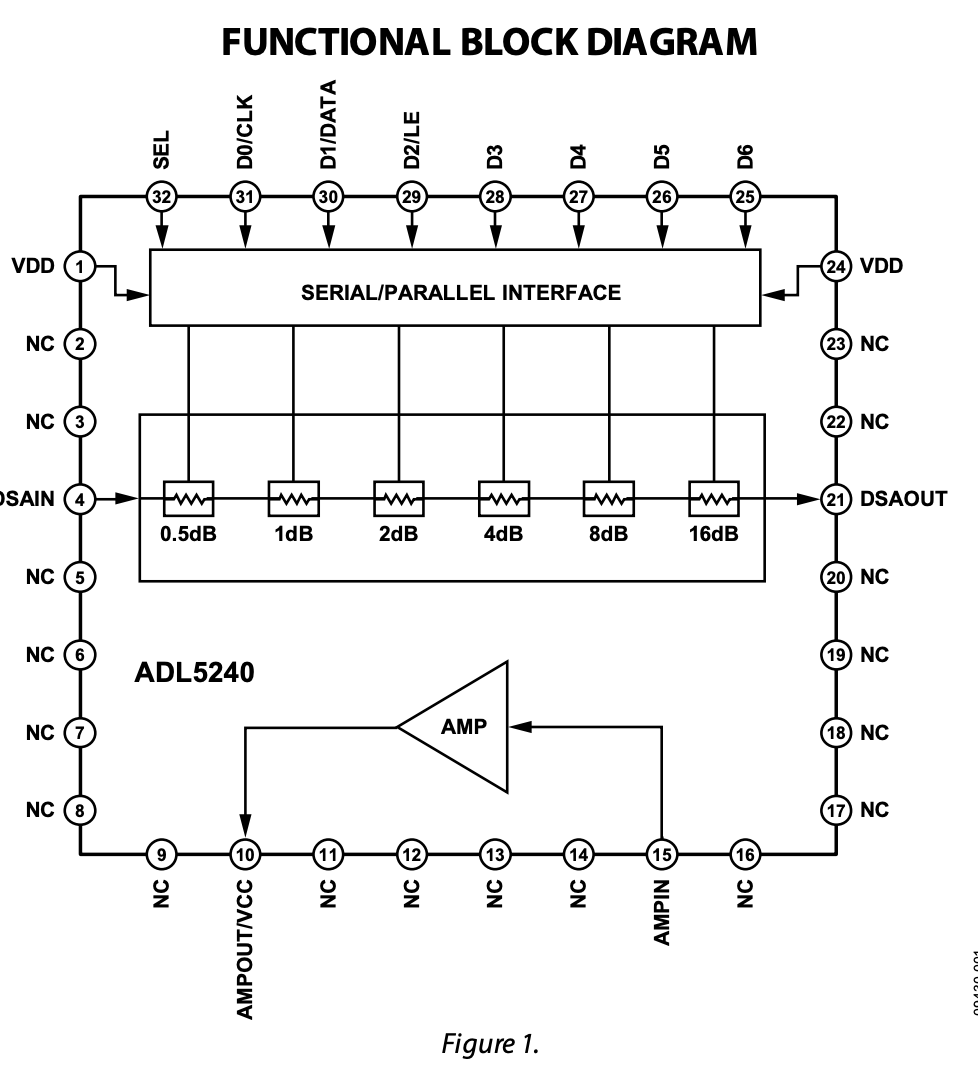

类似ADI ADL5240:

当然高速的东西是配套的,所有 ADI 的这个参数不够

当然高速的东西是配套的,所有 ADI 的这个参数不够

时钟芯片

推荐:

ABUF944:7GHz 分频器

ABUF18Q:16GHz 分频器

ABUF18Q:16GHz one-shot

用于生成:快速 ADC 采样时钟,多通道相位同步(重要!),以及示波器多通道同步依赖,同相位时钟,同延时,低抖动(<100fs),这就是为什么必须用 GHz 级分频器。

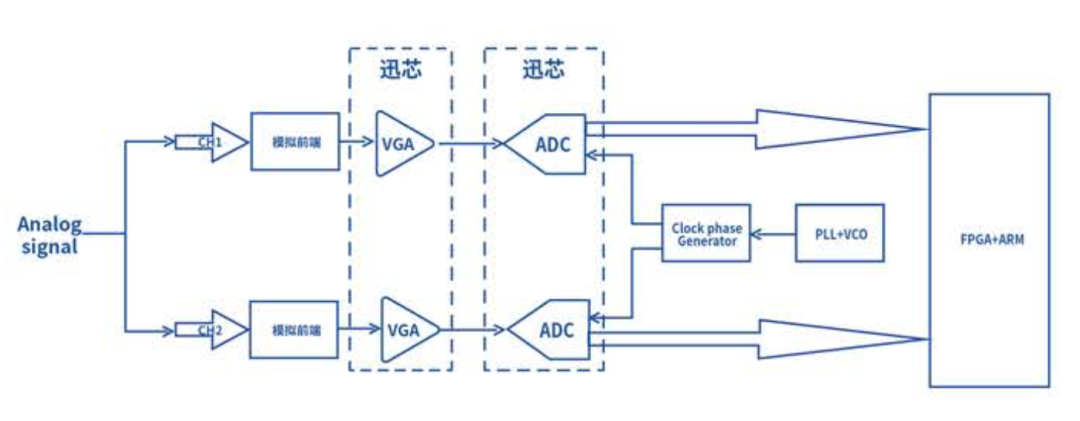

高带宽示波器前端

高带宽示波器前端

这一页的内容是10GHz、20GHz、40GHz 示波器,其中ADC 速率高达 10GSps、20GSps、40GSps(仍然是 8bit)

高带宽两种模式

双通道模式 :两个 ADC 各自采样一条路径

单通道模式(interleave)两个 ADC 交错倍频采样,如:两路 20GSps → 合成一路 40GSps,两路 10GSps → 合成一路 20GSps。

关键技术难点在时间偏斜校正(skew calibration),增益匹配,以及offset 匹配,一部分是 ADC 内部校准另外一部分是 FPGA 做数字校准。

型号 | 速率 | 输出接口 | 状态 |

|---|---|---|---|

AAD085010G | 10GSps | 8bit LVDS | 量产 |

AAD085020G | 20GSps | 8bit | 量产 |

AAD085040G | 40GSps | 8bit | 量产 |

这是国内极少数可做到 10–40GSps 的芯片供应链。

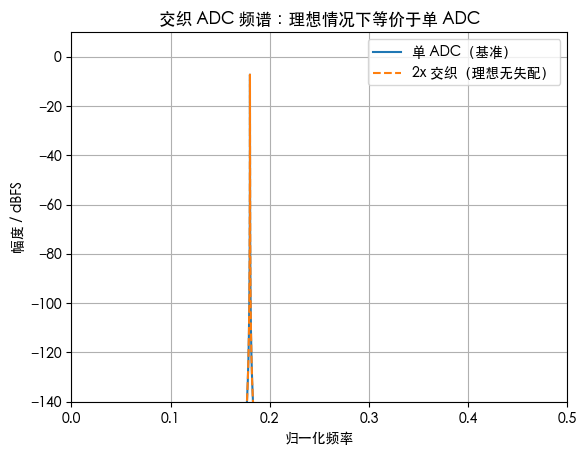

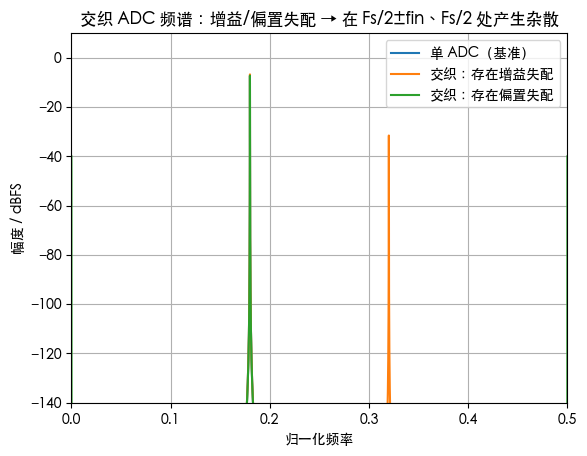

再次说明多ADC的交织误差

仿真设置概要

总采样率:(归一化,方便理解,可当成 1 GS/s)

输入信号:

点数:,用汉宁窗 + rFFT 计算幅度谱(dBFS)

交织方式是偶数采样点 → ADC_A;奇数采样点 → ADC_B,然后把两路样点“插回”到原时间顺序,即得到交织输出。

理想交织 = 单 ADC

理想交织 = 单 ADC

第一张图里两条曲线(单 ADC & 理想 2× 交织)完全重合:只有一个主谱线在 处,噪声底受窗函数影响,大约在 −130 dBFS 以下。

说明在完全无失配(增益、offset、时序都完美一致)时,2× time-interleaving 在频域上与一个“理想翻倍采样率的单 ADC”是等效的。

数学上可以这样理解:原始信号为离散时间 ,我们定义:

如果两路 ADC 采样精确、无误差,那重构时:

偶奇

所以频谱 ,自然不会多出杂散。

图 2:增益/偏置失配 → 在 相关位置冒 spur

仿真中设定:

(1 dB 失配)

对应输出:

这个可以拆成:

平均增益交替项

注意那项 等价于一个频率为 的 cos 信号:

所以“交替增益”相当于把原信号乘以一个 的正弦,从频域角度看就是:

原谱 被搬移到 处,产生两个对称 spur。

这就是在第二张图里看到的:除主信号 外,在接近 、 位置出现两条明显杂散线。

偏置失配

仿真中设定:

ADC_A offset = 0

ADC_B offset = 0.02(大约 5 LSB)

同理可写成:

常数项 → 在 直流 DC 处产生一个 spur

交替偏置项 → 在 处产生 spur

因此你在第二张图可以看到:

DC 附近有一根线(偏置平均值), 处还有一根线(交替偏置)

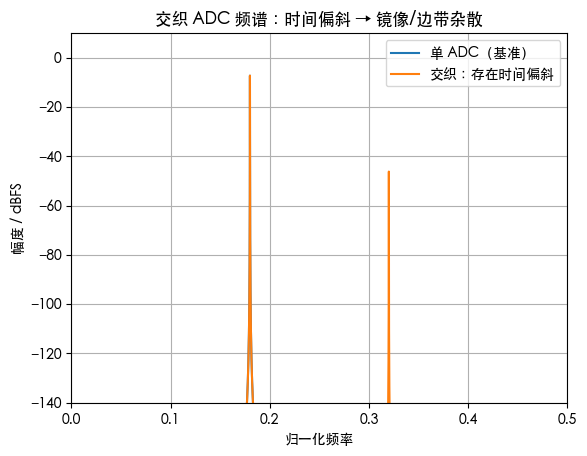

图 3:时间偏斜(Skew) → 镜像/边带杂散

image-20251127193519659

image-20251127193519659

仿真中设定ADC_B 的采样时间比 ADC_A 延迟 2% 的 Ts

也就是实际采样信号为:

对一个正弦信号 来说:

延迟 等价于增加相位

于是交织输出可以拆成:

误差项

又出现了 ,所以误差项在频域上会出现在: 附近(同样是“半采样率镜像”)

区别在于:其幅度正比于 => 频率越高、skew 越大,spurs 越严重;在第三张图中能看到主信号旁边一对明显的边带杂散,而且随着频率靠近 Nyquist 会愈发严重(这里我们选了 0.18Fs,就是为了使效果更夸张)这也是高速示波器里要用到精细的时间对齐校准的原因。

对 2× 交织 ADC 来说: 理想状态:频谱 = 单 ADC,完全干净 增益失配:在 处冒两条 spur 偏置失配:在 DC 和 出现 spur 时间偏斜:在 附近产生与频率成正比的杂散

题外话

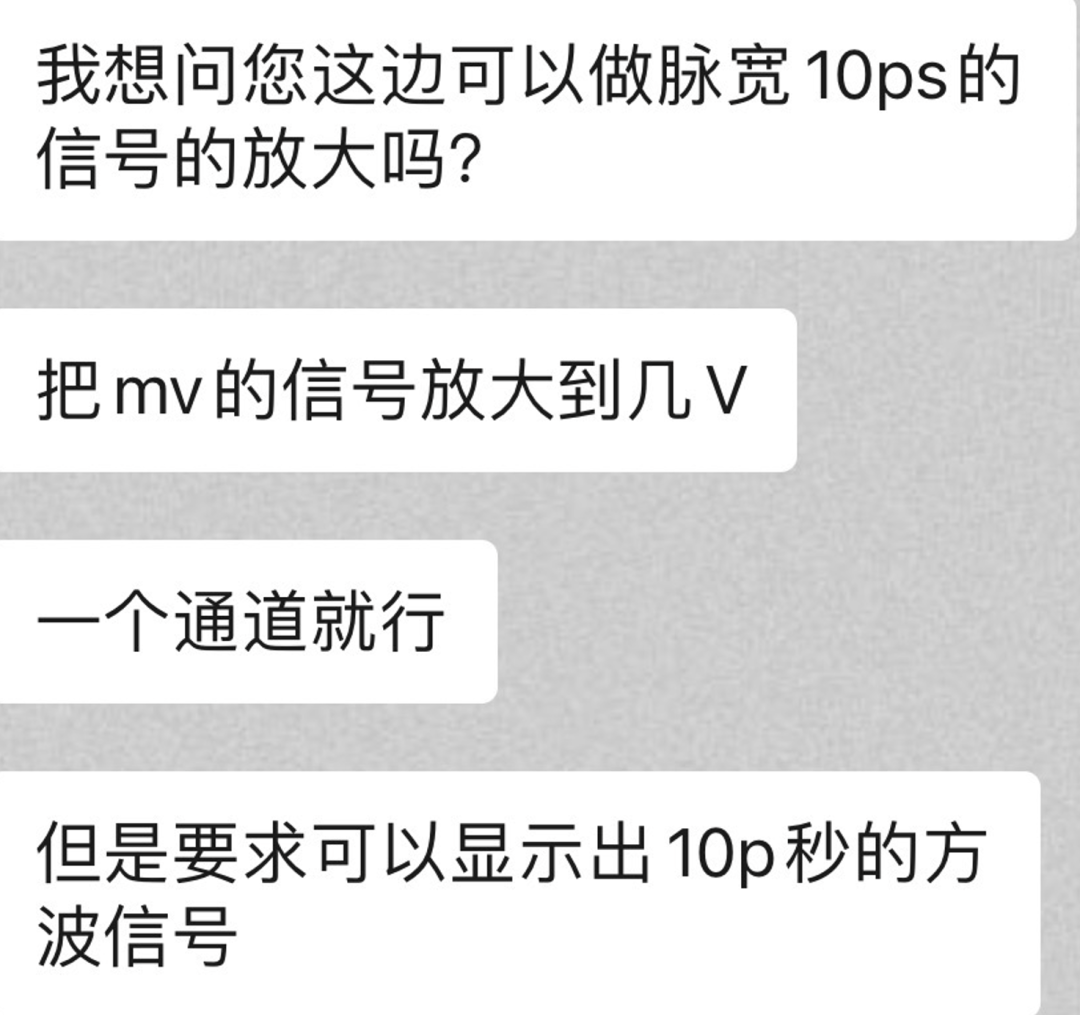

本来这个内容就到此为止了,但是一个朋友问了一个问题,我觉得可以引申一些有意思的东西:

我们从专业的信号链设计角度看看这个要求有多么的变态!

我们从专业的信号链设计角度看看这个要求有多么的变态!

逐句解读

“我想问您这边可以做脉宽 10ps 的信号的放大吗?”

他希望放大的,是脉冲宽度只有 10 皮秒 的信号。

“脉宽 10ps”通常理解为:上升沿+高电平+下降沿加起来差不多这个量级,也就是一个 极其窄的超高速脉冲。

“把 mV 的信号放大到几 V”

输入只有 毫伏级(比如几 mV)的幅度,

希望放大到 几伏(比如 1~5 V)。

增益量级大概是 ×100~×1000(40~60 dB)。

“一个通道就行”

不需要多通道,只要单路放大链路。

“但是要求可以显示出 10ps 的方波信号”

不只是“检测到有信号”,而是要在示波器上“看清楚”这个 10ps 方波的形状:能看见类似方波的波形;上升沿、下降沿不要被拖得太慢;高电平宽度要接近 10ps。

总结一下:

他在问:能不能做一个单通道放大器,把几 mV 的 10ps 方波脉冲放大到几 V,并且在示波器上还能清晰看到 10ps 的方波形状?

从指标推回硬件需求,太他妈的难了!

10 ps 对应的带宽有多恐怖?

用非常熟的经验公式:

如果把 10 ps 当作上升沿时间 :

而且是方波,要看得“像方波”,至少要保留到第 3~5 次谐波,实际系统带宽往往要再乘 2~3 倍:35 GHz × 2 ≈ 70 GHz,甚至接近 100 GHz 级别 的前端

也就是说,他这个需求隐含的是 30~100 GHz 的模拟带宽。

这已经远远超出常规宽带放大器、常规示波器的范畴,是毫米波 / 光电前端才会涉及的领域。

“mV → 几 V”的大增益在几十 GHz 几乎做不到

假设:

输入:1 mV 量级

输出:1 V 量级 → 增益 60 dB(×1000)

而现有的毫米波宽带放大器:单级一般 10~20 dB 增益;3 级串起来才能到 40~50 dB,而且已经很难保证平坦度、稳定性和噪声;还要配合匹配网络、走线、封装,一点点寄生都成问题。

再考虑噪声:10ps 脉冲意味着你在几十 GHz 的超宽带内都在“吃”噪声;mV 级小信号 + 超大带宽 → 信噪比会非常差;还要放到几 V,更是把所有噪声一并放大;现实情况是在 30~70 GHz 做一个 大增益 + 低噪声 + 线性好 的放大器,是科研级/军工级课题,不是一个普通模拟放大链路能解决的。(如果不是写错单位,那普通人是真做不出来)

上面的内容就告一段落,来看看里面有趣的知识点。

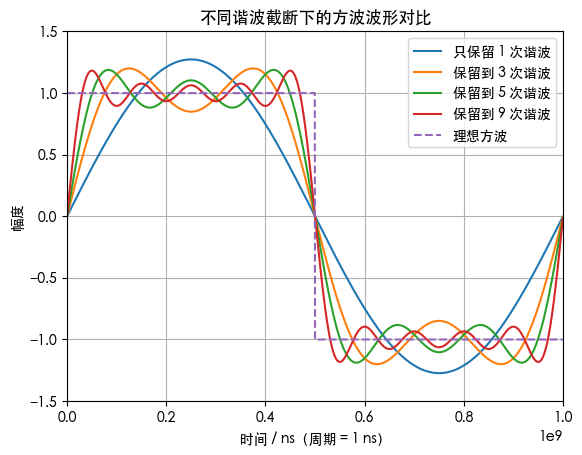

要看得“像方波”,至少要保留到第 3~5 次谐波

上面的内容里面有这句话,其实这个暗含了采样率在工程上面应用的真谛,可以算出来给你看。

50% 占空比方波的傅里叶级数

单位幅度、50% 占空比的理想方波可以展开成:

特征:只有 奇次谐波;第 个奇次谐波()的幅度比例是 。

所以:

基波:系数 1

3 次谐波:1/3(幅度仍然很大)

5 次谐波:1/5

再往上:1/7、1/9……越来越小

“方波长得方”就是因为高次谐波把边缘拉得很陡、波顶拉平。如果只留基波,就是一条正弦波,看起来完全不像方波。

算一算:保留到几次谐波能还原多少“能量”?

把上式前面的 当成常数,只看每一项的 能量比例:

对正弦波,能量 ∝ 幅度²

所以第 个奇谐波的能量 ∝

所有奇次谐波的总能量为:

逐步累加看看:

只保留基波(1 次):

只有基波时,已经包含了大约 81% 的总能量,但波形还是明显是正弦,不“方”。

保留 1 次 + 3 次谐波:

到 3 次谐波,已经恢复了 90% 的能量,波形边缘开始变方,顶端开始变平。

保留 1、3、5 次谐波:

加到 5 次谐波,能量 ~**93%**,波形在示波器上已经“很像方波”了——边缘够陡、顶部够平,剩下的是 Gibbs 振铃、细节毛刺。

继续往上:到 7 次约 95%,到 9 次约 96%

也就是说:

从“波形长相”的角度,3~5 次谐波已经贡献了大部分“方”的感觉,再往上的谐波更多是在修细节。

和带宽、上升沿的关系

如果方波基频是 ,把带宽做到第 个奇次谐波:

常用经验公式:

所以:

只留基波:BW ≈ ,上升沿时间和周期同量级 → 完全不像方波;

保留到 3 次谐波:BW ≈ 3 → 上升沿大约是周期的几分之一;

保留到 5 次谐波:BW ≈ 5 → 上升沿更陡、波顶更平,看起来已“很方”。

我才会说那句话:

“要看上去像方波,至少要有到 3~5 次谐波 的带宽。”

背后就是上面这两个事实一起作用:能量 90~93% 已经被包含;带宽够大,上升沿和周期比值足够小,看起来就“方”了。

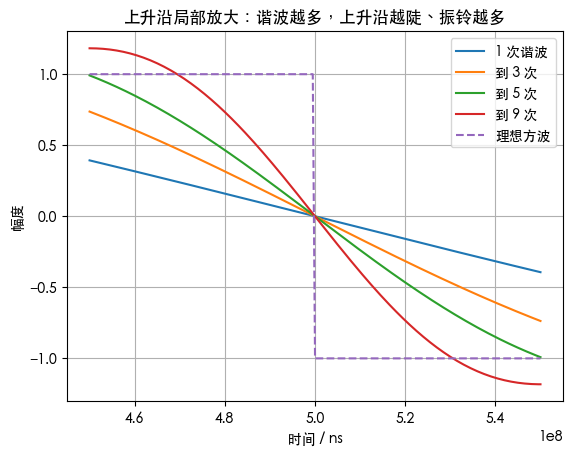

一个周期内,谐波越多,波形越“方”

一个周期内,谐波越多,波形越“方”

设定:

周期 的 1GHz 方波;

用傅里叶级数部分和重建波形:

只保留 1 次谐波(1GHz)

保留到 3 次谐波(1、3GHz)

保留到 5 次谐波(1、3、5GHz)

保留到 9 次谐波(1…9GHz 的所有奇次)

外加一个真正的“理想方波”做对比。

可以看到:

只要基波(蓝线):完全就是一条正弦,根本不像方波。

到 3 次谐波(橙线):波顶已经开始变平,上下有点接近矩形。

到 5 次谐波(绿线):波顶更平,波形轮廓几乎和理想方波重合,只是边缘有一点振铃。

到 9 次谐波(红线):轮廓几乎和理想方波重叠,只是在边缘附近出现更明显的 Gibbs 振铃。

从“我们在示波器上看波形”的角度,带宽做到基波的 5 倍左右,眼睛看到的波形已经非常“方”了,再往上基本是修饰边缘细节。

放大看上升沿——谐波=边缘“刀锋度”

放大看上升沿——谐波=边缘“刀锋度”

第二张图把时间轴放大到一个上升沿附近(大约 0.45T~0.55T):

基波:上升过渡非常圆滑,几乎就是半个正弦;

到 3 次谐波:过渡变得陡峭,已经有“台阶边缘”的感觉;

到 5 次谐波:上升沿近似直线,“刀锋感”明显增强;

到 9 次谐波:边缘更陡,但同时出现明显的振铃 overshoot/undershoot。

这也呼应工程经验:

带宽越高,上升沿越陡,看起来越“方”;但谐波太多、带宽太高时,现实系统中更容易出现过冲/振铃,实际上并不一定“更好”。

回到上面那个 10ps 问题,再算得更具体一点

假设要的是类似“重复的方波脉冲”,脉宽 = 10ps;如果占空比差不多 50%,那周期就是 20ps,对应 50GHz 基波;

基波:50GHz

3 次谐波:150GHz

5 次谐波:250GHz

这就解释了为什么我刚才说:

要“看得像 10ps 方波”,系统得有个三四十 GHz 甚至更高的等效带宽,如果按“基波 5 倍”来算,可能要到 100GHz 量级。

当然,现实中未必需要这么极端——如果可以接受:只需要看“10ps 级上升沿”,不一定是严谨的 10ps 脉宽;或者波形像“扁正弦”而不是标准方波;

那就可以回退到我们之前那条常规公式:

例如想做到 20ps 上升沿:

再结合“5× 基波”这个谐波观点,可以很快评估:带宽只有 3GHz 的放大器 → 实际能展示的最快上升沿 ~100ps 量级;带宽 10GHz → 最快上升沿 ~35ps 左右;要到 10ps 级,就要 35GHz+ 以上。

后记

也难怪大家有时候给的需求离谱,可能是真的不懂。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-11-27,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录