SiliconMotion:基于PCIe5.0的客户端SSD

SiliconMotion:基于PCIe5.0的客户端SSD

数据存储前沿技术

发布于 2025-02-11 16:49:11

发布于 2025-02-11 16:49:11

按:SSD主控厂商PR材料,偏解决方案介绍,从中可一窥先进存储主控的性能和发展方向。

关键要点

- 1. PCIe Gen5 SSD将很快超越PC OEM SSD

- 2. 高性能存储带宽的需求不断增长

- 3. SM2508采用四核Cortex-R8 CPU,具有更高的速度和效率

- 4. SM2508优化了内存控制器设计以降低延迟并减少对高带宽内存的需求

- 5. SM2508采用低功耗架构,可实现最佳性能和功率平衡

• PCIe第四代SSD在推出后不久就压倒了PC OEM SSD。相信第五代SSD将遵循同样的路径。

• 对存储带宽的追求永不停止。在当前平台中,存储继续发挥着重要作用,例如快速数据访问、作为DRAM缓存、“直接存储API”等……所有这些应用都需要高性能SSD。

SiliconMotion SMI首款PCIe第五代客户端SSD控制器。

高性能 • 顺序读取可以达到PCIe第五代x4带宽饱和,最高可达15GB/秒 • 随机读写高达250万IOPS。

低功耗 • 激活模式下最大3.5瓦 • 状态PS4下2.5毫瓦。

灵活的外围接口 • 平台弹性支持 • 升级设计。

高性能的客户端SSD有助于端侧和PC场景的AI推理落地。

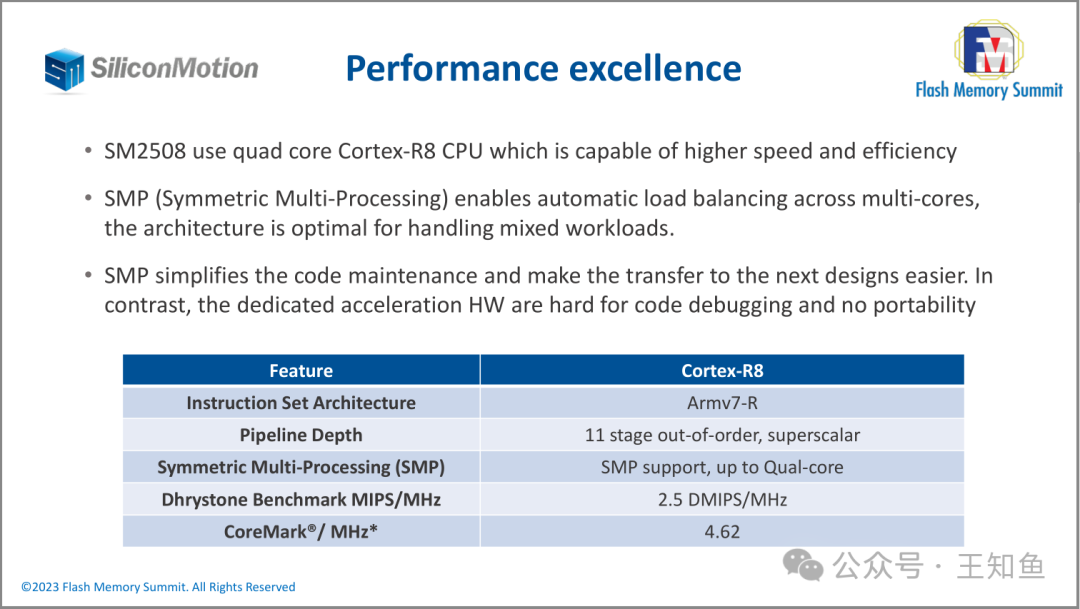

介绍了SM2508使用的处理器核心类型及其优势。SM2508采用了四核Cortex-R8 CPU,具有高性能和高效率的特点。SMP(对称多处理)使得多核之间能够自动均衡负载,适合处理混合型的工作负载。

此外,SMP也简化了代码维护,方便未来的设计转移。表格部分列出了Cortex-R8的一些关键特性,包括它的指令集架构、管道深度、对SMP的支持程度、Dhrystone基准测试结果以及CoreMark评分。

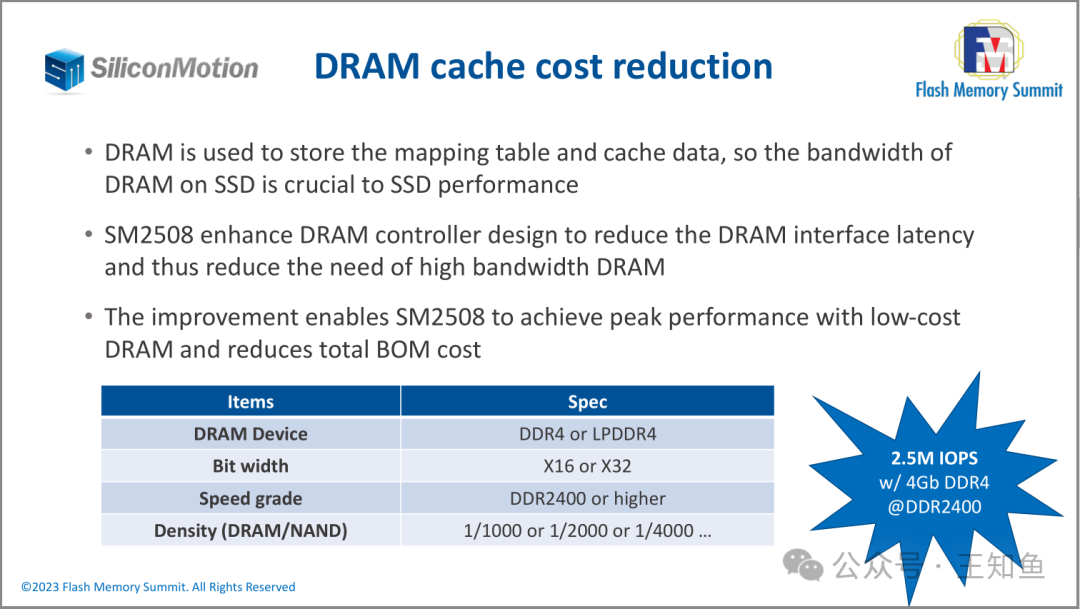

DRAM用于存储映射表和缓存数据,因此SSD上的DRAM带宽对SSD性能至关重要。

增强了DRAM控制器设计以减少DRAM接口延迟,并且减少了对高带宽DRAM的需求。

控制器内的DRAM使用的是DDR4,因为是客户端SSD,故标准传输速率并不高,服务器DDR4的速率能到3200-4800。

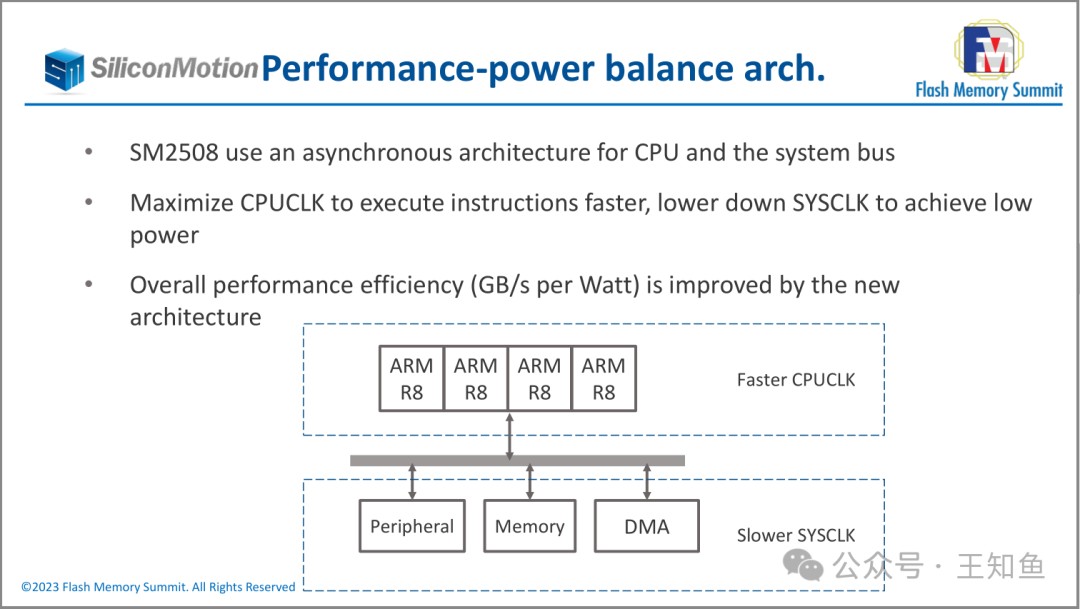

通过优化控制器模组设计,将高主频的CPUCLK和低速率模块分开供电,从而降低能耗,获得更高的性能效率 GB/s/w。

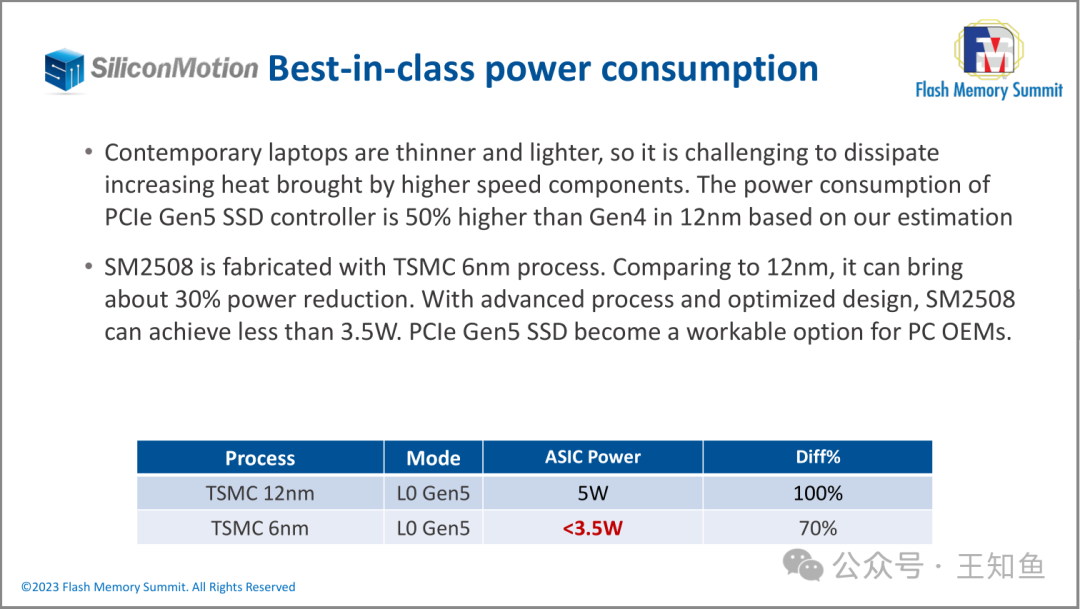

通过采用台积电6纳米工艺来降低功耗,使其在同类产品中拥有较低的功耗水平。相比于12纳米工艺,SM2508可以降低约30%的功耗,使得PCIe Gen5 SSD成为PC原始设备制造商的一个可行选择。

图表还对比了两种不同工艺下的ASIC功耗差异,其中台积电12纳米工艺的L0 Gen5模式功耗为5瓦特,而台积电6纳米工艺的L0 Gen5模式功耗不足3.5瓦特。

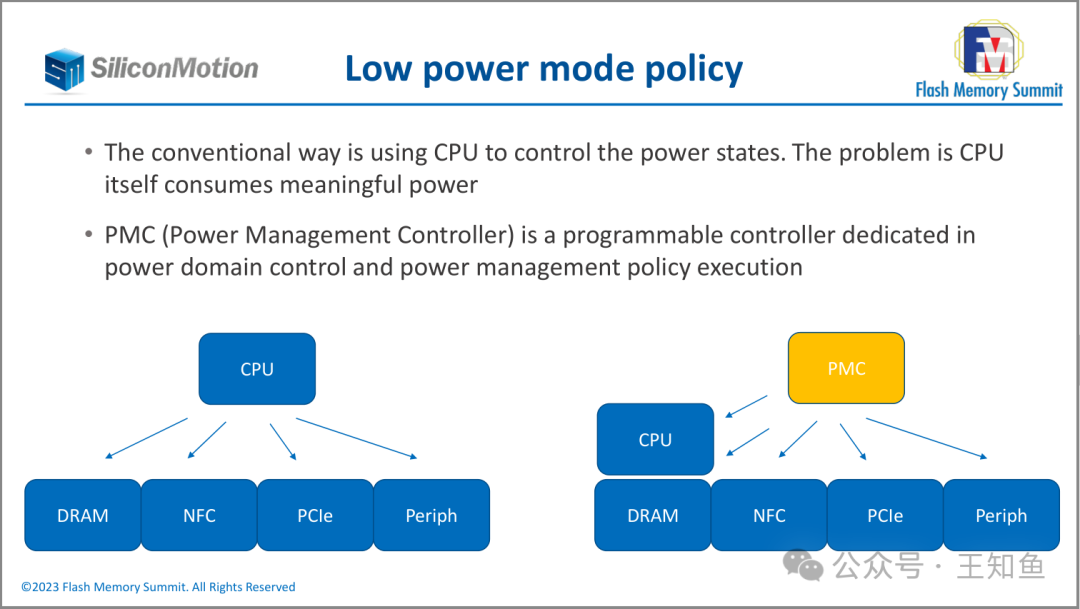

展示了传统的电源管理模式和新的电源管理模式的区别。传统的电源管理模式下,CPU负责控制所有硬件的电源状态,但是这样会导致CPU自身消耗大量电力。新的电源管理模式引入了PMC(电源管理控制器),它是一个专门用于电源域控制和电源管理策略执行的可编程控制器,从而降低整个系统的功耗。

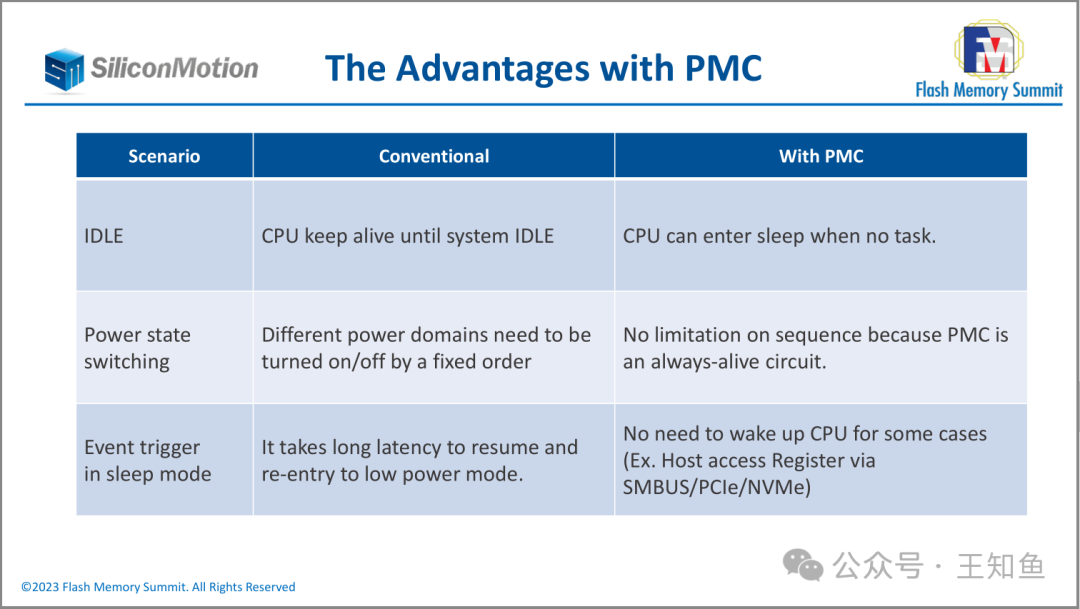

场景 | 传统方式 | 使用PMC |

|---|---|---|

空闲状态 | CPU保持活动,直到系统空闲 | CPU在没有任务时可以进入睡眠 |

电源状态切换 | 不同的电源域需要按照固定顺序开关 | 没有顺序限制,因为PMC是一个始终保持活动的电路 |

睡眠模式下的事件触发 | 恢复和重新进入低功耗模式需要较长的延迟 | 在某些情况下无需唤醒CPU(例如,通过SMBUS/PciE/NVMe访问寄存器) |

展示了使用PMC(电源管理控制器)相较于传统方法在不同场景中的优势。PMC允许CPU在空闲时进入睡眠状态,简化了电源状态切换过程,并减少了在睡眠模式下事件触发时的延迟。这使得系统在功耗管理和响应速度上表现更佳。

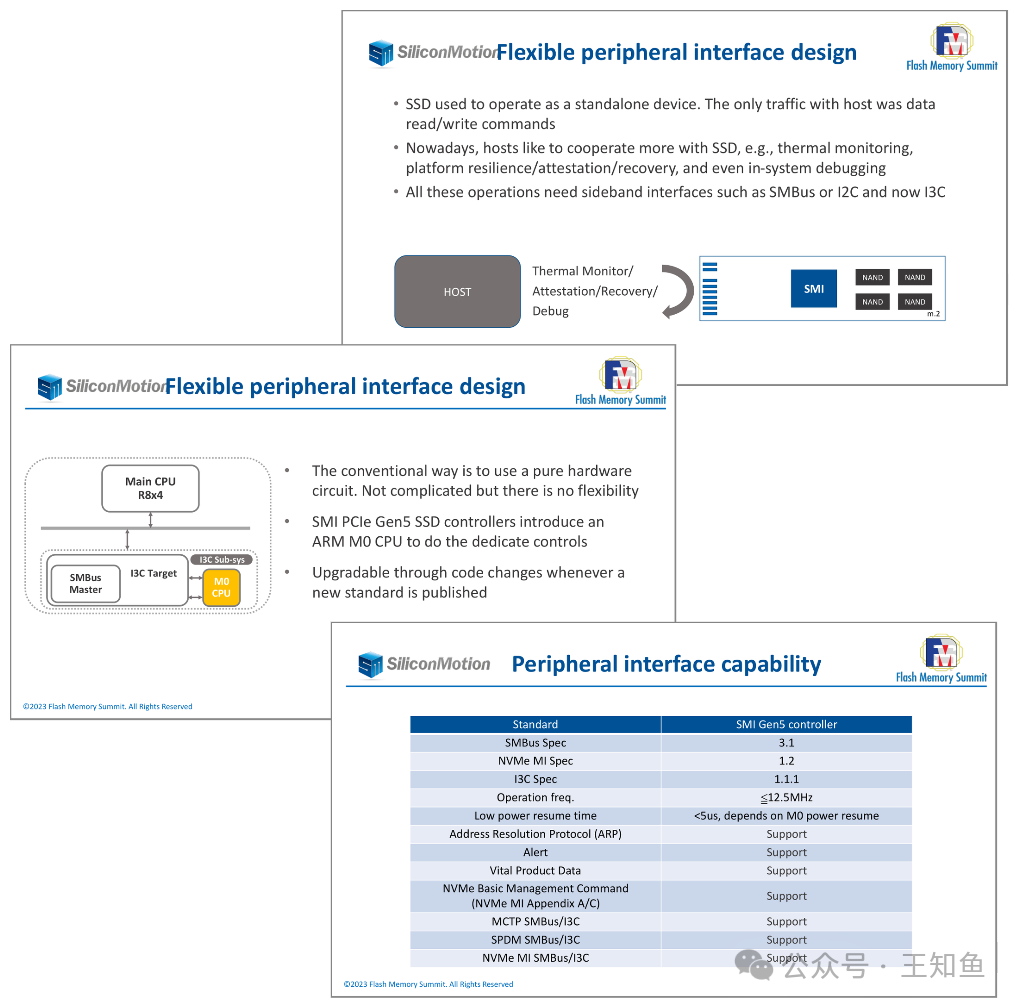

- • SSD曾作为独立设备运作。与主机的唯一通信是数据读/写命令。

- • 如今,主机希望与SSD进行更多交互,例如热监测、平台弹性/认证/恢复,甚至系统内调试。

- • 所有这些操作需要侧带接口,如SMBus、I2C,现在还有I3C。

• 传统的方法是使用纯硬件电路。不复杂,但没有灵活性。

• SMI PCIe Gen5 SSD控制器引入ARM M0 CPU来进行专用控制 。

• 新标准发布时可以通过代码更改升级 主CPU R8x4 SMBus主控 I3C目标 I3C子系统 M0 CPU。

总结

SM2508 特点:

高性能:顺序读取可饱和 PCIe 第五代 x4 带宽,接近15GB/s,随机读写达 250 万 IOPS。

低功耗:激活模式下最大功耗为 3.5W,PS4 状态下为 2.5mW。

灵活接口:支持平台弹性和升级设计。

DRAM 优化:减少 DRAM 接口延迟,降低总 BOM 成本。

创新点:

四核 Cortex-R8 CPU:提供高性能与高效率。

SMP 技术:实现自动负载平衡,适合混合工作负载。

优化设计:降低能耗,提高性能效率。

PMC 引入:简化电源状态切换,降低延迟与系统功耗。

---【本文完】---

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-08-20,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录