使用Verdi的小技巧(六)

灵活控制 Lib Cell 的显示方式

在数字集成电路设计中,成熟的设计团队都会提供大量经过验证、可以可靠复用的模块,以便新的设计可以最大程度通过搭积木的方式进行,一方面是节省人力和时间,另一方面是避免引入错误。

通常这些复用模块是以 library cell 的方式出现在文件列表中。

-v ./share_ip/sync_2dff.v

-y ./share_ip当整个设计读入 Verdi 时,Verdi 也会默认折叠这些 libraray cell,以方便查看真正关心的新设计的模块。

如果复用模块以普通模块的形式被文件列表引用,那么 Verdi 中会显示巨大数量的实例,从而干扰工程师的专注。大家可以想象一下,如果某个子系统的顶层,含有几千个类似两级触发器同步模块,在 Verdi 中想找到感兴趣的模块就非常的麻烦了。

当然,凡事皆有例外,在有些特殊的场景下,我们希望某些 library cell 以普通模块的方式在 Verdi 中显示,以方便我们去查看。这个时候就可以用下列的 Verdi 选项来改变工具的默认行为。

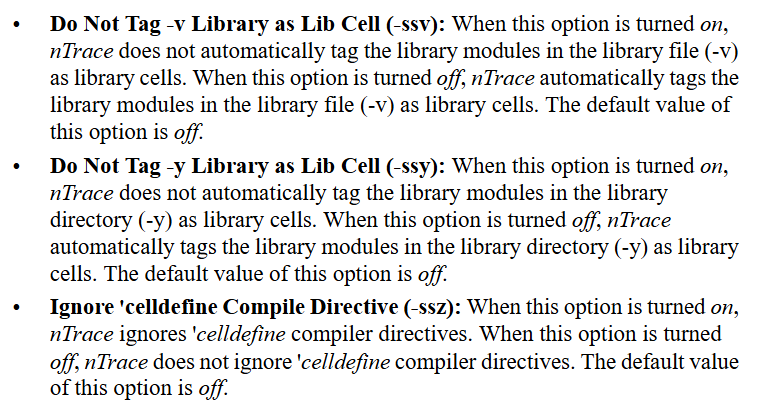

-ssv

-ssy

-ssz详细的解释如下。

统计 Cycle 数量

这个系列之前的文章曾经提到过一些统计信号的小技巧,最近学习到一种简洁有效的好办法,分享给大家。

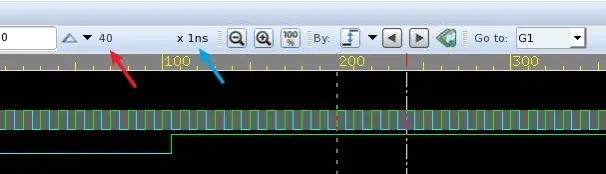

经常使用 Verdi 的读者朋友们,菜单上的这两部分想必非常熟悉,红色箭头所指是波形中两个默认 Marker 之间的时间差,蓝色箭头所指是时间单位。

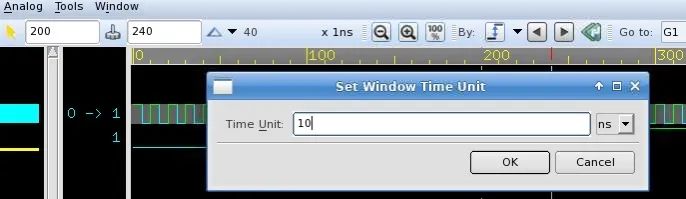

说到时间单位,固有思维中一般是以一为单位,但实际可以是任意的数字。那么通过改变时间单位为时钟周期的时间间隔,其实就可以很方便的应用于一些需要统计时钟周期个数的场合。

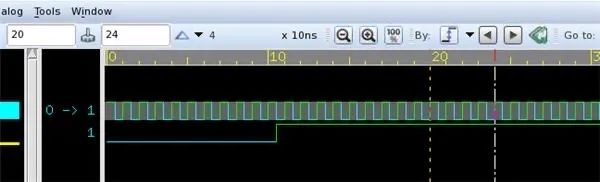

比如下图中,时间单位更改为10ns,正好对应时钟周期,那么改变两个 Marker 的位置,就可以很直观地读出它们之间相隔多少个时钟。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-03-08,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录