静态时序分析

静态时序分析介绍

传统的电路设计分析方法是仅仅采用动态仿真的方法来验证设计的正确性。随着集成电路的发展,这一验证方法就成为了大规模复杂的设计验证时的瓶颈。

相对于动态仿真方法,静态时序分析方法要快很多,而且它能够验证所有的门级电路设计的时序关系。

静态时序分析最大的特点是不需要加入输入测试向量,每一个时序路径都自动被检测到。

静态时序分析工具主要对设计电路中以下路径进行分析:

- 从原始输入端到设计电路中的所有触发器;

- 从触发器到触发器;

- 从触发器到设计电路的原始输出端口;

- 从设计电路的原始输入端口到原始输出端口。

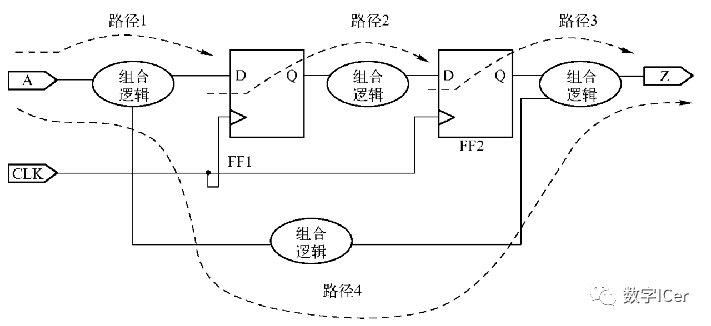

时序路径(Timing Path)

- 路径1:从设计电路的原始输入端口A到触发器的数据端口D。

- 路径2:从触发器的CLK端到触发器的数据输入端口D。

- 路径3:从触发器的CLK端到设计电路的原始输出端口Z。

- 路径4:从设计电路的原始输入端口A到设计电路的原始输出端口Z。

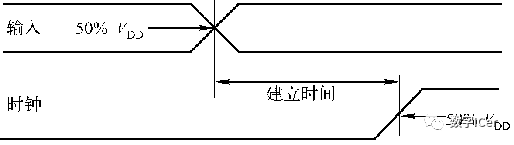

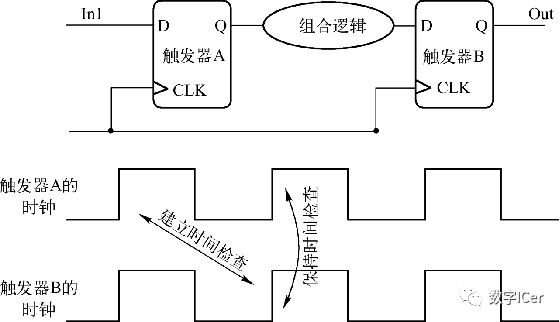

触发器的建立时间(Setup Time):

指的是时钟信号变化之前数据保持不变的时间

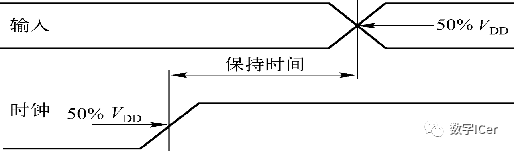

触发器的保持时间(Hold Time):

指的是时钟信号变化之后数据保持不变的时间

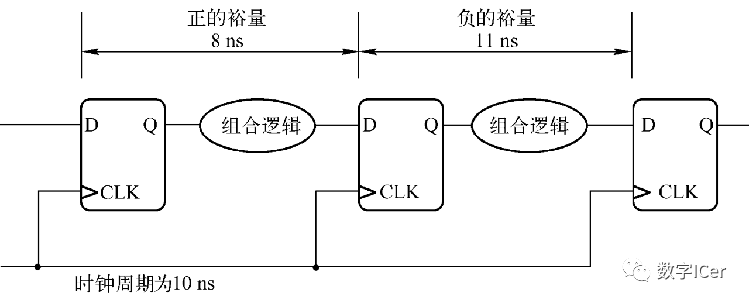

时间裕量(Slack)

Slack是指信号在时序路径上要求的时间和实际花费的时间之差。

时钟偏斜(Clock Skew)

时钟偏斜是指从时钟定义点到不同触发器时钟引脚的延时差。在可综合的同步设计电路中,在一个时钟沿第一个触发器放出数据,此数据在另一个时钟沿(通常是接下来的那个时钟沿)被第二个触发器接收到。如果这两个时钟沿(发出数据的时钟沿和接收数据的时钟沿)是同一个时钟源放出的,则在理想状态下,两个时钟沿相差一个时钟周期。但是由于两个触发器的时钟路径的不同,路径上的延时会有一定的差别,接收数据的时钟沿可能早到或晚到,这样的话就会产生时钟偏斜。

更多请查看 :

PTPX功耗分析 | Average Power Analysis PTPX功耗分析 | Peak Power Analysis

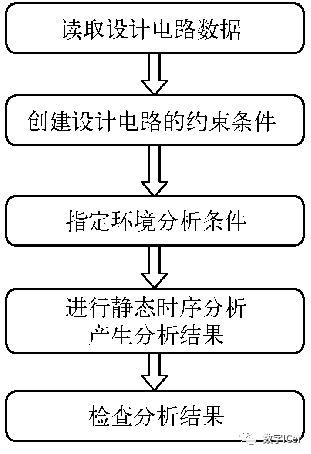

实例:用PrimeTime进行时序分析

Primetime,缩写为PT,是一个独立的STA工具。它不仅能够在设计电路所要求的约束条件下检查时序,还能对设计电路进行全面的静态时序分析。

(1)读取设计电路数据

把电路的设计代码文件读入PT中,以便PT进行分析。值得注意的是,PT做静态时序分析的时候只能读映射过的文件。

read_db -netlist_only <design name>.db #db format

read_verilog <design name>.sv #verilog format

read_vhdl <design name>.svhd #vhdl format

read_edif <design name>.edf #EDIF format

(2)创建设计电路的约束条件

对设计电路设置约束条件,这样才能得到接近实际情况的分析结果。通常需要设置相关的时钟信号和输入/输出延时

create_clock -period 40 -waveform {0 20} CLK

set_clock_latency -source 0.2 CLK

set_clock_uncertainty -setup 0.5 -hold 0.5 CLK

set_dont_touch_network CLK

set_ideal_network CLK

(3)指定环境分析条件

除了一些语法上轻微的差别,PT的环境的设置命令与DC一致。

下面是常用的设置环境的命令:

set_wire_load_model -name <wire-load model name>

set_wire_load_mode < top | enclosed | segmented>

set_operating_conditions <operating conditions name>

set_load 50[all_outputs]

set_input_delay 10.0 -clock <clock name>[all_inputs]

set_output_delay 10.0 -clock <clock name>[all_outputs]

(4)进行静态时序分析

report_timing:显示时序路径信息。 report_timing -delay max -from a -to z2 report_timing -delay min -from a -to z2

上述第一条命令用于建立时间冲突的检查,第二条命令用于保持时间冲突的检查。

report_constraint:显示设计电路的相关约束信息。 report_constraint -all_violators

检查时序冲突和修正冲突

由于静态时序工具把整个设计电路打散成时序路径,分析不同路径的时序信息,得到建立时间和保持时间的计算结果。而静态时序分析的精髓就在于判断和分析这两个参数的结果。

消除建立、保持时间的冲突方法

消除建立时间的冲突方法如下:

- 加强约束条件重新综合设计电路或对产生冲突的时序路径进行进一步的优化;

- 通过做ECO(Engineering Change Order)来消除冲突;

- 如果以上方法都不能产生效果,那可能只好通过修改RTL代码来实现。

消除保持时间冲突方法如下:

- 绝大多数的布局布线工具都具有自动消除保持时间冲突的功能,可以通过这些工具来实现;

- 如果工具不能实现的话,可以在产生冲突的时序路径上通过ECO添加缓冲器逻辑,使得数据到达的时间符合保持时间的检查,以此消除冲突。

统计静态时序分析

静态时序分析很久以来都被看作是百万门级芯片时序分析的基本方法及设计完成的检验。然而,随着深亚微米技术进一步下降到90 nm及其以下的线宽,设计者在进行静态时序分析时面临着太多的不确定性。

用统计表态时序分析(SSTA,Statistical Static Timing Analysis)的方法有可能估计出许多不确定的现象,帮助设计者精调设计,减少不必要的过度设计,使得设计更可靠,进而提高良率。

传统的时序分析的局限

制程变异的来源有很多,主要包括每批晶圆的差异、晶圆与晶圆间的差异、裸片间的差异,以及裸片上的差异等。

将电路置于最好条件(Best Case)、最坏条件(Worst Case)等多种情况下进行分析,但是对于晶片上的制程变异却无能为力。因为在最坏条件分析时,静态时序分析总是假定一个晶圆上的电路同时都处于最坏情况下,而实际上,同一个晶圆上的电路不可能同时都处于最坏的条件下(这可由分析版图或者工艺得来)。

在一个芯片上不同位置上画了两个完全一样的MOS管,制造出来后,两只MOS管的性能很难保证完全一样。当工艺在90 nm以下时,误差会高达20%~30%。传统式的静态时序分析是将芯片上所有器件按同一个工艺及工作条件下的时间路径上的延时加起来,因而传统式的静态时序分析对于延迟的估计过于悲观。

统计静态时序分析的概念

在静态时序分析中,信号的到达时间和门延迟都是确定的数值。

在统计静态时序分析中,当工艺参数的偏差用随机变量建模后,作为工艺参数函数的门延迟、互连线延迟和门输入端信号的到达时间自然也需要用带有概率分布的随机变量来描述。

统计静态时序分析的步骤

首先,要有用于统计静态时序分析的标准单元库。

通过统计静态时序分析,找出合适的时序窗(Timing Window),在此窗中,良率可以达到最高。

总之,统计静态时序分析通过对制程变异进行恰当的建模,更好地解决了延迟的不确定性问题,避免了过度的余量,提高了设计的性能及制造的良品率。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2022-11-27,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读