SD NAND 为何不能存启动代码,SPI NAND 与 NOR Flash 却可以 —— 接口、传输、启动机制全对比

原创SD NAND 为何不能存启动代码,SPI NAND 与 NOR Flash 却可以 —— 接口、传输、启动机制全对比

原创

杭州瀚海微

发布于 2026-02-09 11:19:52

发布于 2026-02-09 11:19:52

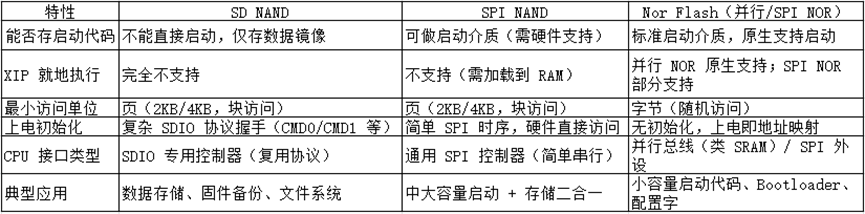

在嵌入式、物联网、工控、车载等硬件系统中,启动存储器(Boot Flash) 是决定设备能否上电即跑、稳定可靠的核心器件。实际选型中,SD NAND、SPI NAND、NOR Flash 是常见的非易失性存储方案,但业界有一条明确共识:SD NAND 几乎不用于存放启动代码,而 SPI NAND 和 NOR Flash 是主流启动介质。

这一差异并非单纯成本或容量问题,而是由接口协议、CPU 访问机制、XIP 能力、初始化流程、传输方式、可靠性设计共同决定。本文从启动原理、数据传输、硬件交互、优劣势及场景适配四个维度,完整拆解三类存储的核心区别,帮你彻底理解启动存储的选型逻辑。

一、先搞懂:嵌入式设备「启动」的核心硬件要求

设备上电后,CPU/MCU 要完成复位、取指、执行,对启动存储有 4 个刚性要求,缺一不可:

1. 上电即访问,无复杂前置初始化:CPU 刚复位时,时钟、外设、驱动均未配置,存储必须能被硬件直接寻址读取,无需软件协议握手、状态机配置。

2. 支持 XIP(eXecute-In-Place,就地执行):代码可直接在 Flash 中运行,无需先搬运到 RAM,满足极小体积 BootROM、片上 RAM 不足的场景。

3. 字节级 / 任意地址随机读取:CPU 取指是单字节 / 指令级随机跳转,不允许仅支持块 / 页批量读取。

4. 低延迟、时序确定、无坏块 / FTL 依赖:启动阶段无错误处理、坏块管理、ECC 校验软件,存储必须保证地址稳定、读取可靠。

满足以上条件,才能作为一级启动介质(存放 Bootloader、第一阶段启动代码);不满足则只能作为数据存储 / 二级镜像存储(如系统固件、文件、日志)。

二、核心结论先行:三类存储的启动能力本质差异

下面从接口与传输方式、启动限制、优劣势逐层拆解。

三、SD NAND:为什么不适合存放启动代码

SD NAND 本质是封装成 SD 形态的 NAND Flash 裸片,内置 SD 控制器,对外遵循 SDIO 协议,看似引脚少、易用,但违背启动存储的硬件规则。

1. SD NAND 数据传输与接口机制

· 接口:SDIO 总线(CMD + DAT0~3 + CLK)

属于主机 - 从机协议型接口,不是简单的地址 / 数据总线,必须由主机 SD 控制器发送标准命令交互:

1. 上电发送 CMD0 软复位

2. CMD1 / CMD8 做电压识别、卡初始化

3. CMD9/CMD10 获取 CID/CSD 配置

4. 读数据必须用 CMD17(单块读)+ 地址 + 等待响应 + 整页传输

· 传输方式:半双工、块 / 页为最小单位

o 不支持单字节随机读,只能整页(2KB/4KB)读写

o 读写必须经过命令 - 响应 - 数据三步握手,延迟高、时序不确定

o 数据方向切换需重新配置总线,无法像总线一样随时取指

2. 三大问题:无法承担启动职责

1. 无 XIP,完全不能就地执行

CPU 无法直接从 SD NAND 取指,必须先通过驱动把整页数据搬到 RAM,再从 RAM 执行。但启动初期无驱动、无 RAM 初始化,陷入 “先有鸡还是先有蛋” 死循环。

2. 依赖 SD 控制器与软件协议,上电不可直接访问

SDIO 是复杂高速协议,需要时钟配置、相位校准、状态机切换,纯硬件无法自动完成初始化,必须软件参与,而上电第一步就是取指,不可能先运行驱动。

3. 内置 FTL、坏块、ECC,启动阶段不可控

SD NAND 为兼容存储卡场景,内置损耗均衡、坏块替换、ECC 校验,逻辑地址与物理地址映射不透明,启动代码不能跨块跳转、地址不稳定,极易出现上电读失败、指令错乱。

3. SD NAND 优劣势总结

· 优势:容量大(Gb 级)、价格低、引脚少、兼容标准 SD 卡槽、易用性高、适合大容量数据存储

· 劣势:无 XIP、协议复杂、上电不可用、可靠性不满足启动、仅做数据存储

· 定位:数据盘、固件备份、日志、文件系统,绝对不参与一级启动

四、SPI NAND:可以启动,但本质是「加载型启动」

SPI NAND 是NAND Flash 裸片 + SPI 接口转换,对外是标准 SPI(CS/CLK/MOSI/MISO),保留 NAND 大容量低成本特性,同时解决了 SD NAND 的协议壁垒。

1. SPI NAND 数据传输与接口机制

· 接口:标准 SPI / QSPI / Octal SPI

通用同步串行接口,无复杂协议命令集,仅靠片选、时钟、移位完成通信,MCU 通用 SPI 控制器即可驱动,无需专用 SDIO。

· 传输方式:串行移位、页访问、指令简单

o 读指令:0x03(慢速)/ 0x0B(快速)+ 3 字节地址 + 串行输出数据

o 最小访问单位仍是页(2KB/4KB),不支持真正字节随机读

o 全双工 / 半双工串行,速度由时钟决定,支持四线 / 八线提速

2. 为什么 SPI NAND 可以存启动代码?

1. 上电硬件直接访问,无需软件协议初始化

SPI 时序简单,MCU 硬件 BootROM 可直接控制 SPI 时序,不需要发送复杂 SD 命令,上电即可发送读指令。

2. MCU 硬件支持「SPI 启动加载机制」

主流 MCU(STM32、ESP32、RV1106、全志、瑞芯微)内置 BootROM,硬件实现:

o 上电自动配置 SPI 时钟

o 发送读指令,从固定地址读取小体积 Bootloader(如 4KB/8KB)

o 硬件直接搬运到片内 SRAM,再跳转到 SRAM 执行

3. 虽无 XIP,但满足「一级启动加载」需求

SPI NAND 本身不支持 XIP,但硬件加载流程固化在 BootROM,属于「硬件预加载 → RAM 执行」,完美避开软件依赖,实现可靠启动。

优劣势总结

· 优势:容量大(1Gb~8Gb+)、成本低、引脚极少(4~10 脚)、兼容通用 SPI、支持硬件启动、适合中大容量启动 + 存储

· 劣势:无 XIP、页访问、随机读取慢、擦除以块为单位、需依赖 MCU BootROM 适配

· 定位:主流低成本大容量启动介质(IoT、机顶盒、屏驱、工控)

五、NOR Flash:真正原生支持启动,XIP 王者

NOR Flash 是最早为代码存储设计的非易失存储,架构最接近 SRAM,是启动最稳定、最通用的方案,分并行 NOR(传统)和 SPI NOR(主流小容量)。

1. NOR Flash 数据传输与接口机制

(1)并行 NOR(经典启动架构)

· 总线结构:独立地址线 + 数据线 + 控制信号(CE/OE/WE)

与 CPU 总线直连,地址直接映射,完全等同于访问静态内存。

· 传输方式:并行同步 / 异步、字节级随机读取

o 最小单位:字节(8bit)

o 任意地址直接读,无命令握手、无页等待

o 读取延迟 ns~us 级,完全匹配 CPU 取指速度

(2)SPI NOR(当前小容量主流)

· 接口:SPI/QSPI/Octal SPI

· 传输:串行,但保留字节访问能力

· 优势:支持 XIP(模式 - 0 / 模式 - 3),CPU 可直接在 Flash 上执行代码,无需搬运到 RAM

2. 为什么 NOR Flash 是最理想的启动介质?

1. 原生支持 XIP,上电即执行

无需加载到 RAM,CPU 直接取指运行,BootROM 极小即可启动,适合裸机、RTOS、极简系统。

2. 无复杂初始化,总线直接映射

并行 NOR 上电即被 CPU 寻址;SPI NOR 由硬件自动配置时序,无协议依赖、无软件参与。

3. 字节级随机读取、低延迟、稳定可靠

无页访问、无坏块设计(工业级极少坏块)、无 FTL、地址固定,完全满足启动代码频繁跳转、随机访问需求。

3. NOR Flash 优劣势总结

· 优势:支持 XIP、字节随机读、启动最稳定、延迟最低、兼容性最广、全场景通用

· 劣势:容量小(通常 128Mb~2Gb)、价格高、并行 NOR 引脚多、擦除速度慢

· 定位:关键启动代码、Bootloader、配置区、车规 / 工控 / 高可靠场景

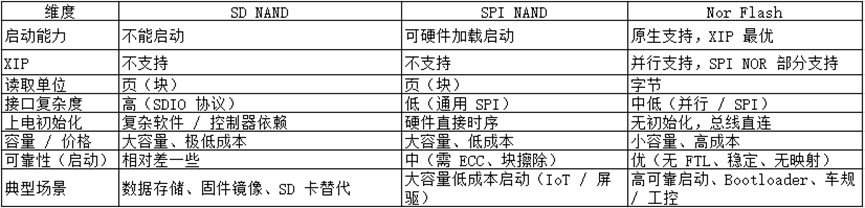

六、终极对比:传输方式与启动能力核心差异(精华总结)

1. 数据传输方式本质区别

· SD NAND(SDIO)

协议型半双工传输 → 命令 - 响应 - 数据块传输 → 页访问 → 不支持随机读 → 必须软件驱动

· SPI NAND(SPI)

串行移位传输 → 指令 + 地址 + 数据帧格式 → 页访问 → 硬件可直接读 → 无 XIP

· NOR Flash(并行 / SPI NOR)

并行总线 / 串行字节访问 → 地址直接映射 → 字节随机读 → 支持 XIP → 上电即取指

2. 启动能力差异根源

1. SD NAND:协议太重、上电不可用、无 XIP、地址不透明 → 不能启动

2. SPI NAND:接口简单、硬件可加载、无 XIP → 可启动(依赖 MCU 硬件加载)

3. NOR Flash:总线直连、XIP、随机读、稳定 → 原生完美启动

3. 三类存储优劣势总表

七、工程选型指南:该用谁?

1. 必须用 NOR Flash

o 车规、医疗、工控、高可靠、低延迟

o 极简系统、无 OS、RTOS、需 XIP

o 启动代码小(< 16MB)

2. 优先用 SD NAND

o IoT、消费电子、机顶盒、智能屏

o 需要大容量(≥ 256MB)+ 启动二合一

o MCU 支持 SPI 启动加载

3. 不用 SD NAND 存启动代码

o 仅用于:数据盘、日志、多媒体、升级固件备份

o 启动必须由 NOR / SPI NAND 负责,SD NAND 只做数据层

八、结语:不是性能问题,是架构定位问题

SD NAND 不能启动,不是速度不够,而是定位为「数据存储设备」,采用 SDIO 协议、块访问、FTL 映射,完全为文件系统与大容量读写设计,违背 CPU 启动的总线级、随机取指、上电即用规则。

SPI NAND 通过简单 SPI 接口 + 硬件 BootROM 加载,折中实现大容量启动;NOR Flash 则以XIP、字节随机读、总线直连,成为最稳定的启动黄金标准。

一句话记住选型本质:

SD NAND 是「盘」,SPI NAND 是「可启动的盘」,NOR Flash 是「真正的启动内存」。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

评论

登录后参与评论

推荐阅读

目录