LVDS、LVPECL、CML 间的互连

原创LVDS、LVPECL、CML 间的互连

原创用户11599900

发布于 2025-09-25 17:36:49

发布于 2025-09-25 17:36:49

在高速数字电路设计中,LVDS(低压差分信号)、LVPECL(低压正射极耦合逻辑)和CML(电流模式逻辑)是三种常见的接口标准。当需要在不同标准的芯片间实现信号互连时,正确的电平匹配和耦合方式至关重要。

本文档将详细探讨这三种标准之间(LVPECL到CML、CML到LVPECL、CML与LVDS)的互连方案,包括交流耦合与直流耦合的具体实现方法。在下面的讨论中,假设采用+3.3V PECL。

1. LVPECL 到 CML 的连接

LVPECL 与 CML 之间的耦合方式可以是交流方式,也可以是直流方式。

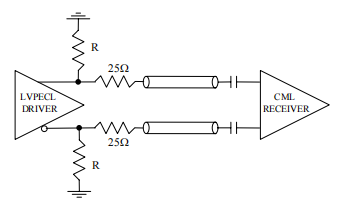

1.1 交流耦合

LVPECL 驱动器到 CML 接收器的一种连接方式就是交流耦合方式,如图 1 所示。在 LVPECL 的两个输出端各加一个到地的直流偏置电阻,电阻值选取范围为 142Ω 至 200Ω。如果 LVPECL 的差分输出信号摆幅大于 CML 的接收范围,可以在信号通道上串一个 25Ω 的电阻,以提供 0.67 倍的电压衰减。

图 1. LVPECL 与 CML 之间的交流耦合

1.2直流耦合

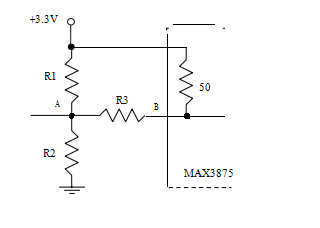

在 LVPECL 到 CML 的直流耦合连接方式中需要一个电平转换网络,以满足 LVPECL 输出与CML 输入的共模电压要求。该电平转换网络引入的损耗必须要小,CML 接收器输入端的信号摆幅大于接收器的灵敏度要求。另外还要求自LVPECL 输出端看到的总阻抗近似为 50Ω。下例说明了 LVPECL 输出驱动 MAX3875 CML 输入的情况,电平转换网络如图 2 所示。

图 2. LVPECL 与 CML 之间的电阻网络 (MAX3875)

注:假定 LVPECL 的最小差分输出摆幅为1200mV,而 MAX3875 的输入灵敏度为 50mV, 这样电阻网络的增益必须大于 50mV/1200mV = 0.042。

(4)求解上面的方程组,我们得到 R1 = 182Ω,R2 = 82.5Ω,R3 = 294Ω (标准 1%阻值),VA = 1.35V, VB = 3.11V ,增益 = 0.147 , ZIN = 49Ω 。把

LVPECL 输出与 MAX3875 输入通过该网络连接,实测得:VA = 2.0V,VB = 3.13V。

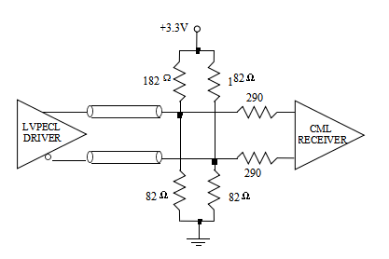

LVPECL 到 MAX3875 的直流耦合结构如图 3 所示。对于其它的 CML 输入,最小共模输入电压和最小输入信号摆幅可能不同,读者可根据上面的考虑计算所需的电阻值。

图 3. LVPECL 与 CML 之间的直流耦合 (MAX3875)

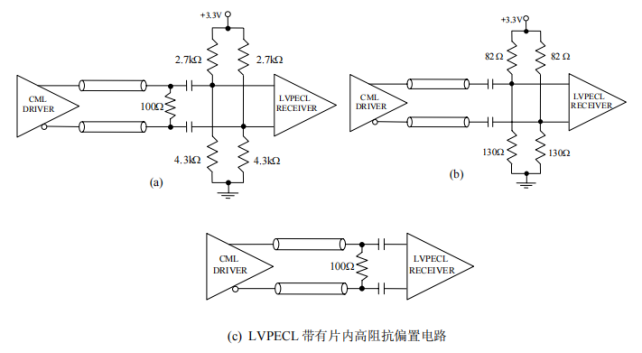

2. CML 到 LVPECL 的连接

CML 与 LVPECL 的连接需采用交流耦合(参见图4)。

图 4. CML 与 LVPECL 之间的交流耦合

3. CML 和 LVDS 间互连

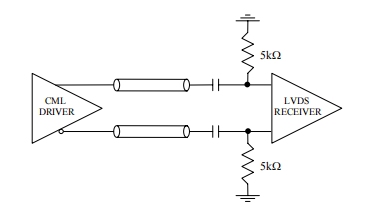

CML 与 LVDS 之间采用交流耦合方式连接(图5)。注意,CML 输出信号摆幅应该在 LVDS 输入能够处理的范围以内。

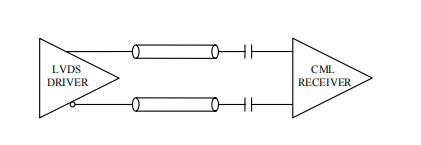

如果 LVDS 驱动器需要驱动一个 CML 接收器, 可以采用图 6 所示的交流耦合方式。

图 5. CML 与 LVDS 之间的交流耦合

图 6. LVDS 与 CML 之间的交流耦合

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

评论

登录后参与评论

推荐阅读