分享!基于NXP i.MX 8M Plus平台的OpenAMP核间通信方案

原创分享!基于NXP i.MX 8M Plus平台的OpenAMP核间通信方案

原创

创龙科技Tronlong

修改于 2025-02-25 14:34:28

修改于 2025-02-25 14:34:28

在嵌入式系统领域,随着技术不断发展,对于系统性能和功能要求日益提高。核间通信作为提升系统整体效能的关键技术,成为了关注焦点。今天,我们和大家分享一个OpenAMP非对称架构核间通信方案,基于NXP i.MX 8M Plus

平台。

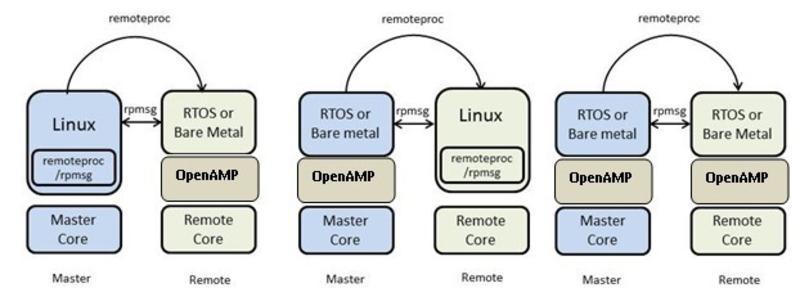

OpenAMP架构

AMP(Asymmetric Multi-Processing),即非对称多处理架构。“非对称AMP”双系统是指多个核心相对独立运行不同的操作系统或裸机应用程序,如Linux + RTOS/裸机,但需一个主核心来控制整个系统以及其它从核心。每个处理器核心相互隔离,拥有属于自己的内存,既可各自独立运行不同的任务,又可多个核心之间进行核间通信。OpenAMP框架是一个提供用于处理非对称多处理架构(AMP)系统的软件组件,为开发者提供了便捷高效的开发工具。

随着对嵌入式系统性能需求的持续攀升,非对称AMP架构凭借其独特优势,成为一种新选择,被广泛应用于工业领域,如工业PLC、继电保护装置、小电流选线设备等场景,为工业自动化和智能化发展提供了强大的技术支持。

图 1

i.MX 8M Plus的OpenAMP开发方案

本案例采用i.MX8M Plus处理器的Cortex-A53核心与Cortex-M7核心,基于RPMsg-lite框架实现高效的核间通信。

Cortex-A53通过加载imx_rpmsg_tty驱动,向内核注册TTY终端设备。这样一来,Linux应用层只需通过访问"/dev/ttyRPMSGxx"设备节点,就能实现间接调用RPMsg-lite接口,与Cortex-M7核心建立通信连接。

系统框图如下图所示。

图 2

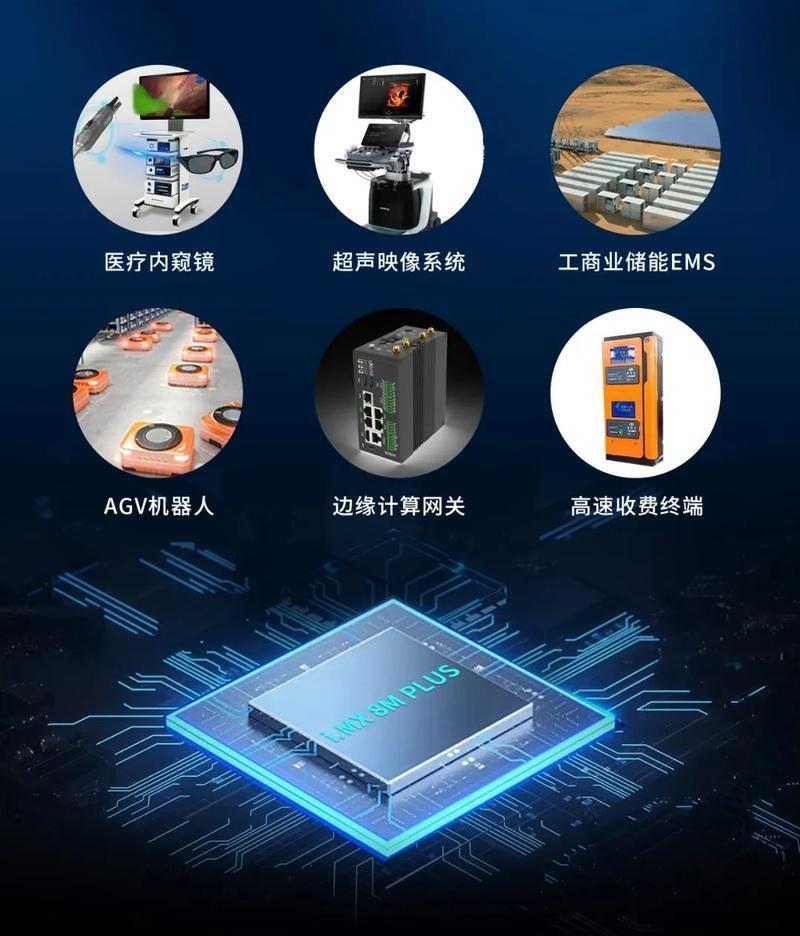

i.MX 8M Plus的典型应用领域

i.MX 8M Plus凭借其强大的性能和出色的兼容性,广泛应用多个领域,为行业提供了有力的硬件支撑。

图 3

OpenAMP开发案例演示

为了简化描述,本文仅摘录部分方案功能描述与测试结果。 开发环境

Windows开发环境:Windows 7 64bit、Windows 10 64bit

虚拟机:VMware15.5.5

Linux开发环境:Ubuntu20.04.6 64bit

U-Boot:U-Boot-2022.04

Kernel:Linux-5.15.71-rt51

SDK开发包:SDK_2_12_0_MIMX8ML8xxxKZ

交叉编译工具链:gcc-arm-none-eabi-10.3-2021.10-x86_64-linux

硬件平台:创龙科技TLIMX8MP-EVM工业评估板(基于NXP i.MX 8M Plus)

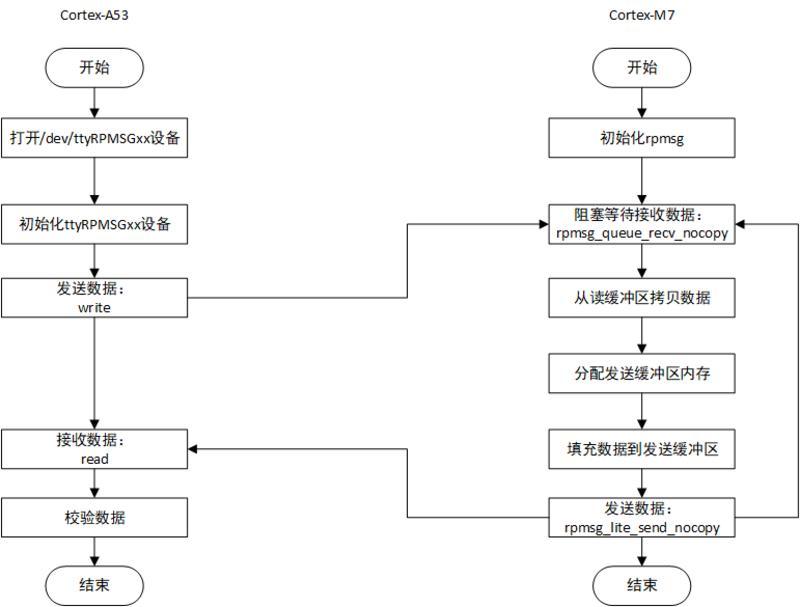

案例功能

本文案例主要通过RPMsg-lite框架演示核间通信。首先,在Cortex-A53核心发送"Tronlong"字符串到Cortex-M7核心,Cortex-M7核心接收到"Tronlong"字符串后,会将此消息回发到Cortex-A53核心,最后,Cortex-A53核心接收并校验消息,确保数据传输的准确性和完整性。

程序原理流程图如下所示:

图 4

案例测试

请使用USB串口线将评估板的USB TO UART2串口连接至PC机的USB接口,使用RS232交叉串口母母线、USB转RS232公头串口线将评估板的RS232 UART4串口连接至PC机的USB接口,如下图所示。

其中USB TO UART2作为Cortex-A53核心调试串口,RS232 UART4作为Cortex-M7核心调试串口。

图 5

参考产品资料进行环境搭建,启动Cortex-M7核心并加载工程镜像,Cortex-M7核心启动后将自动运行程序,加载imx_rpmsg_tty模块,启动核间通信等。

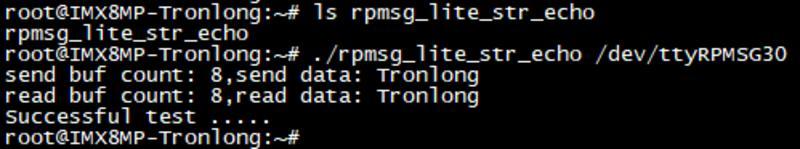

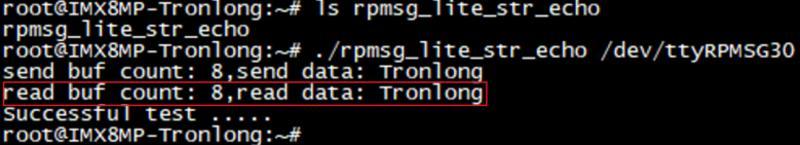

然后将案例rpmsg_lite_str_echo文件拷贝至评估板文件系统,执行如下命令发送数据至Cortex-M7核心。

Target# ./rpmsg_lite_str_echo /dev/ttyRPMSG30

图 6

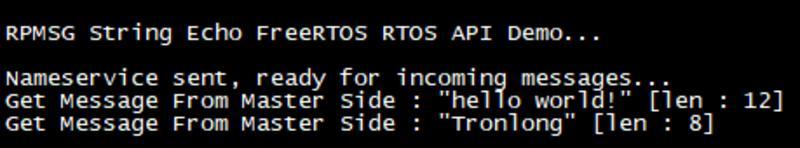

Cortex-M7核心接收到数据后,在RS232 UART4调试串口将数据进行打印,同时将数据回发至Cortex-A53。

图 7

在USB TO UART2调试串口可查看Cortex-M7核心回发的数据。

图 8

如果您还想查看更多i.MX8M Plus相关的案例演示,请通过公众号(Tronlog创龙科技)查阅,亲自上手体验吧!

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

评论

登录后参与评论

推荐阅读

目录