双控开关接入NVBoard

原创导入NVBoard

git仓库:https://github.com/NJU-ProjectN/nvboard

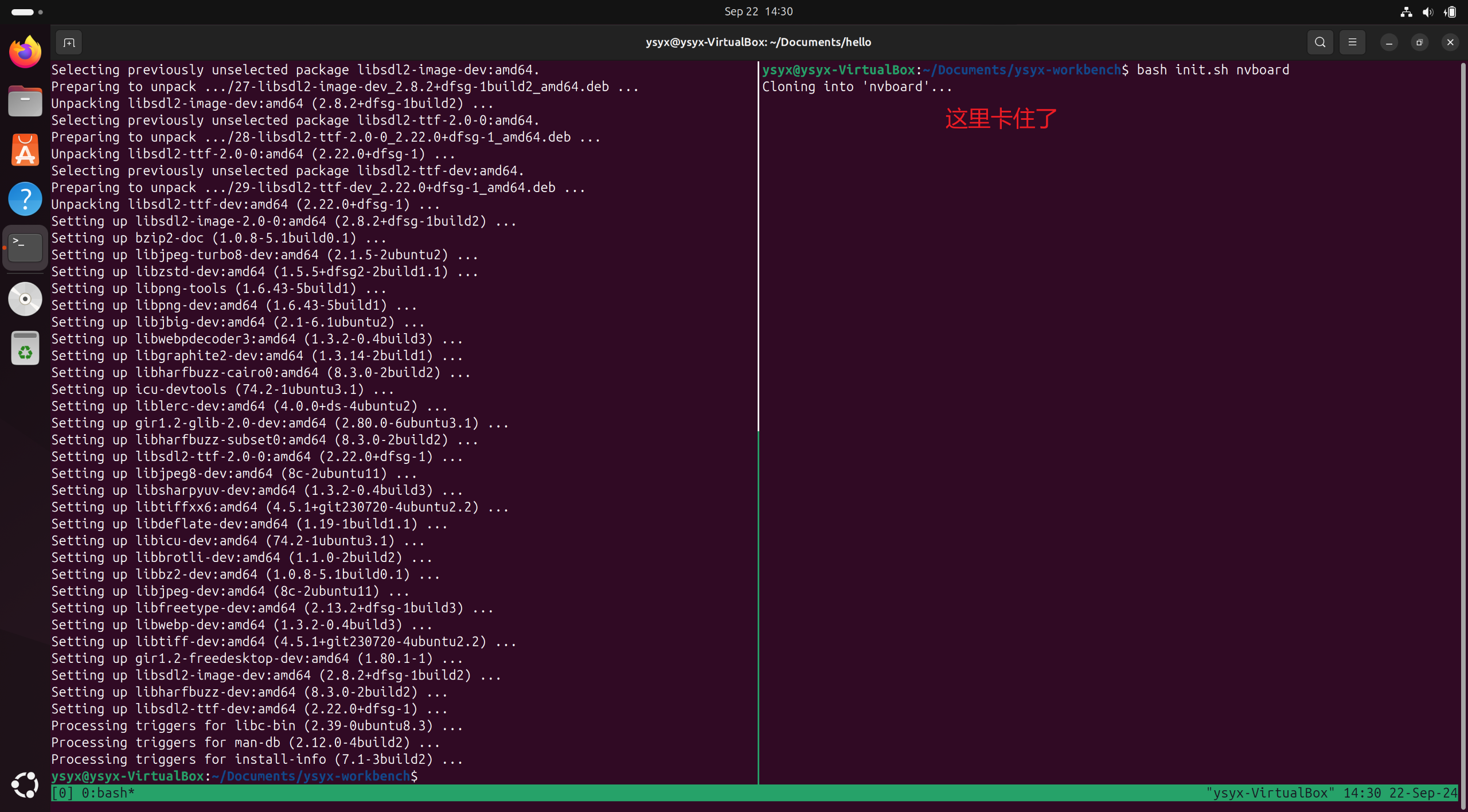

按照ysyx手册的要求,初始化NVBoard项目。

由于GitHub在国外,可能会超时无响应:

解决方案是修改代理。

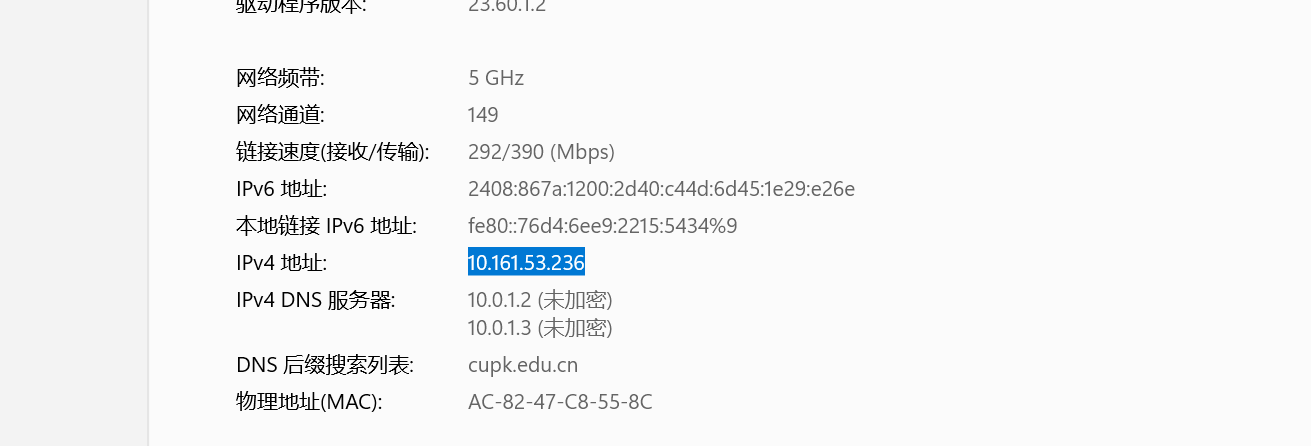

当前的运行环境是VM VirtualBox虚拟机,网卡是:网络地址转换NAT。

主机有访问国外网站,可以让虚拟机连接主机的代理接口。

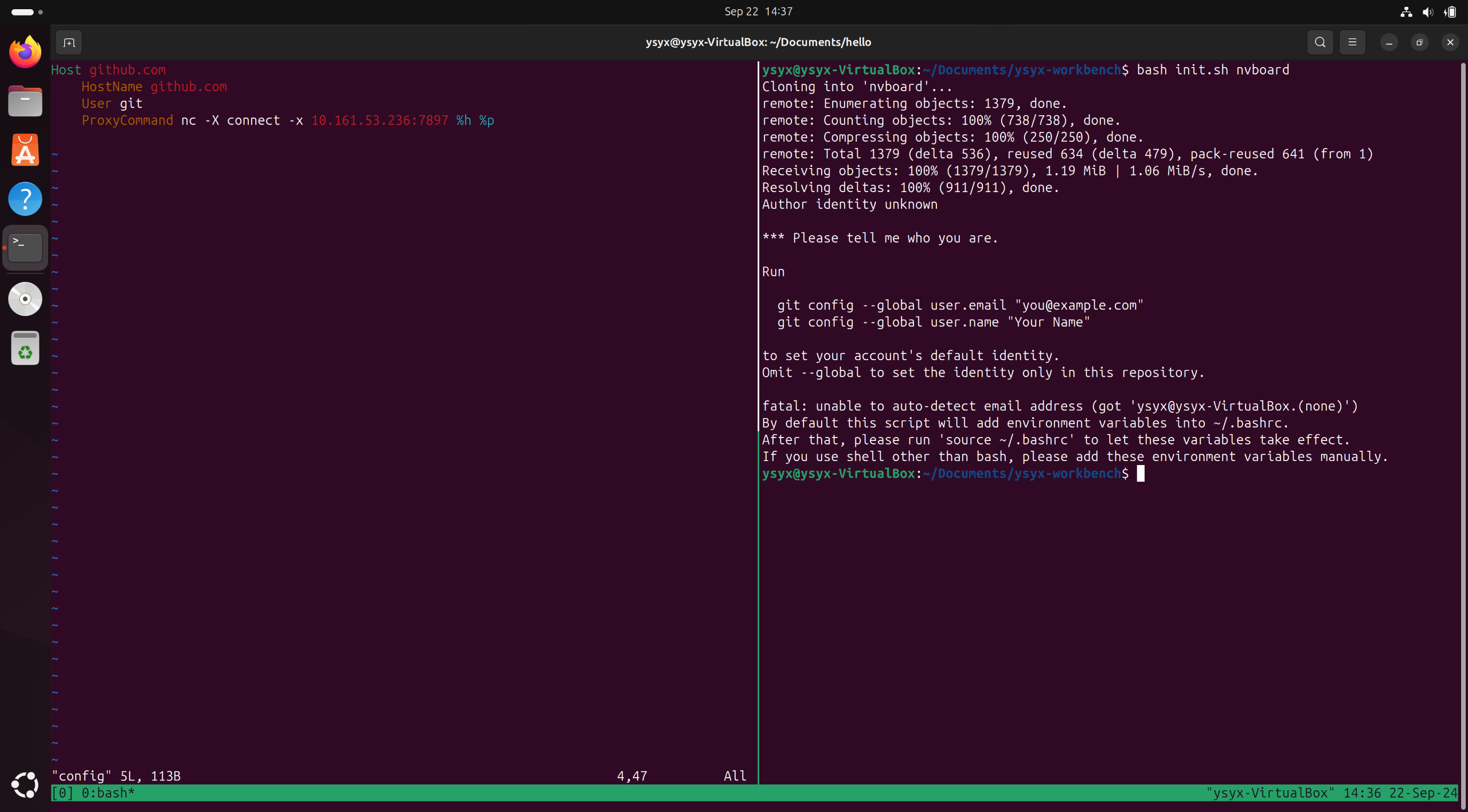

修改或新建~/.ssh/config:

Host github.com

HostName github.com

User git

ProxyCommand nc -X connect -x 10.161.53.236:7897 %h %p 修改上面的ip地址端口为主机实际地址即可。

现在可以成功下载:

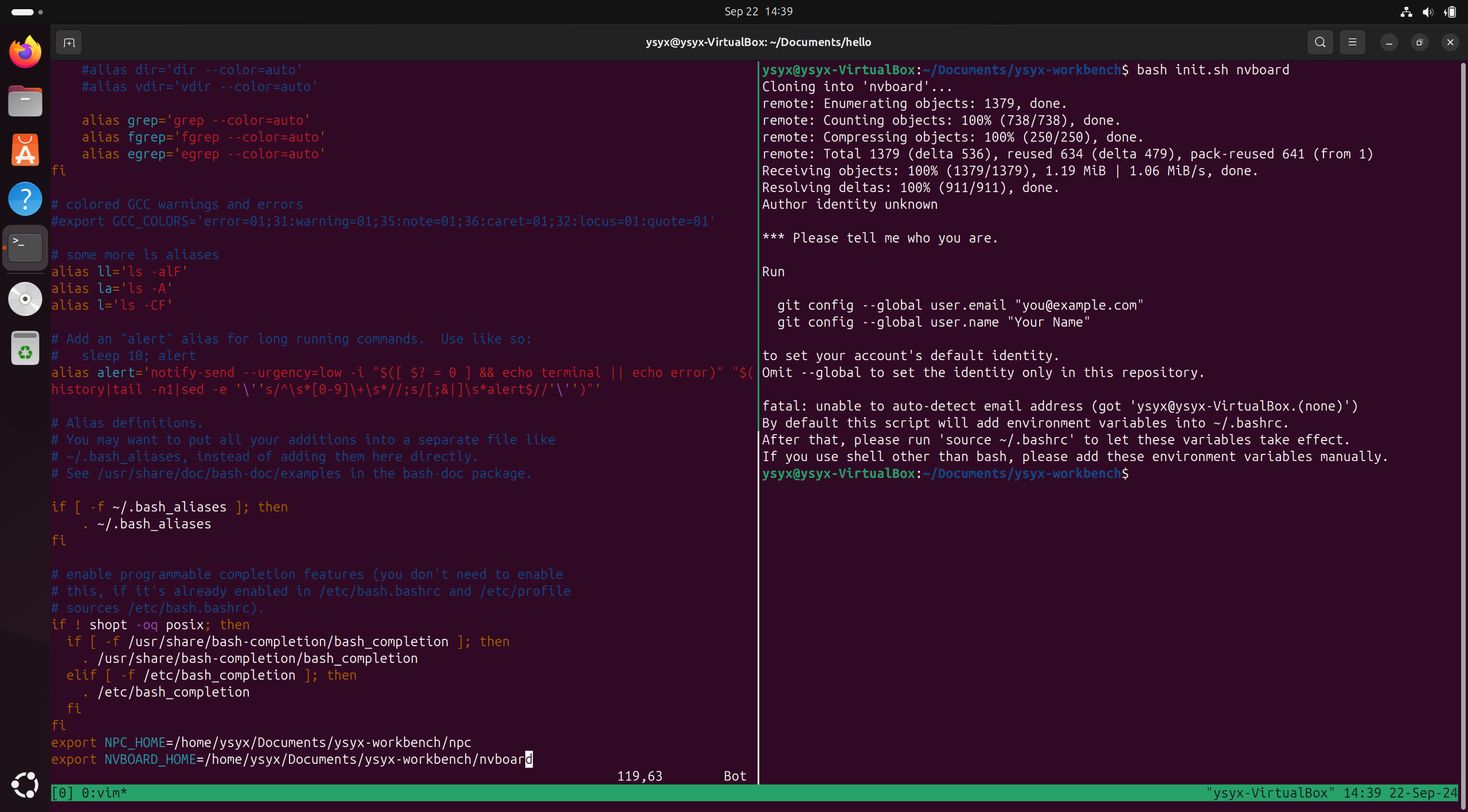

安装官方仓库readme的要求,需要添加环境变量NVBOARD_HOME指向所在的文件目录。

亲测通过ysyx导入会自动配置。

如果没有配置,可以参照下图,在~/.bashrc后手动追加。

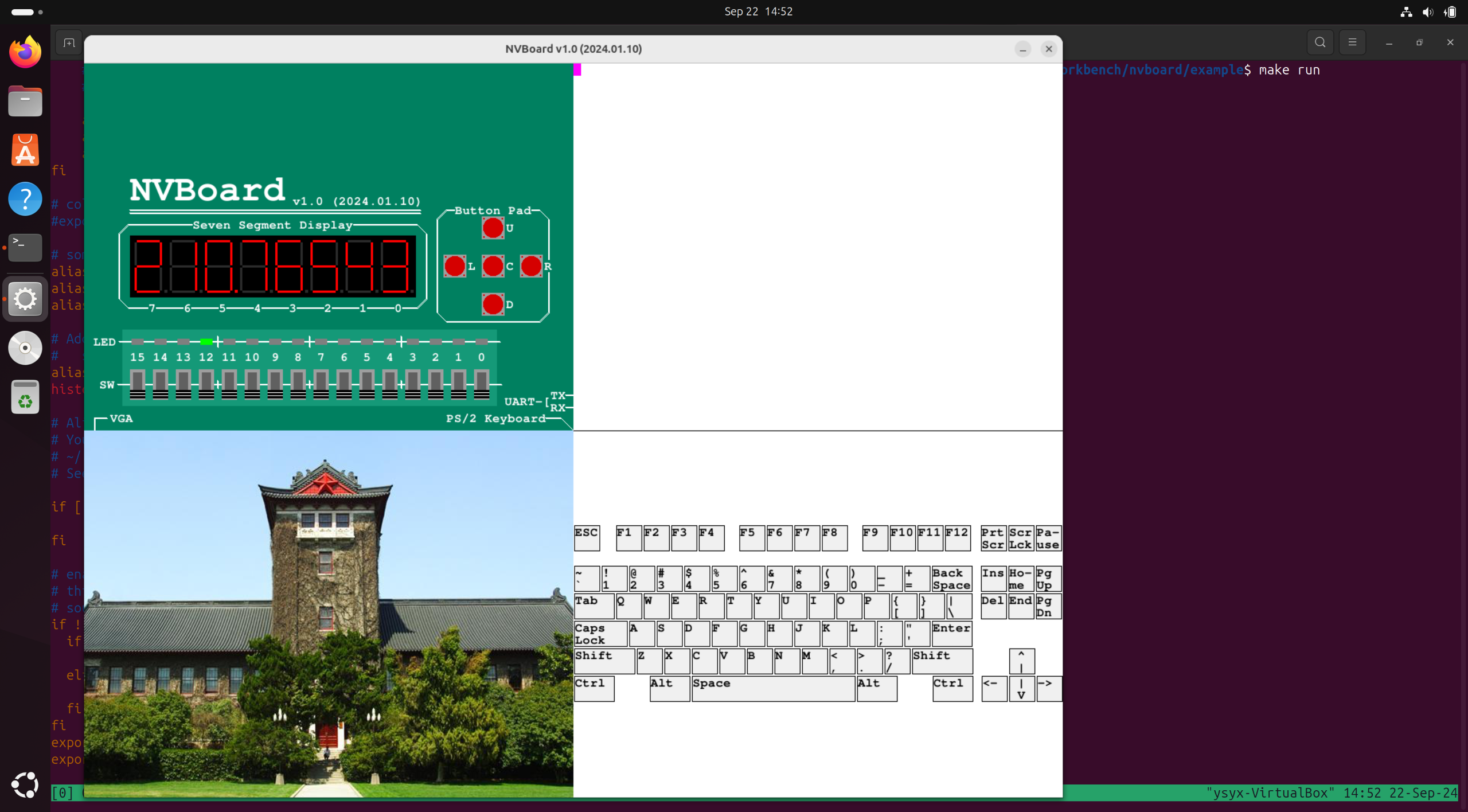

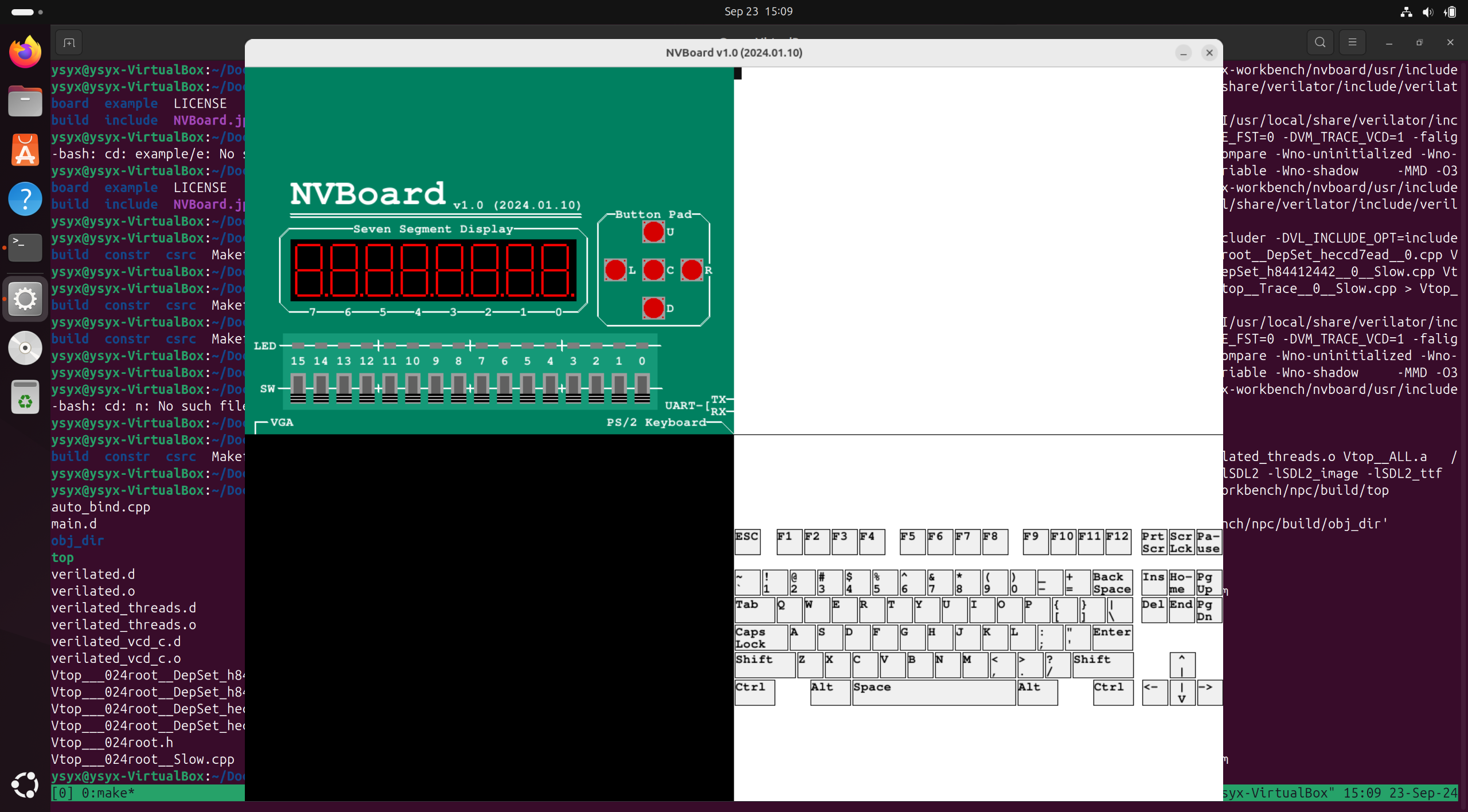

进入/ysyx-workbench/nvboard/example目录下运行make run,而不是直接在/ysyx-workbench下运行。

如果报错找不到/scripts/nvboard.mk。

那可能是环境变量没有生效,需要source ~/.bashrc。

运行结果:

创建verilator项目

双控开关

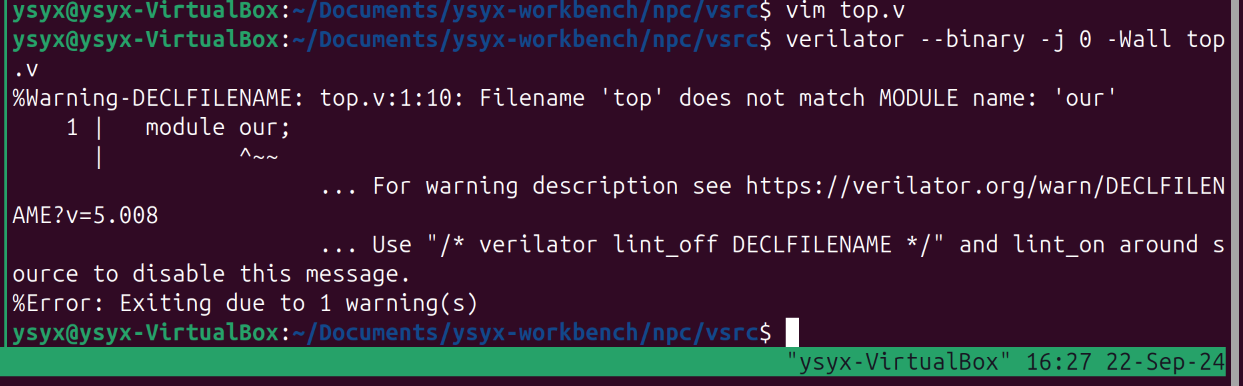

样例给的一般是.v作为verilator格式后缀。

文件名必须与类名相同,否则会报错:

编译语句较长,编写Makefile文件简化操作。

本人也是初学,目前是能成功编译。

肯定会存在一些规范问题,之后边学边解决。

VSRC_DIR=./vsrc

BUILD_DIR=./build

VERILATOR_FLAGS = --binary -j 0 -Wall -I$(VSRC_DIR) --Mdir ${BUILD_DIR}

all:

@echo "Write this Makefile by your self."

sim:

$(call git_commit, "sim RTL") # DO NOT REMOVE THIS LINE!!!

#@echo "Write this Makefile by your self."

Vtop:${VSRC_DIR}/top.v

verilator ${VERILATOR_FLAGS} ./top.v

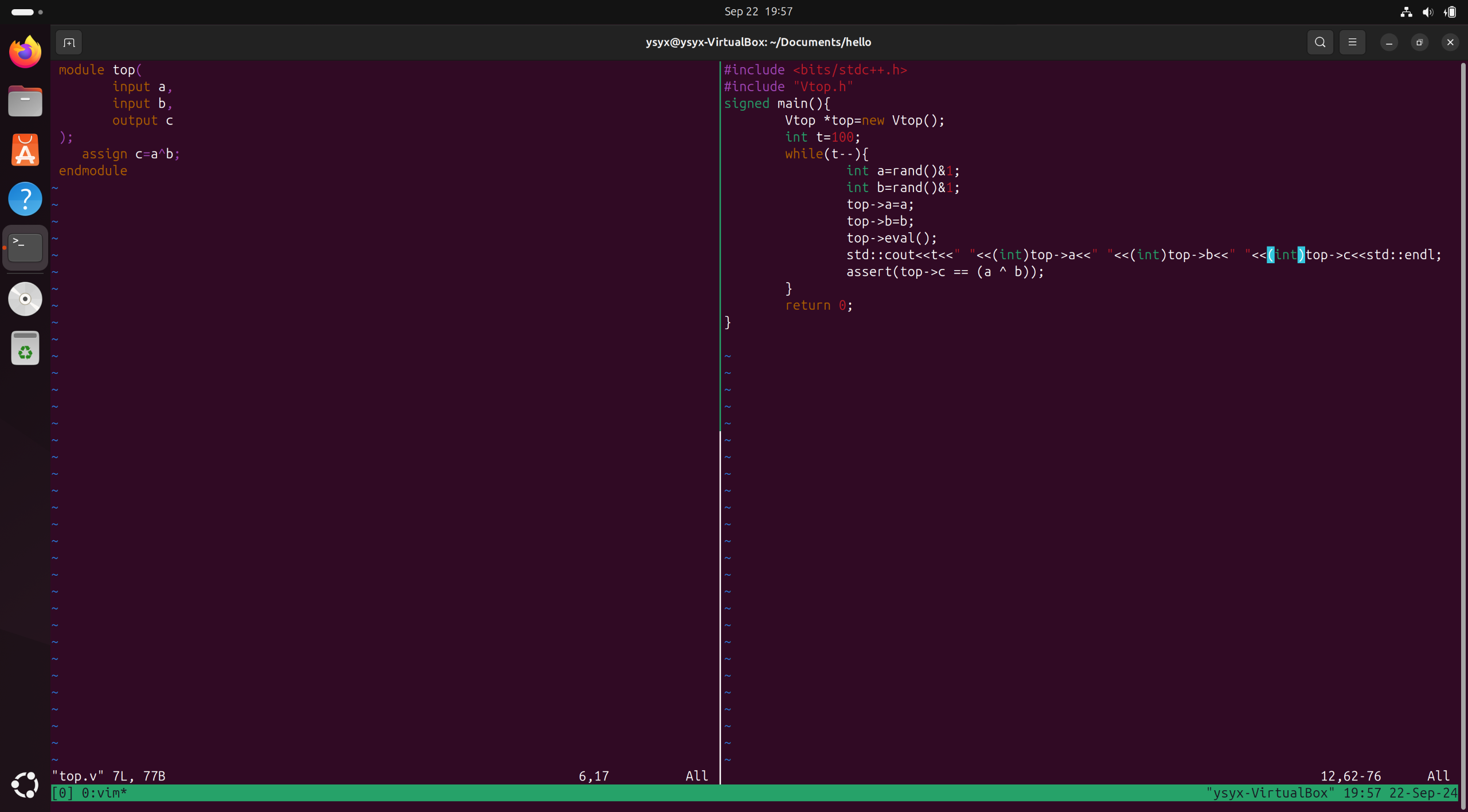

include ../Makefile修改top.v内容为双控开关代码:

补充说一下,Ctrl b z可以全屏显示,当前分屏方案下的,活跃窗口

再按一次可以恢复分屏方案。

编译命令为:verilator -Wall --cc --exe --build main.cpp top.v

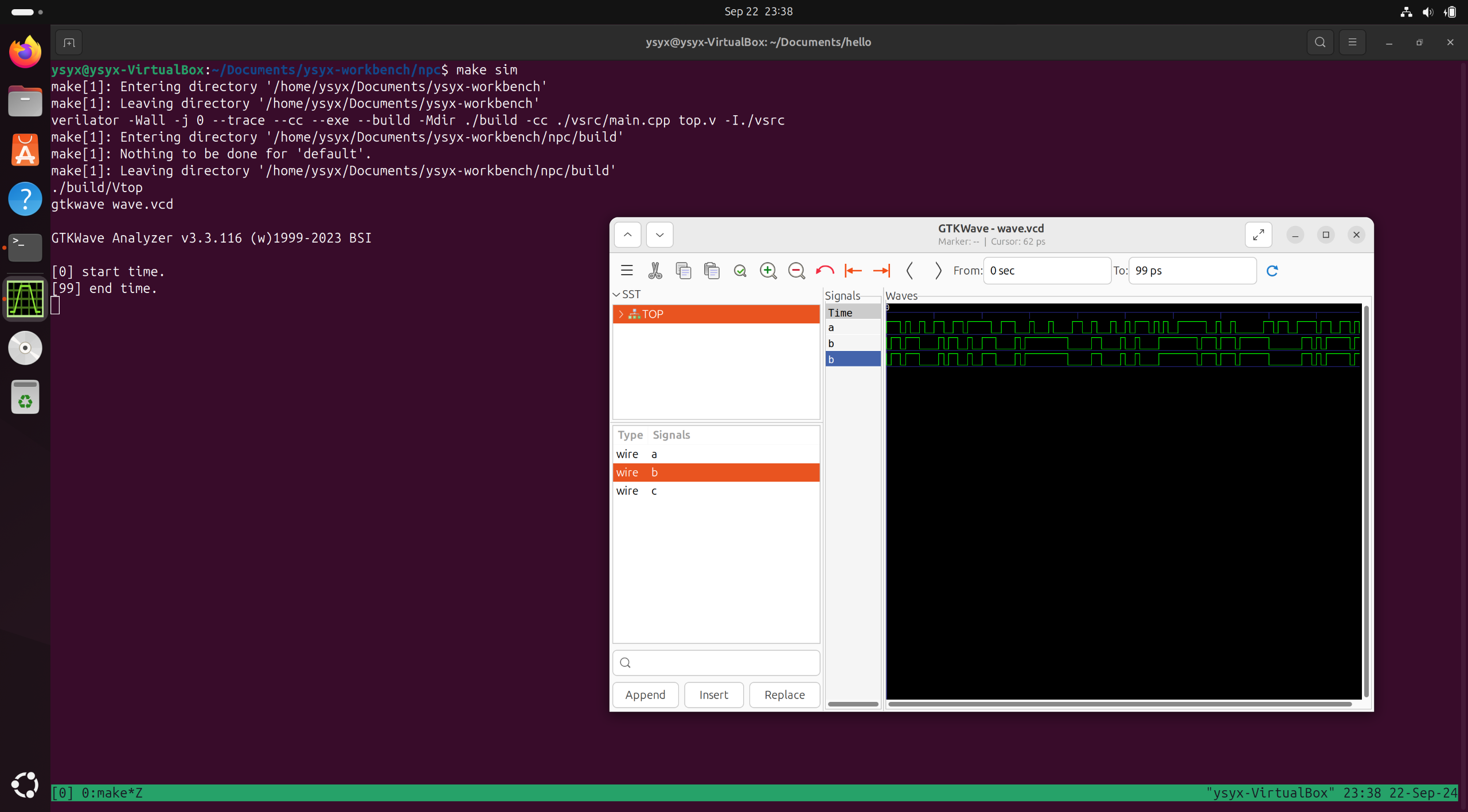

显示波形

Makefile文件内容:

- 生成可执行文件

--trace:允许记录波形,不开启此选项在记录波形时会报错--cc:语言是C++--exe --build:生成可执行文件

- 执行可执行文件

- 查看波形

main.cpp内容:

#include <bits/stdc++.h>

#include "Vtop.h"

#include "verilated_vcd_c.h"

signed main(){

VerilatedContext* contextp = new VerilatedContext;

Vtop* top=new Vtop(contextp);

VerilatedVcdC* tfp = new VerilatedVcdC;

contextp->traceEverOn(true);

top->trace(tfp,0);

tfp->open("wave.vcd");

while(contextp->time()<100){

int a=rand()&1;

int b=rand()&1;

top->a=a;

top->b=b;

top->eval();

tfp->dump(contextp->time());

contextp->timeInc(1);

//std::cout<<t<<" "<<(int)top->a<<" "<<(int)top->b<<" "<<(int)ctop->c<<std::endl;

assert(top->c == (a ^ b));

}

tfp->close();

return 0;

}最后必须写tfp->close();,亲测否则不会生成波形文件。

还需要再gtkware左侧双击才能显示波形。

接入NVBoard

刚才的文件目录结构有很多不规范之处

参照NVBoard官方仓库的样例:

csrc:存放.cpp文件vsrc:存放.v文件constr:存放.nxdc文件

其中constr文件夹默认npc下没有给出。用于绑定nvboard引脚。

如果你创建一个不绑定任何引脚的.nxdc文件,比如:

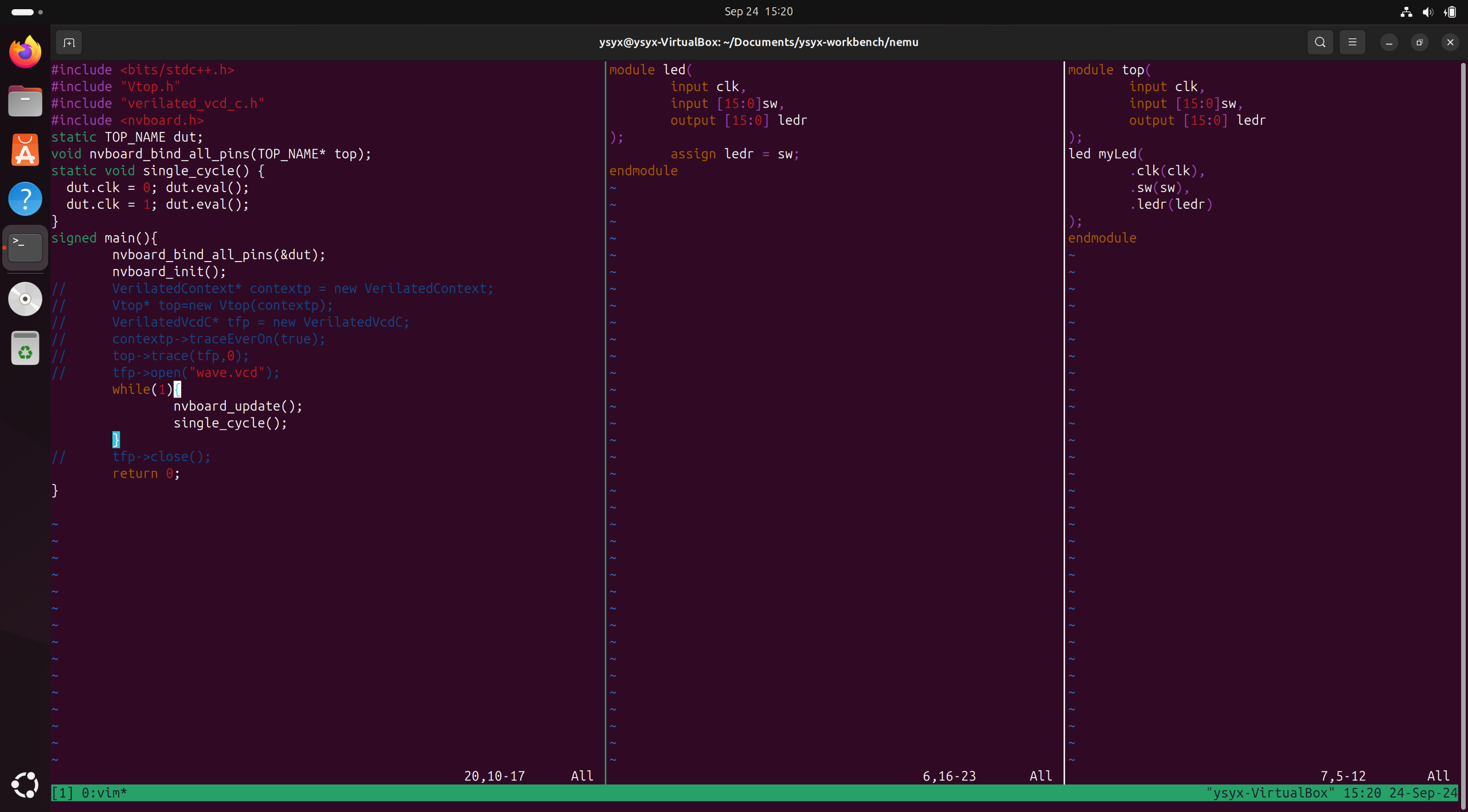

top=top并仿照官方样例的main.cpp结构,修改之前的main.cpp:

#include <bits/stdc++.h>

#include "Vtop.h"

#include "verilated_vcd_c.h"

#include <nvboard.h>

static TOP_NAME dut;

void nvboard_bind_all_pins(TOP_NAME* top);

static void single_cycle() {

dut.clk = 0; dut.eval();

dut.clk = 1; dut.eval();

}

signed main(){

nvboard_bind_all_pins(&dut);

nvboard_init();

VerilatedContext* contextp = new VerilatedContext;

Vtop* top=new Vtop(contextp);

VerilatedVcdC* tfp = new VerilatedVcdC;

contextp->traceEverOn(true);

top->trace(tfp,0);

tfp->open("wave.vcd");

while(contextp->time()<100){

nvboard_update();

single_cycle();

}

tfp->close();

return 0;

}把Makefile文件抄过来,界面大概是这个样子的:

经过stfsc,没发现官方仓库example目录下没有办卡前端的配置项。

也就是说,这个办卡的前端是固定的,通过.nxdc文件绑定引脚,控制显示内容。

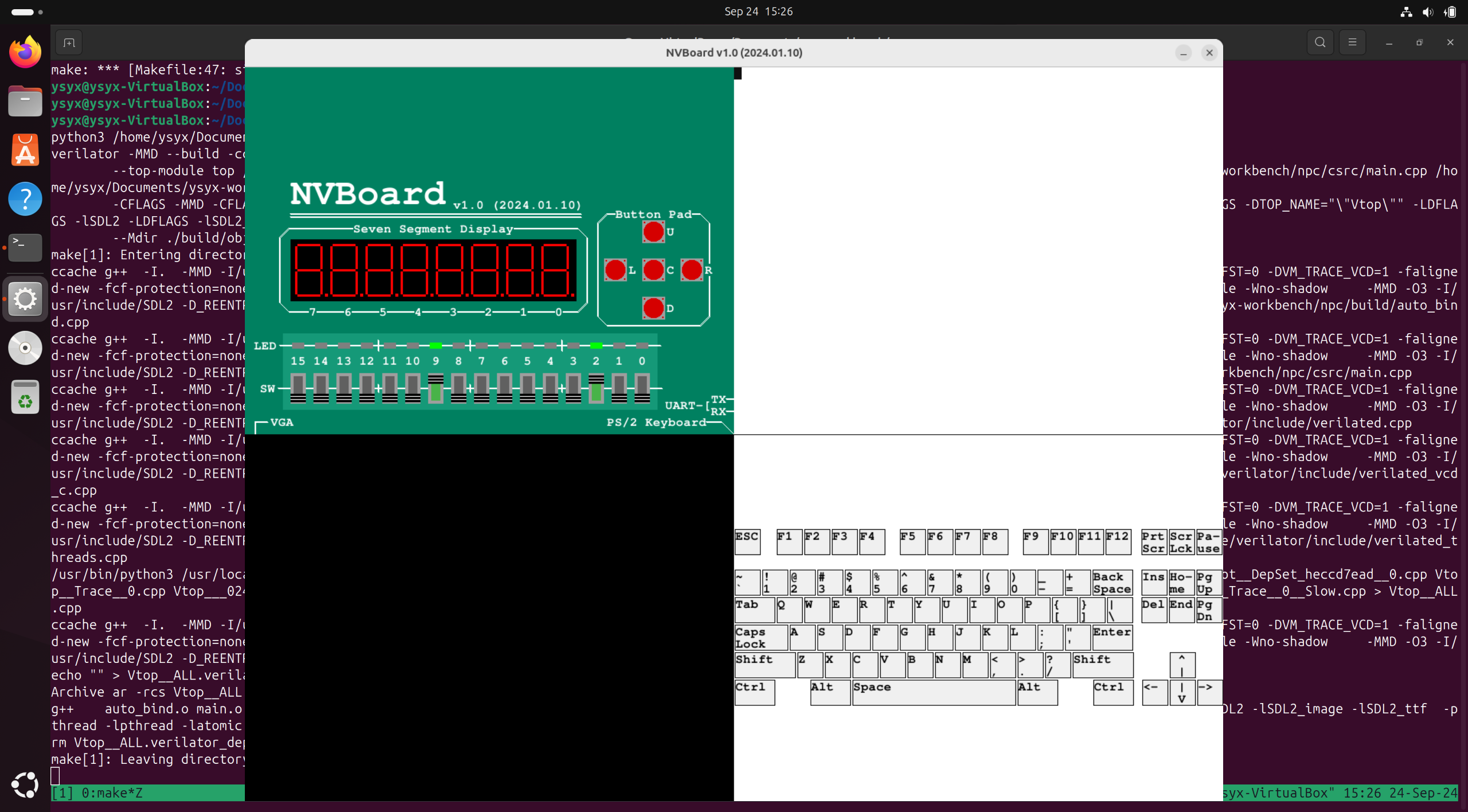

接入双控开关

对于板载的16个开关,期望需求是:

- 开关拨上去的时候,上方的灯是亮的

- 开关拨下去的时候,上方的灯是灭的

顶层模块是top,led myLed用于创建一个led模块,并将引脚绑定。

模块间绑定之后,还需要将顶层模块与NVboard绑定,这一部分资料较少,可以选择STFRC阅读源码。

编辑top.nxdc:

top=top

ledr (LD15, LD14, LD13, LD12, LD11, LD10, LD9, LD8, LD7, LD6, LD5, LD4, LD3, LD2, LD1, LD0)

sw (SW15, SW14, SW13, SW12, SW11, SW10, SW9, SW8, SW7, SW6, SW5, SW4, SW3, SW2, SW1, SW0)左侧是ledr和sw的顶层模块的输入输出引脚

- 命名由开发者自定义

右侧的(LD15, ..., LD0)是将引脚绑定到NVboard的对应位置

- 命名在

NVboard中写死

运行效果:

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

评论

登录后参与评论

推荐阅读

目录