基准源噪音如何悄悄溜进 ADC(以3PEAK TPR70 为例)

基准源噪音如何悄悄溜进 ADC(以3PEAK TPR70 为例)

云深无际

发布于 2026-01-07 13:50:40

发布于 2026-01-07 13:50:40

前天晚上的文章已经写明白了,高位的 ADC,量化误差不是主导了(而是除了 ADC 之外的这些器件不给力,把噪音传导到了 ADC 内部,造成了最终的采集效果),那就自然而然的引出来了今天的文章:准源的噪音是如何进入 ADC 影响最终的精度的?

基准源(VREF)在 ADC 里的作用

对任何 ADC 来说,参考电压 决定了量化台阶的绝对大小:

因此,ADC 输出码的实际意义是:

VREF 相当于 ADC 的“标尺”:输入电压被它归一化后再量化,这意味着如果参考电压本身在抖动(有噪声或纹波),整个标尺就随时间波动,哪怕输入电压是静止的,数字输出也会抖动。

VREF 噪声的进入路径

ADC 内部包含两个主要通路:

输入路径 (VIN) ──► 比较器 / 调制器 ──► 数字输出

参考路径 (VREF) ──┘ ↑

│

“基准标尺” & 电荷转移节点

输入路径:采样电容、输入开关、输入缓冲;

参考路径:为采样电容充放电提供基准电压(SAR)或设定积分器基准(ΔΣ)。

每次采样,ADC 会比较“VIN 与 ±VREF 的比例”;因此,VREF 的微小变化等效于输入端被乘以一个时间相关系数:

由此产生输出等效噪声:

从上式可得:

量 | 意义 |

|---|---|

基准源自身的 RMS 噪声 | |

当前输入信号幅度 | |

参考电压幅值 | |

折算到 ADC 输入端的等效噪声(输入参考噪声) |

对着公式我们可以看到与输入幅度成正比(输入越大,影响越大);与参考电压成反比(更高的 VREF 抑制参考噪声影响);而且本质是乘性噪声(比例误差),与放大器、量化噪声那种加性噪声不同。

定量计算一个

假设:

µ(REF60xx 级)

输入信号幅度

则折算到输入端的等效噪声为:

µµ

如果 ADC 的自身噪声为 0.8 µV_RMS, 则加上参考噪声后:

µ

→ 精度下降约 3 %,在 24 bit ΔΣ ADC 中,这已经足以损失 0.1 bit 以上有效分辨率。

不同架构中的表现

上面只是数学定量的说 REF 的影响,但是在具体的器件上面的影响还是会落实到具体的工作模块:

ADC 类型 | 参考噪声耦合特点 | 说明 |

|---|---|---|

SAR ADC | 直接参与采样电容充电 | 参考瞬态电流大、对瞬态阻抗敏感(需低阻驱动、低 ESR 去耦) |

ΔΣ ADC | 参与积分器的基准注入 | 电流波形平滑,对 1/f 噪声和低频稳定度敏感 |

SAR → 注意 瞬态电流尖峰 与 局部去耦;

ΔΣ → 注意 低频 1/f 噪声 与 长时稳定性;两者都需防止参考通路与输入通路共地耦合。

比例噪声效应

输入固定 VIN = 1.00000 V

VREF = 2.500000 V

↓

若 VREF 波动 ±10 µV:

→ 实际比值变化 ±(10 µV / 2.5 V) = ±4 ppm

→ 输出码变化 ±4 ppm × Fullscale ≈ ±17 LSB (在 22 bit 下)

可见,几微伏的基准噪声就足以让 24-bit ADC 输出抖动十几 LSB。

为什么是“乘性噪声”?

代码理想值:code = (VIN/VREF)*2^N;当 VREF → VREF + n_ref(t),则

code_noisy ≈ (VIN/VREF)*(1 - n_ref/VREF)*2^N

Δcode ≈ -(VIN/VREF)*(n_ref/VREF)*2^N

Δcode 与 n_ref 成正比,并且与 VIN 成正比(输入越大,影响越大),与 VREF 成反比(参考越大,影响越小)。

基准源的噪声并不会“加”在输入上,而是“乘”在输入上;它让 ADC 的量化标尺抖动,从而把参考电压的微小波动直接转化为输出比例误差;在高分辨率 ADC(20–24 bit)中,这个比例噪声常常与甚至超过内部量化和热噪声,成为最终系统精度的决定性限制。

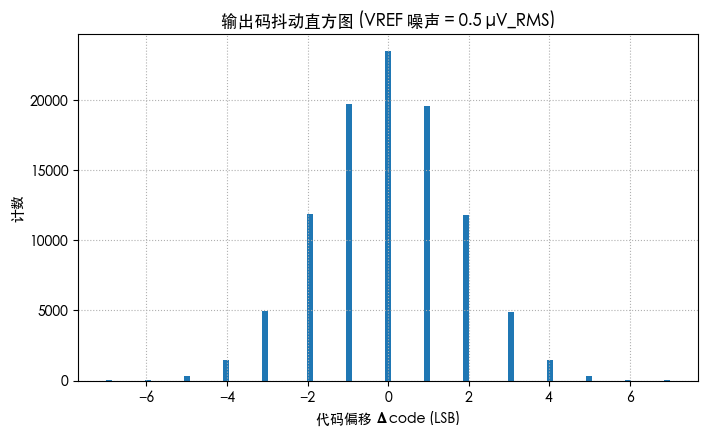

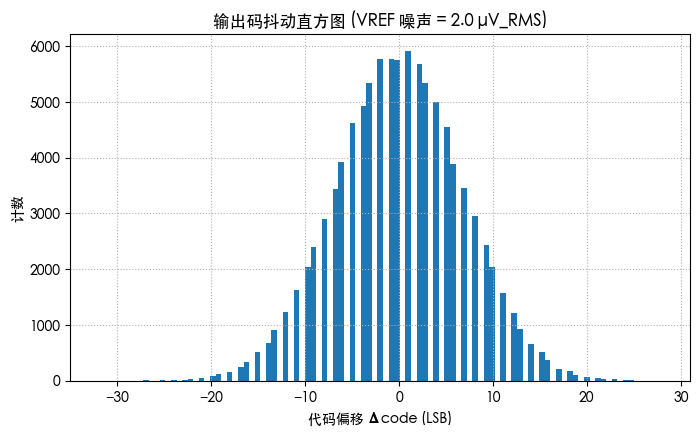

24-bit ADC;VIN=50%FS;VREF=2.5 V;LSB = 0.149012 µV

参考噪声引起的输出码抖动(统计 100000 次)

RMS(VREF) [µV] σ_code [LSB] σ_RTI [µV]

0.000 0.0000 0.0000

0.100 0.3689 0.0550

0.500 1.7017 0.2536

1.000 3.3730 0.5026

2.000 6.7270 1.0024

5.000 16.7646 2.4981

σ_RTI(输入参考噪声)≈ σ_code·LSB,是把码抖动折算回输入端的电压;VREF 噪声从 0.1→5 µV_RMS,输出码抖动从 0.37 LSB 增加到 16.8 LSB,且与理论近似 线性正比(因为 VIN 固定、VREF 固定,RTI≈VIN/VREF·VREF_noise)。

0.5 µV_RMS:分布较窄,σ≈1.7 LSB,仍清晰集中;

2.0 µV_RMS:分布显著展宽,σ≈6.7 LSB,24-bit 读数已被参考噪声主导(哪怕 ADC 自身很“安静”)。

实际应用的选择

首先是用低噪声基准源,降低 VREF 噪声本体(10 Hz–10 kHz 带内 < 1 µV_RMS 级别(如 ADR45xx/REF60xx/LT6657 等族),并注意温飘与长期稳定度);接着是增加 VREF 幅值,让 ADC减小比例项 ,可以在输出的path 上面使用RC 滤波,对于SAR 参考驱动需低输出阻抗、承受瞬态充放电;ΔΣ 关注低频 1/f。局部 C(陶瓷+钽/铝电解)并合适的 RC/π 滤波。参考地与模拟地的回流路径分离,避免把输入噪声“变相耦合”进参考网络。(老生常谈)

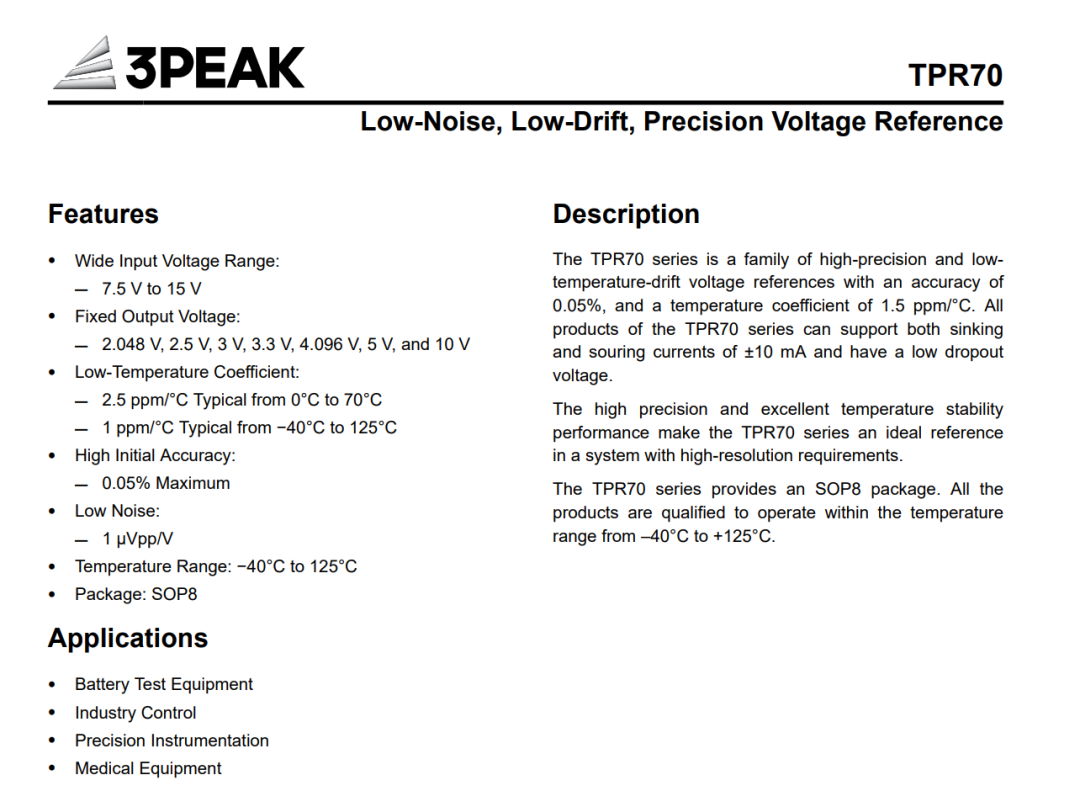

看看3PEAK的TPR70

3PEAK 有好多的基准,我看了看最好的就是这个 70:

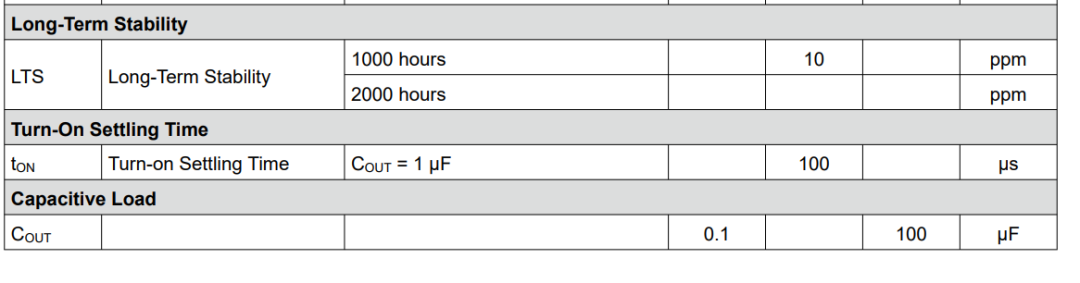

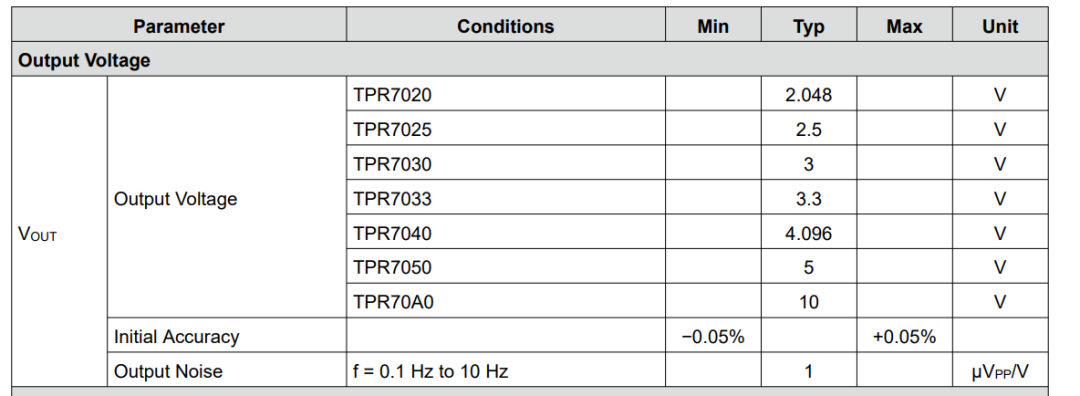

定位是低噪声、低漂移、带 NR 引脚可降噪的系列基准源(2.048–10 V 多版本,SOP-8)。输入 7.5–15 V,能源/汲各 ±10 mA。

温漂与长期稳定性:全温(−40~125 °C)典型 1.5 ppm/°C、最大 3 ppm/°C;长期 1000 h 典型 10 ppm;热迟滞给了多轮循环的典型值。→ 对 20–24 bit ΔΣ/SAR 足够“安静”。

低频噪声

低频噪声

规格表给出 0.1–10 Hz:1 µVpp/V;文中还说明在 2.5 V 版本、室温、接 NR 时,典型 2.5 µVpp,且 NR=10 nF 可继续降低。→ 2.5 V 器件的 0.1–10 Hz 典型约 2.5 µVpp ≈ 0.38 µV_RMS(pp→RMS 约÷6.6),作为输入参考噪声的乘性项通常远小于 ADC 自身宽带噪声。

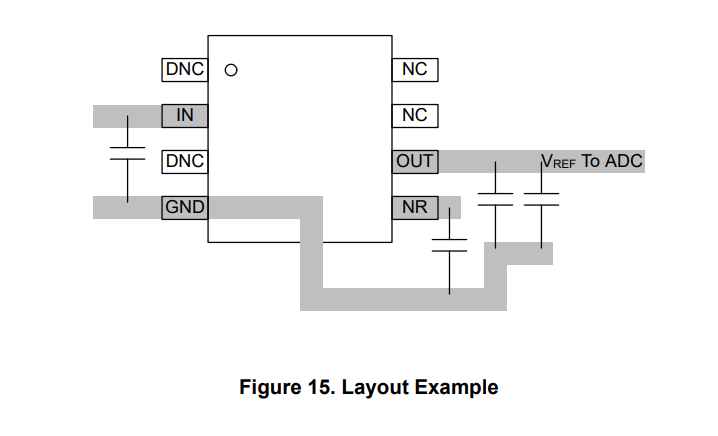

推荐输入并联 1–10 µF + 0.1 µF,就地小回路;输出 1–50 µF 并联 1 µF 陶瓷改善瞬态;NR→GND 放 ≥10 nF 抑制噪声。这些对 SAR 参考瞬态与 ΔΣ 低频噪声都关键。;VOUT≤5 V 时线性调整率 0.1 ppm/V(典型);负载调整率 2.5 ppm/mA(典型)。这有助于把参考纹波与负载跳变引起的误差压到 ppm 级。

低频(0.1–10 Hz)参考噪声 → 输入参考(RTI)等效

1 µVpp/V(0.1–10 Hz);2.5 V 器件典型 2.5 µVpp(可加 NR=10 nF 再降)。

折算:(乘性项) 例:ΔΣ 24 bit,2.5 V 参考,输入 0.5 V_RMS;若 ,→ 。 对多数高分辨率 ADC(>0.5 µV_RMS 宽带噪声)来说,这一项可忽略或占比很小。

若信号是直流/超低频测量(0.1–10 Hz),请务必接 NR(≥10 nF)并在输出端用较大 C 把低频噪声再压一档。

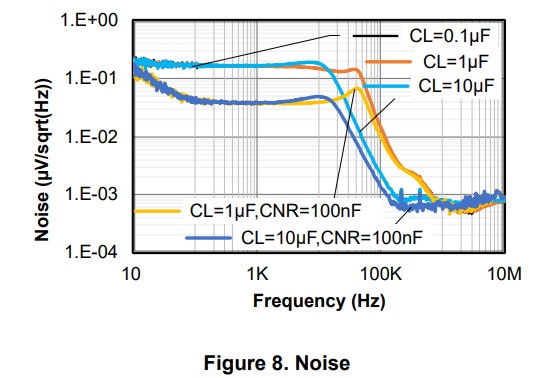

文档提供了“噪声密度 vs 频率”的典型曲线(含不同 C_OUT / C_NR 组合),能看到 NR+较大 C_OUT 对宽带噪声也有可见抑制。具体数值未逐点表格化,建议按你的目标带宽实测或留裕量。

其中线性调整率(VOUT≤5 V)典型 0.1 ppm/V;负载调整率典型 2.5 ppm/mA。若 SAR 采样电容拉动瞬态电流或前级电源纹波较大,上述 ppm 级抖动将直接变为比例误差。对 20+ bit 分辨率,布局+去耦至关重要。

给ΔΣ(高分辨率、低频)做基准时有着超低温漂(1.5–3 ppm/°C)、低 0.1–10 Hz 噪声(NR 可降),长期 10 ppm/1000 h。很适合 20–24 bit 直流/慢速测量、基准/量程标尺用途。

但是要注意规格表的“1 µVpp/V(0.1–10 Hz)”是带宽极窄的低频指标,宽带噪声需参考 典型噪声密度曲线(Fig. 8)并结合你的实际带宽评估;对高速 SAR 来说,输出阻抗+瞬态控制更关键;而初始精度为 ±0.05%(±500 ppm),高等级计量需一次系统标定。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-11-15,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录