RF 直采 10Ghz 12bit ADC:ADC12DJ5200

RF 直采 10Ghz 12bit ADC:ADC12DJ5200

云深无际

发布于 2026-01-07 13:31:25

发布于 2026-01-07 13:31:25

一颗30W+的ADC12DJ5200-单通道10.4G SPS

在高速 ADC 这块,除了我天天写的 40G 这颗,其实大部分的还是集中在 10G 的样子,这样的 ADC 称为 RF-ADC(我自己给起的名字),就是可以对一些射频信号进行直接采样:

我之前应该写过这个

我之前应该写过这个

标题是什么 30W,其实没有那么贵。。。

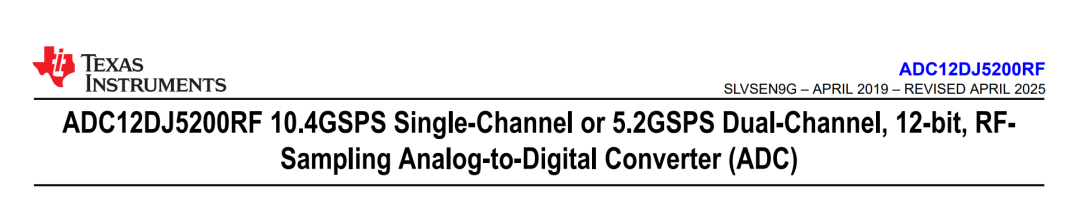

构架上面确实是两个 ADC,高采样的时候也是使用了这个交错

构架上面确实是两个 ADC,高采样的时候也是使用了这个交错

ADC12DJ5200RF 是一颗 12 bit、最高 10.4 GSPS 的 RF-Sampling ADC。 可以配置成:

单通道模式:10.4 GSPS

双通道模式:每通道 5.2 GSPS

双ADC

在芯片内部,它包含 两颗完全对称的 12-bit ADC 内核:

┌───────────────┐

RF_IN_A →│ ADC_A (12 bit)│─┐

└───────────────┘ │

├─ JESD204C TX Lanes (可独立或合并)

RF_IN_B →│ ADC_B (12 bit)│─┘

└───────────────┘

两路 ADC 的采样时钟、触发、校准与 DDC(数字下变频器)都可独立控制或耦合运行。

主要工作模式

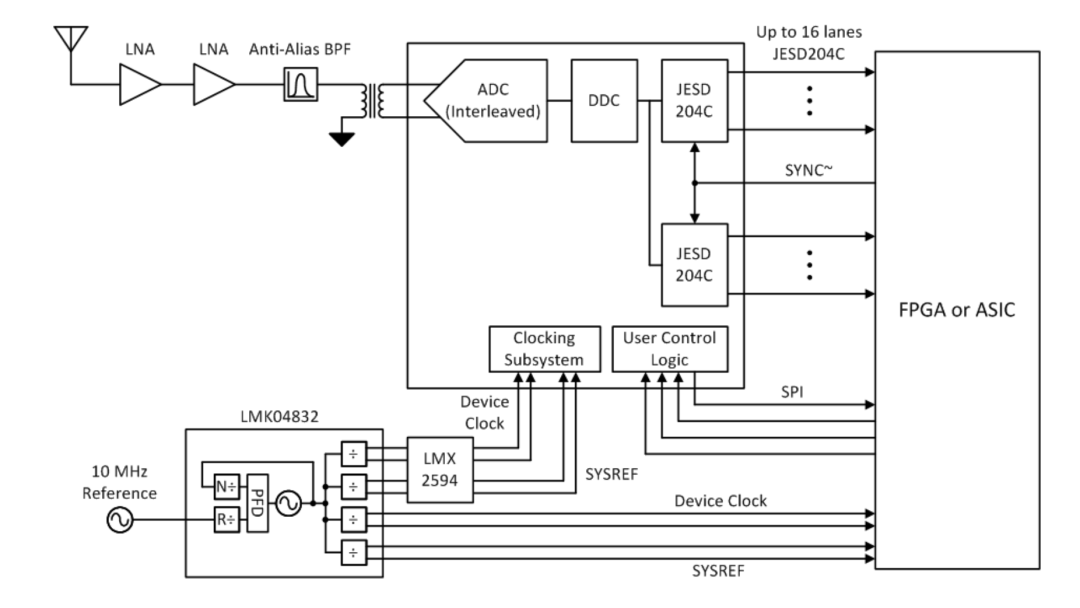

双通道模式(Dual Mode)

每个 ADC 独立采样一组模拟输入。

采样率:5.2 GSPS × 2 通道。

相当于两颗 12-bit ADC 并列工作。

输出:每通道使用独立的 JESD lane 组,可以用于双输入接收机(I/Q、双天线等),同步捕获两个射频通道。

射频采样

射频采样

单通道交织模式(Interleaved Mode)

两个 ADC 以 180° 时钟相位交织采样。

有效采样率翻倍:10.4 GSPS(单输入)。

输出数据由内部逻辑交织合并。

常用于:单路超宽带直采系统(示波器、频谱仪)。

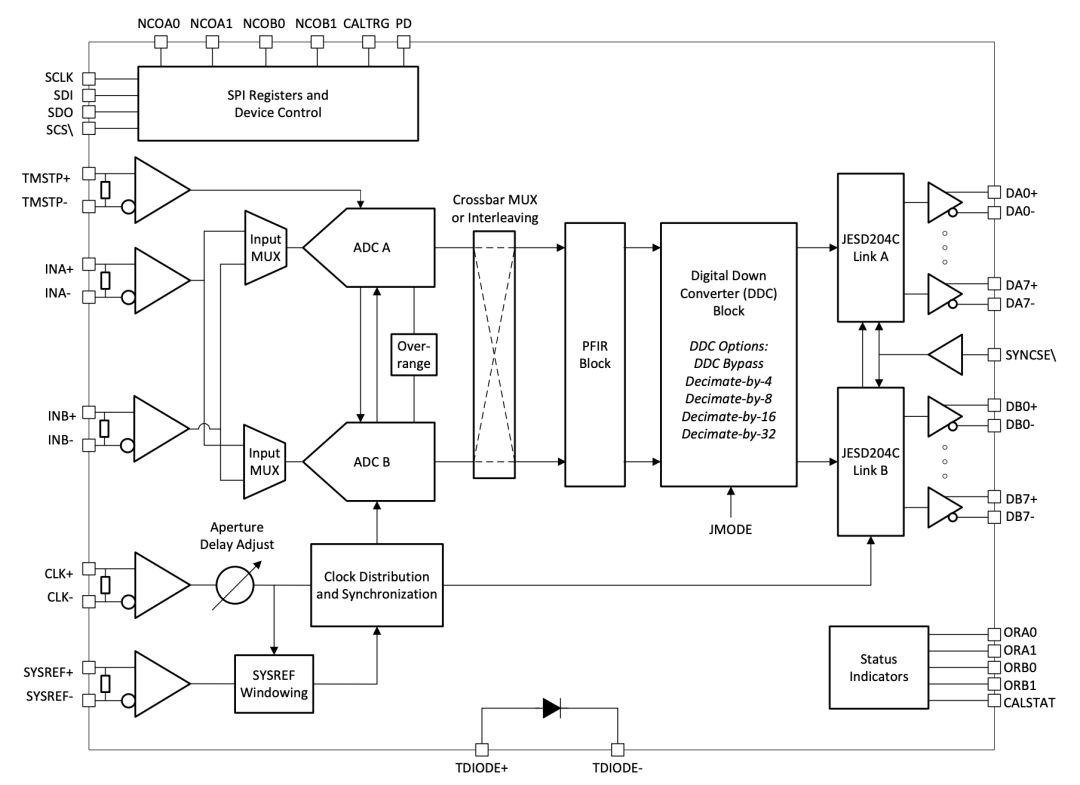

比如这样的

比如这样的

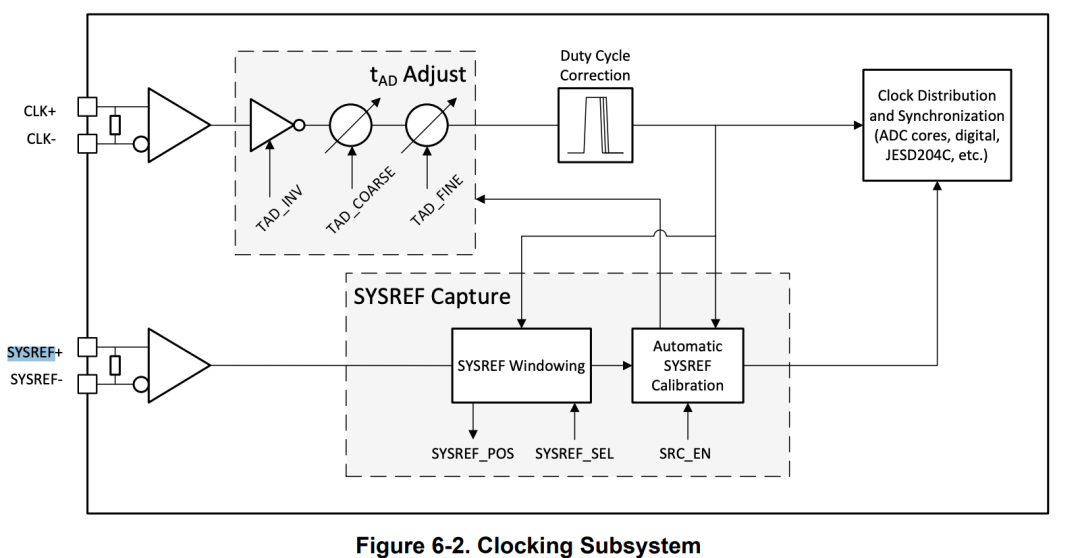

时钟与同步

image-20251029214044526

两个 ADC 共用同一外部时钟,但相位可精密调节(内部 delay line);通过 SYSREF + JESD Subclass 1 实现多片确定性延迟同步。内置 A/B 相位匹配电路(aperture delay adjust)精度达 19 fs;它的最大模拟输入带宽高达 > 10 GHz,意味着能直接采 L/S/C/X 波段的射频信号,不需要下变频器,非常适合:高端示波器、频谱仪。

据输出速率计算

在 单通道 10.4 GSPS、12 bit 下:

原始

JESD204C 接口经过 64b/66b 编码后效率 ≈ 97%,所以输出速率 ≈ 128 Gbps;分 8 ~ 16 lane 即可(每 lane 最高 17.16 Gbps);其中在双通道 5.2 GSPS × 2 模式下,总输出同样 ≈ 128 Gbps。

军用产品

还有一个带 EP 的

还有一个带 EP 的

主要看温度特性:–55 °C – +125 °C 工业/军用范围;芯片结温上限 150 °C。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-10-30,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录