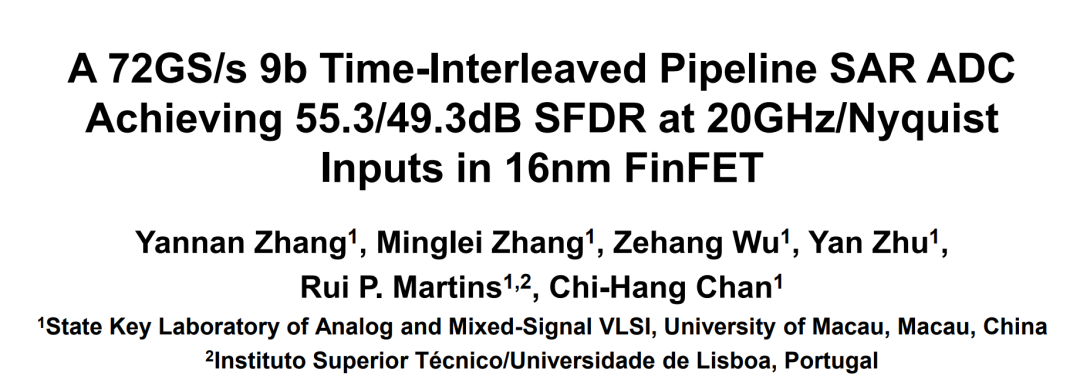

ISSCC 2025,72GS/s 9bit 学界最高指标 分级流水线 ADC(YUNSWJ 解读版)

ISSCC 2025,72GS/s 9bit 学界最高指标 分级流水线 ADC(YUNSWJ 解读版)

云深无际

发布于 2026-01-07 13:27:15

发布于 2026-01-07 13:27:15

给大家伙整点新货,Tony 老师最近给了一堆的高速 ADC论文,实话实话,有时候挺简单的概念写的就是让人看不懂,但是高速这块确实是才摸摸门框子,毕竟低速世界还没有完全搞明白。

今天给大家先分享一个学界的 ADC:

好

好

居然是厦门大学的工作

居然是厦门大学的工作

没错,都流片了

没错,都流片了

好像这个会议都需要流片?

看看怎么个事情?

这篇论文要解决什么问题?

现在的高速 ADC 已经能做到几十 GS/s,但带宽还不够,实际要用在:

光通信 (coherent optical receiver)

6G / 毫米波雷达

测试测量仪器;都希望能直接采 20 GHz 甚至 30 GHz 的信号。注意!!! 是直接采集,就是一个超高速 ADC 的设计,不要各种频率的调节,就和低速 ADC 一样的用法。

先看这个

先看这个

现状痛点:

电子交织太多 (TI ADC)为了提高采样率,通常用好多小 ADC 交错采样;但一旦交织太多(几十甚至上百路),就会出现:

时间偏差 (skew)

通道带宽不一致 (BW mismatch)

相位误差、增益误差→ 导致高频严重失真,SFDR 掉得厉害。

输入缓冲带宽和线性度不够模拟输入链路往往是瓶颈,不能保证几十 GHz 的线性采样。因为不管怎么说,还是要吸收前级的信号能量做量化。

论文的核心思路:

“与其拼命校准,不如从电路根源把问题做小。”

论文的总体策略可以概括为四个关键词:

少就好,会减少一些问题

少就好,会减少一些问题

核心思路 | 通俗解释 |

|---|---|

少交织 | 每个子 ADC 速度更高,所以整体只需 64× TI(比常见的 128× 或 256× 少很多),从源头减少失配问题。 |

电路更线性 | 改进输入缓冲,让信号进来时不被“挤扁”或“压缩”。 |

开关更快 | 重新设计采样开关,让它在 20 GHz 信号下仍能精准抓到波形。 |

自身稳 | 让放大器、采样链自己稳,不需要繁琐的数字校准。 |

关键电路设计思路

输入缓冲:防止信号被“压扁”

普通缓冲器(源极跟随 SF)在输入信号大、频率高时,容易“踩到底”或“跟不上”,相当于:“音响声音太大,喇叭开始破音”。作者给 SF 加了一个“智能补偿电路”,就像给喇叭加了一个自动反相补偿器,当输出开始“压缩”时,补偿电路产生相反的失真来“抵消”它。这个补偿还会随着频率自动调整(高频时补得更多),所以叫“自适应频率线性化”。

结果:信号越大、频率越高,波形越不被压。 → SFDR 提升约 4 dB,带宽提升 20 %。

什么是源极跟随器(Source Follower, SF)

基本结构

以 NMOS 为例:输入接栅极 (VIN),输出从源极 (VOUT) 取出,漏极接 VDD 经电流源或电阻上拉。

主要特征:

也就是说:输出跟随输入变化,但有一个 VGS 的偏移。

它的核心作用是:

把高阻输入 → 转换成低阻输出,作为“缓冲器(Buffer)”隔离信号源与后级电路。

在高速 ADC 里的作用

在高速采样系统中(例如本文 72 GS/s ADC):信号频率可高达 20 GHz 甚至 40 GHz;采样电容只有 几十 fF;前级驱动必须有足够带宽与推送能力,否则波形被压缩失真。

因此 ADC 前面通常加一到两级源极跟随器:

信号源 → 输入 SF → 子缓冲 SF → 采样开关

目的:降低输入阻抗;提供大电流驱动采样开关;抑制信号源与开关之间的 kickback 干扰;维持高线性度和宽带响应。

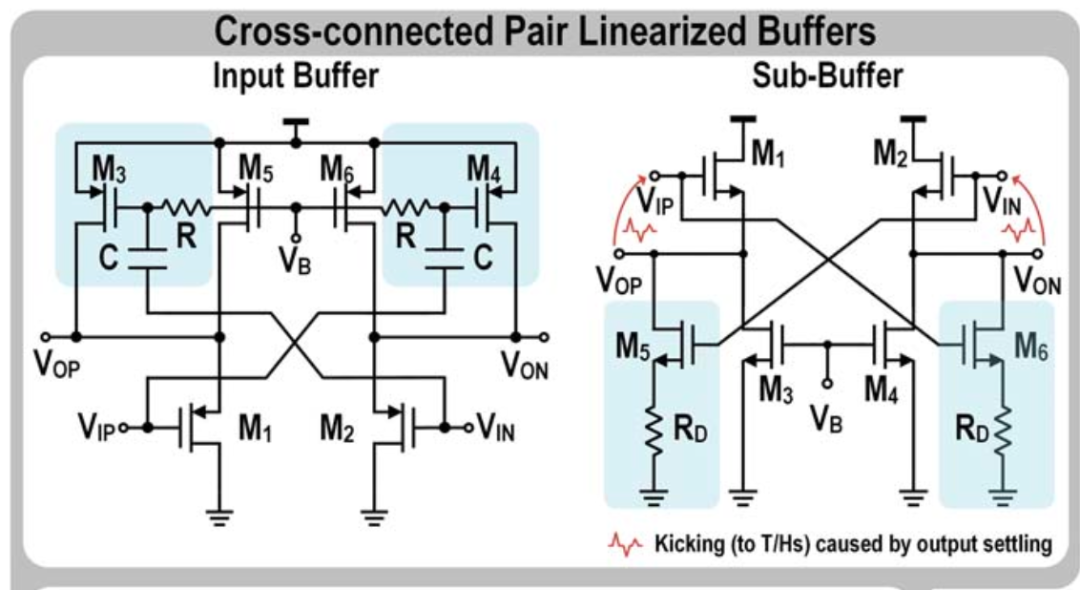

Cross-connected Pair Linearized Buffer

Cross-connected Pair Linearized Buffer

论文的改进:交叉线性化源极跟随器

电路结构

在传统差分 SF (M1–M4) 上方,作者增加了一对交叉耦合 PMOS (M5–M6) 并通过 R–C 网络耦合到输出端。

VIN+ → M1 ─┐

├─► VOUT+

VIN− → M2 ─┘

↑ M5–M6 交叉补偿 + R–C 耦合

工作原理

当主 SF 输出发生“压缩”(gm 减小)时,交叉 PMOS 会通过 C 注入反相信号电流;这种补偿电流在高频时更强(因 R–C 为高通特性);结果是整体 gm 曲线被“拉直”,高频幅度不再衰减。

这是一种“自适应频率线性化”技术。

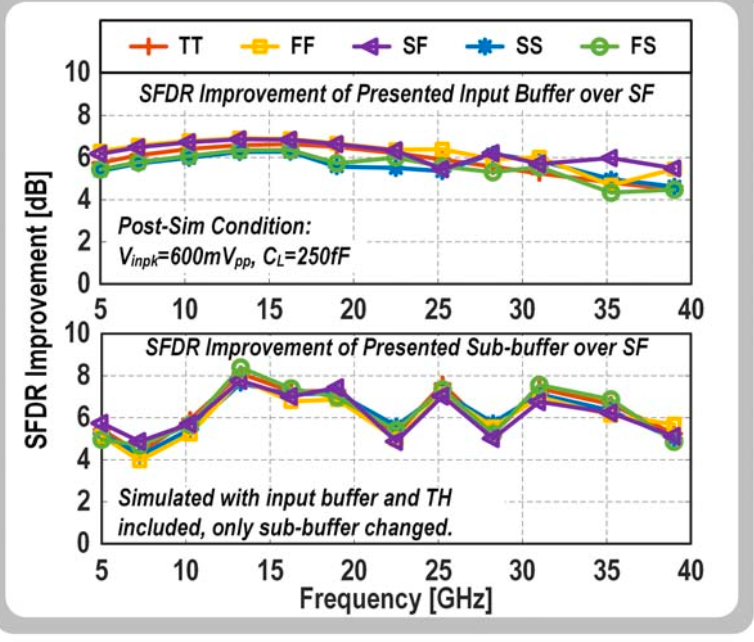

效果(论文仿真)

效果(论文仿真)

SFDR 提升 4 ~ 6 dB;slew 率提升 20 %以上;带宽延伸至 > 30 GHz;补偿电容仅 ≈ 5 % 负载,不损耗带宽。

再进一步:子缓冲 (Sub-Buffer)

论文里 SF 链分两级:

- 输入 SF:主线性化 R–C 补偿;

- 子缓冲 SF:驱动 T/H 阵列(不带 C,只用 RD 稳压),减少“输出踢返(kickback)”并提高相位一致性。

极跟随器(SF) 是高速 ADC 输入链中的关键缓冲级,论文通过在差分 SF 上增加交叉耦合 R–C 补偿支路, 实现了频率自适应线性化,在 20–40 GHz 范围显著提升 SFDR 与带宽,成为该 72 GS/s ADC 能保持 55 dB 线性的根本原因之一。

采样开关:抓波形要又快又稳

普通自举开关(Bootstrap)在 20 GHz 信号下常“关不干净”或“抬不够高”。

作者提出“双通道自举”:

相当于让开关的“推门手”有两条胳膊:一条专门抬电压,另一条帮忙控制寄生电容, 所以能抬得更高、更快。

同时加了 dummy 开关 把漏电流在高频下抵消掉。

结果:Track 时间缩短 ≈ 27 ps → 高频 SFDR 提升 > 10 dB。

单元 ADC:Pipeline + SAR 混合架构

就是这样

就是这样

一般高速 ADC 都是 SAR 或 Flash,但是这篇用“两级 Pipeline-SAR”:第一级 4 bit,第二级 6 bit;中间靠一个固定增益放大器传递残差。

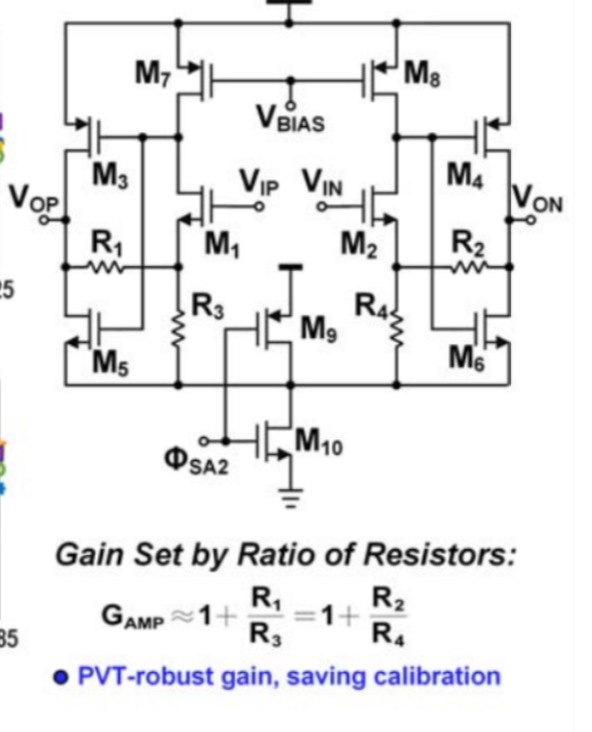

其中的放大器不是传统运放,而是开环电阻反馈 R/R 放大器,就像一个不需要精调的“自动齿轮箱”,增益自然稳定在 6×,温度、电压变化都不敏感;所以它不需要级间增益 (ISG) 校准。

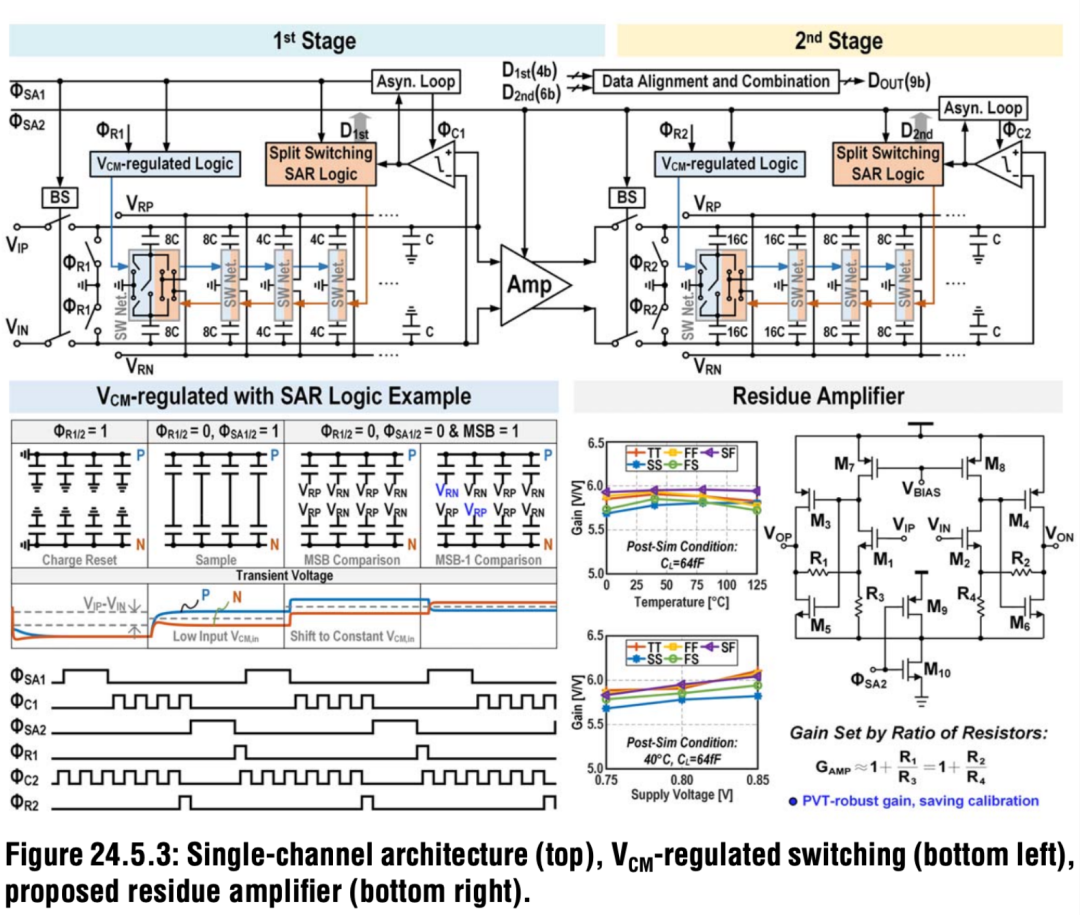

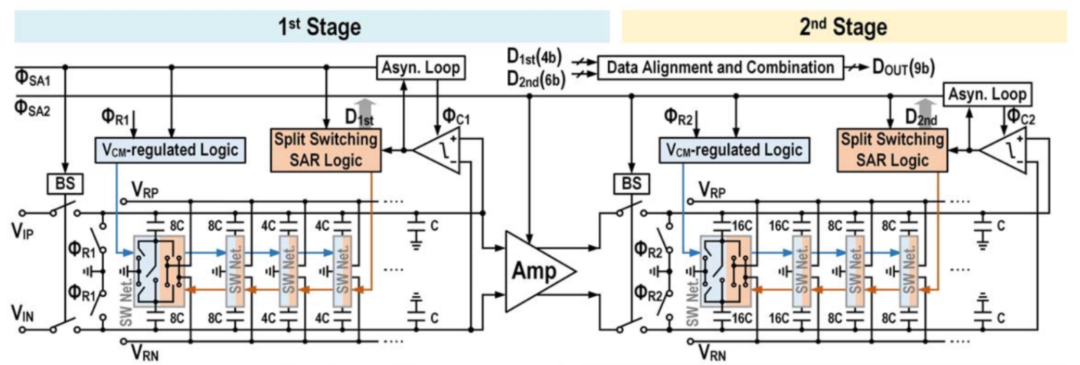

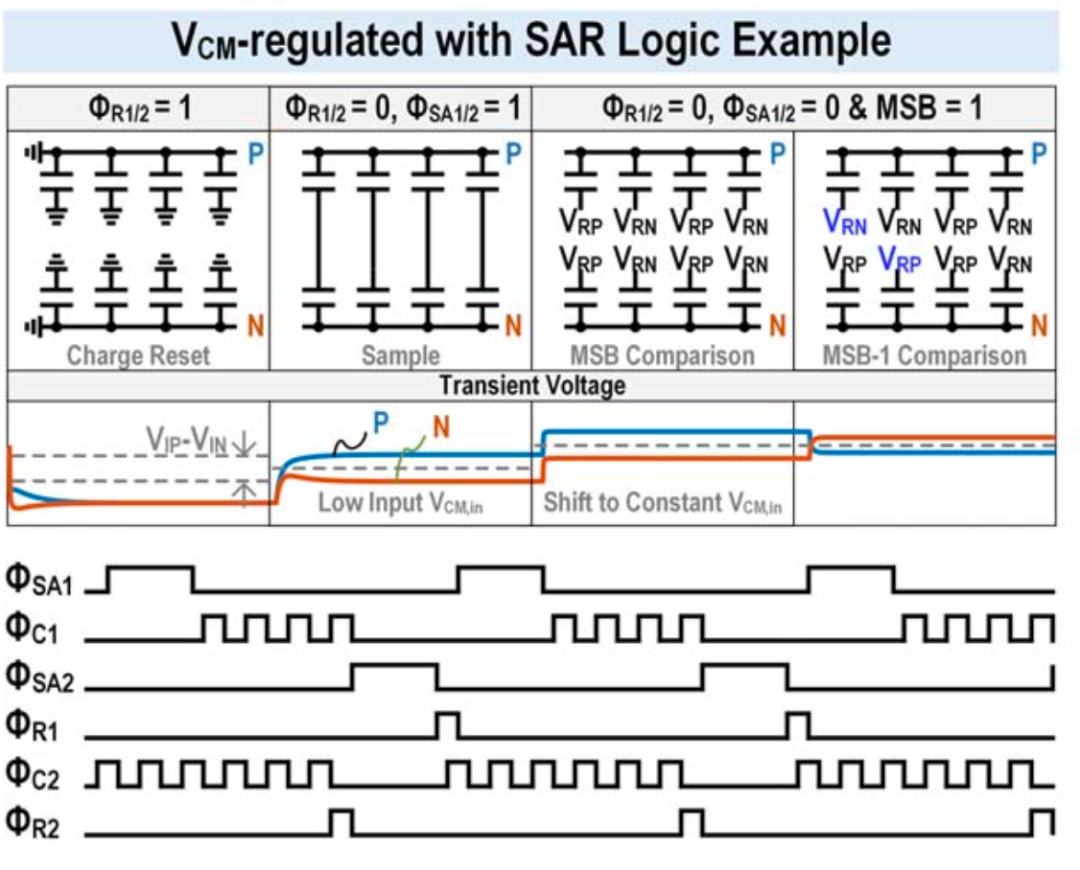

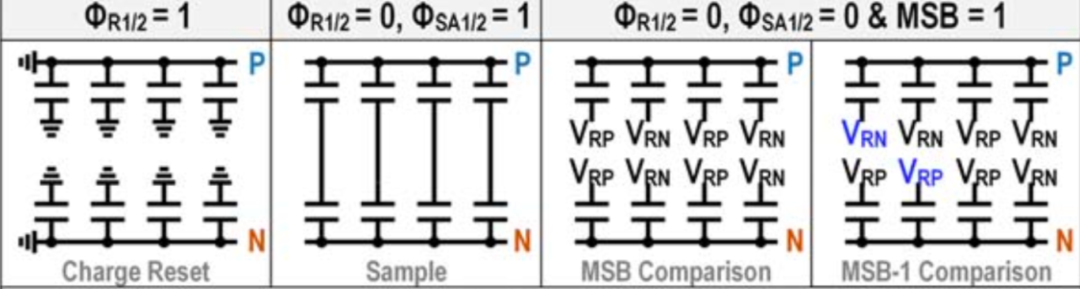

这页图说明了三件事:每个子 ADC 的整体结构与时序; VCM-regulated split switching 技术如何减少失调与动态误差; 残余放大器 (Residue Amplifier) 如何实现 PVT 稳定、无需校准的固定增益。

两级 Pipeline-SAR 架构

两级 Pipeline-SAR 架构

它由两级串联的 SAR 转换器组成,中间用一个开环电阻放大器 (R/R Residue Amplifier) 连接。

每个通道由两级串联组成:

Stage | 分辨率 | 特点 |

|---|---|---|

1st Stage | 4 bit(含 1 bit 冗余) | 高速采样、粗量化 |

2nd Stage | 6 bit | 精细量化 |

两级合起来为 9 bit 输出。中间有一级残余放大器 (Amp),将第一级的量化残差放大并送入第二级。

信号流向

BS:自举采样开关,从输入取样差分信号。

C-DAC 阵列:电容数字-模拟阵列,采用Split switching(分裂式开关结构),以减小切换能耗与电荷注入。

啊啊啊

啊啊啊

VCM-regulated Logic:控制底板电压,使采样相位结束后两端共模稳定。

ΦR1/ΦR2:复位阶段时钟,确保每次采样周期残差清零。

Amp:残余放大器(下方右图),实现固定倍数增益。

输出 D₁st(4b)、D₂nd(6b) → 数字组合对齐后输出 Dout(9b)。

左下部分:VCM-regulated Split Switching 工作原理

在高速 SAR ADC 中,每次采样和比较后,电容阵列的底板电压都会变化,导致:输入共模 (VCM,in) 随周期漂移;输出基线不稳定;残差放大器输入偏移大。

本文改进

VCM-regulated switching → 让电容阵列在每个比较阶段保持恒定的共模电压。

工作过程电容图:

image-20251024114049608

ΦR1/2 = 1(Charge Reset):所有电容复位,底板电压被拉至固定 VRP/VRN。

ΦSA1/2 = 1(Sample):采样输入差分信号 VIN+/VIN−。

ΦR1/2 = 0 → MSB 比较阶段:通过调整电容连接极性,使输出节点电压围绕固定 VCM 变化(蓝色虚线区域)。

这样在比较阶段,放大器输入保持稳定共模,避免了传统 SAR 的“共模漂移”。

残余放大器(Residue Amplifier)

image-20251024114156399

两级差分放大器,采用 R/R 电阻反馈结构;由 M1–M6 组成跨导级,M7–M8 提供电流镜负载,M10 为复位开关。

增益由电阻比决定:

与晶体管 gm、温度、电源几乎无关。

优点

开环结构,无需传统运放补偿 → 高速;增益由 阻值比 固定 → PVT 稳定;不需要额外 ISG (Inter-Stage Gain) 校准。

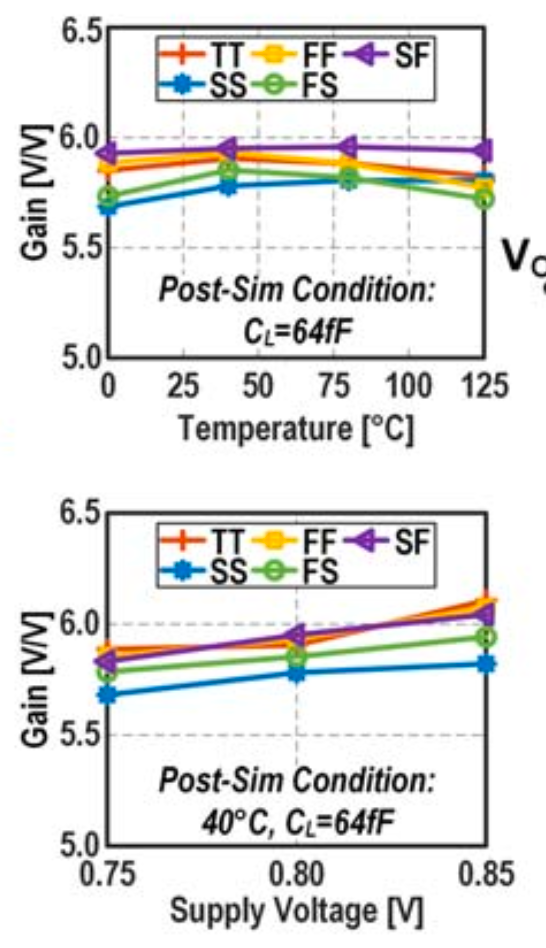

仿真

仿真

两张图显示:

变量 | 范围 | 增益稳定性 |

|---|---|---|

温度 | 0–125 °C | 变化 < ±1 % |

电源电压 | 0.75–0.85 V | 变化 < ±2 % |

→ 表明它能在宽工况下维持固定 6× 增益。

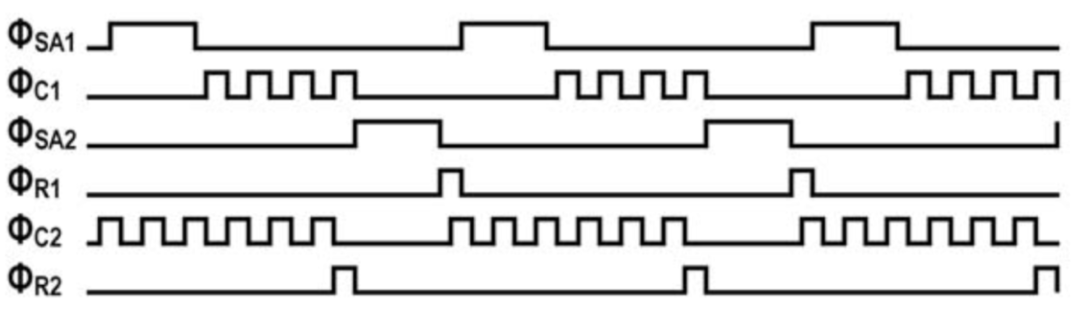

时序

时序

信号 | 作用 |

|---|---|

ΦSA1/ΦSA2 | 各阶段的采样/保持控制 |

ΦR1/ΦR2 | 复位电容与放大器 |

ΦC1/ΦC2 | 残差比较与输出更新 |

每个 Stage 的时钟交错运行,实现 Pipeline 工作;当 Stage1 进行比较时,Stage2 同时在采样下一帧,提高利用率。

模块 | 技术改进 | 效果 |

|---|---|---|

VCM-regulated switching | 固定输入共模,抑制动态失调 | SNDR/SFDR 改善;共模漂移 < 2 mV |

Split switching | 电容分裂连接 | 降低功耗 20–30 % |

R/R 残余放大器 | 固定增益、PVT 稳 | 无需 ISG 校准;节省数字校准功耗 |

两级异步 SAR | 异步控制环路 | 降低比较延迟、加快转换速度 |

这张图展示了论文单通道 Pipeline-SAR 的“精密内部结构”:第一阶段 进行粗采样 + VCM 控制的 split-SAR 量化;残差放大器 用电阻比确定固定增益;第二阶段 精量化残差。

全电路实现了 高速度(1.125 GS/s/通道) 与 高稳定性(无需增益校准),是 64× TI ADC 实现 72 GS/s 的关键基础单元。

时钟与交织:每一拍都对齐

image-20251024114617670

image-20251024114617670

时钟来自 36 GHz 差分信号,经分频与移相得到多相时钟,每个通道采样的相位可微调到 12 fs(飞秒) 级;非重叠时钟避免两个通道同时“抢”输入信号 → 时序误差控制在极限范围内。

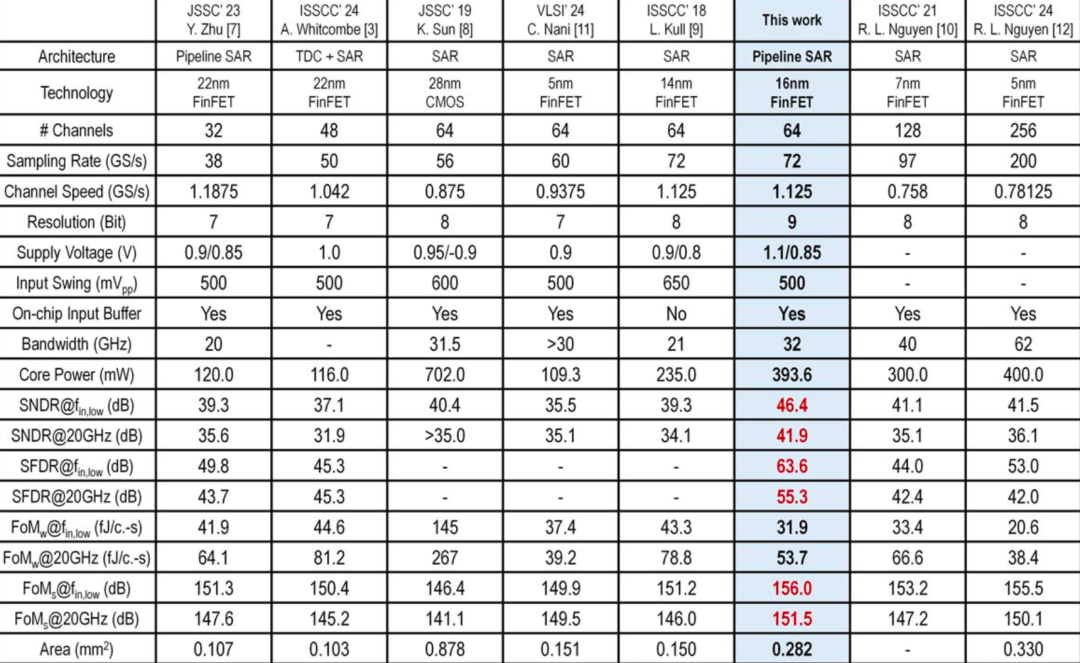

测试成绩一览(实测)

测试成绩一览(实测)

项目 | 数据 |

|---|---|

工艺 | 16 nm FinFET |

面积 | 0.282 mm² |

功耗 | 393 mW |

采样率 | 72 GS/s |

分辨率 | 9 bit |

输入带宽 | > 32 GHz |

SFDR | 55.3 dB @ 20 GHz; 49.3 dB @ Nyquist |

SNDR | 37 dB @ Nyquist |

FoMw | 53.7 fJ/conv-step |

FoMS | 151.5 dB |

这意味着它在 > 20 GHz 输入时,仍能保持接近 9 bit 线性度,已经是目前同类高速 ADC 的领先水平。

这篇论文不是靠“花哨算法”赢,而是靠:硬件前端的物理优化 + 简化交织结构 + 智能自举/补偿电路,做到了在 20 GHz 输入下 SFDR 55 dB、72 GS/s、9 bit。

学术一点的解读

感谢可以看到这里的小朋友,现在是学术时间。

论文瞄准近百 GS/s 级采样、>20 GHz 输入带宽场景(光模块/宽带射频接收),在超大 TI 因子下依然保证宽带 SFDR/SNDR。传统只做“时序偏差(skew)校准”不够,因为带宽失配与交织隐含失真同样是瓶颈。该作业通过减少 TI 因子(提升单通道速率)+ 输入级线性化 + 采样开关加速,把 20 GHz 输入的 SFDR 推到 55 dB 以上,同时在 Nyquist 处也保持 49.3 dB 的 SFDR,Nyquist SNDR 达 37 dB(9b 设计) 。

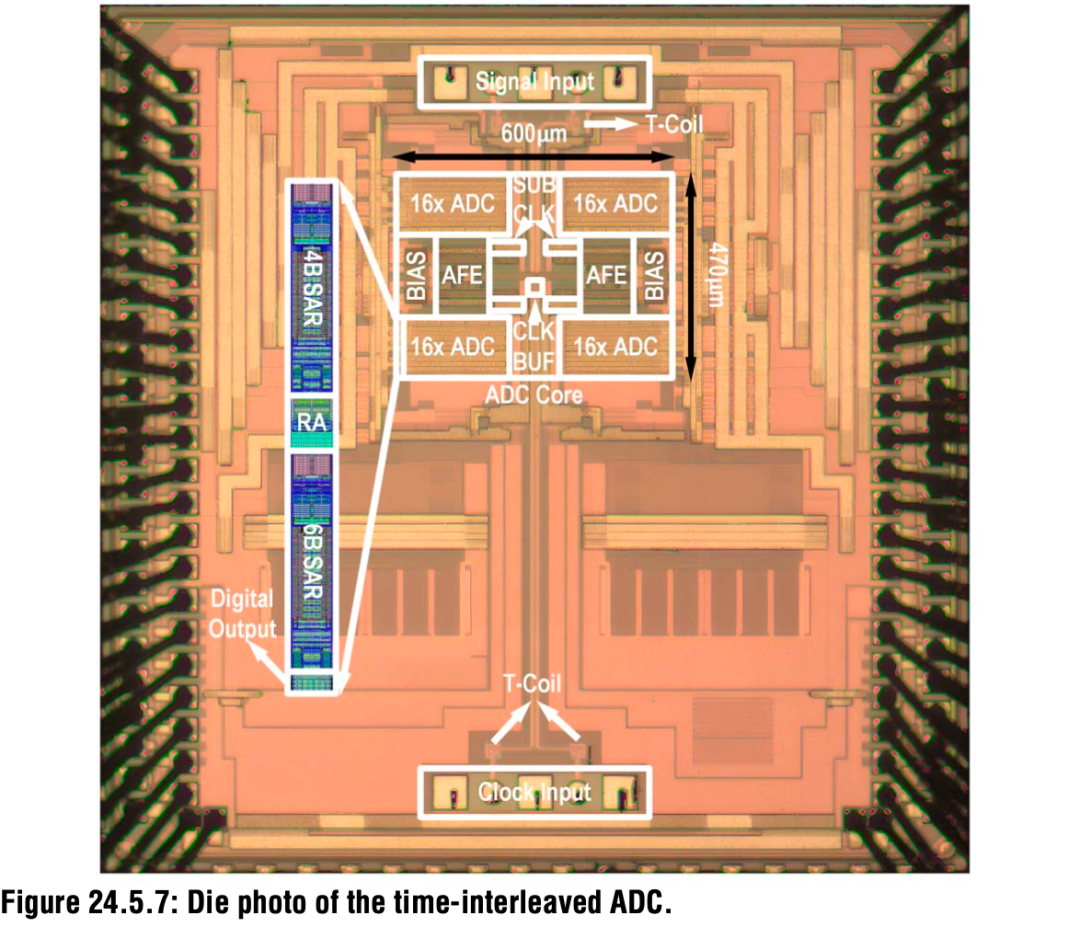

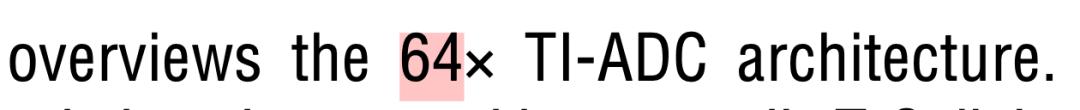

顶层架构:64× TI,两级分层交织 + 双缓冲供驱

输入端:片上 T-Coil 与 50 Ω 终端、ESD 集成,扩展带宽并做静电/阻抗处理。输入之后通过双输入缓冲驱动两级分层交织:第 1 级 16×,第 2 级再扩到 64×。每个第 2 级子缓冲服务 4 个单元 ADC。

单元 ADC:为两级 pipeline-SAR(首级 4b、次级 6b,级间 1b 冗余,1.125 GS/s/ch × 64 = 72 GS/s)。输出合并后再做2295 倍抽取便于表征。

输入采样:第 1 级 T/H 逐次开启,27.78 ps track 时间;同组采样时钟非重叠,抑制通道串扰。

时钟与交织时序

片外 36 GHz 差分时钟进来,片内电流分频产生四相 18 GHz(90° 相移)。再经 8/16 相选择生成 ΦTH0-15(第 1 级 T/H)与 ΦS0-63(单元 ADC)。STDL 提供粗/细 skew 调节,细步进约 12 fs;并在关键沿加入额外缓冲整形抖动。

输入链路的两记“杀手锏”

宽带线性化源极跟随(SF)缓冲

传统 SF 能效高但小于 1 的增益、线性差、slew 限制在高频更糟。本文提出:在 P 型 SF 上叠加交流耦合的 CC-PMOS 对(带 R-C 高通),构造“扩张型”补偿对抗 SF 的“压缩型”非线性,并让补偿随频率一阶自适应(HPF)。

实际设计把补偿对的电容占比控制在<5%,避免带宽损失。效果:在0 dBFS、≤40 GHz 输入下,SFDR 提升 ≥4 dB,slew与带宽分别提升 >20% 与 12%。子缓冲也用类似线性化(去掉 HPF,改用 RD 稳定补偿)。

双通道(dual-path)自举采样开关(BS)

27 ps 的短 track 使传统 BS 很难“又快又稳”。本文把输入电平移位控制“拆两路”,将关键节点 VBST 上的寄生 CP 明显减小(去掉主路上的 M2 与其控制支路),rise/fall 分别加速 1.5×/1.2×;在总自举电容不变下把 CB 分裂成 CB1/CB2,优先提高 M1 的过驱动,使名义提升电压增加 >150 mV,有效 track 时间增加 >5.2 ps,20 GHz 以上 SFDR 进一步 +10 dB。

再配合交叉 dummy + dummy BS 抑制高频漏馈;相比“只下拉 dummy”方案,能把栅相关漏馈压到 <1 LSB。

单元 ADC:两级 pipeline-SAR,R/R 开环残余放大器免 ISG 校准

量化分配俩级,Stage1 = 4b,Stage2 = 6b,1b 冗余;后面用 R/R 开环放大器(级联 CS + 电阻反馈 R1/R3),闭环等效增益 ≈ 1 + R1/R3 = 6,实现 PVT 稳定的 ISG,从而省掉级间增益校准;仿真显示在 0–125 °C、±5% 电源、全工艺角下增益变化 <2%;用“复位后短接底板”时序把输入 VCM 拉到 (VRP+VRN)/2,并在 SAR 切换期间恒定 VCM,in;两级都插入 ΦR1/2 复位,抑制 ISI。

标定策略:只做“该做的”,其余靠电路本身顶住

前台(foreground)做 TI 偏置/增益与级间偏置校准;时序上面用 Nyquist 输入做片外估计,然后片内一次性靠 STDL 修正;带宽失配与ISG,不做校准(电路级方案已把它们压下去)。

这篇论文的“工程含金量”在哪里?

把系统瓶颈前移到“输入链路”去解决:通过自适应线性化 SF,在极宽带下仍保持低失真与推送能力;用双通道 BS把turn-on/off 动作做得更快更稳,并细抠VBST 寄生与 Vov 分配,直击高频 SFDR。

以单通道更高的 fs 换更小 TI 因子:在 72 GS/s 的目标下,单通道 1.125 GS/s 的 pipeline-SAR 方案,显著减少交织失真与带宽失配来源;再辅以R/R 残放消除 ISG 校准负担,系统复杂度与风险都下降。

校准“做减法”:只保留对产线与长期漂移最“值当”的项目(offset/gain、一次性 skew),其他通过前端电路物理优化兜住,利于量产一致性与部署。

后记

写到后面我已经不知道是什么了,但是感觉基本的电子学知识还是在工作,总之就是这样的架构,希望你看的开心。

感谢 zub 的账号,不然 IEEE 的论文还是不好下载的

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-10-24,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录