OFC 2025:TSMC低损耗PECVD氮化硅平台

台积电在这个工作中报道了SiN-on-SOI平台的工作,其中氮化硅采用PECVD工艺低温沉积,以减少对硅有源器件的热影响。但低温PECVD氮化硅的质量和均匀性不如高温LPCVD工艺,因此进行了工艺优化。(台积电的SOI的硅层采用270nm,目的是为了提升光栅耦合器的耦合效率和无源器件性能;Intel的硅光同样是选了一个400nm的厚度,GF也报道过160nm的SOI器件,CEA-Leti有个310nm顶硅的选项,总之好多都不是常规的220nm😂)

◆ 优化成果

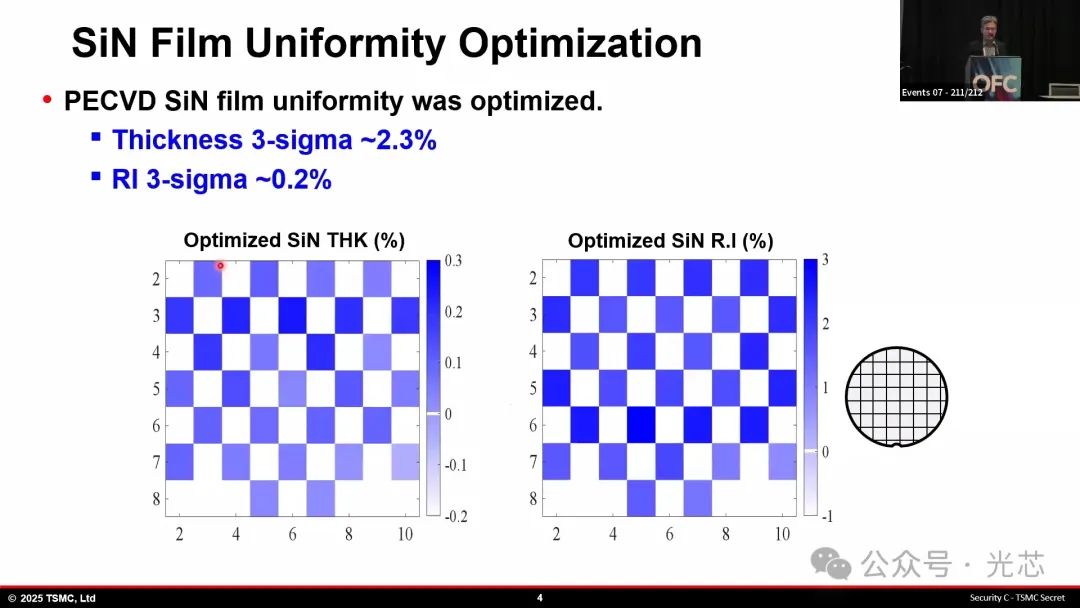

显著改善了PECVD氮化硅的均匀性,厚度和折射率范围得到优化,3σ厚度和折射率值分别仅为2.3%和0.2%,有效折射率范围优化后提升超过50%,减少了MZI级联在复用和解复用应用中的中心波长漂移,从7nm降到了4nm。

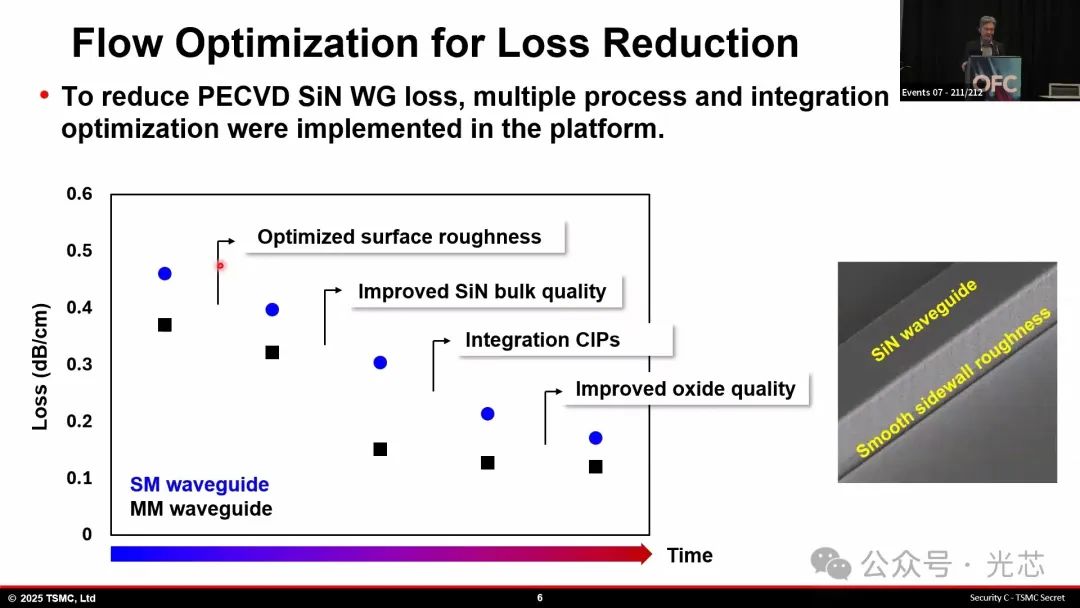

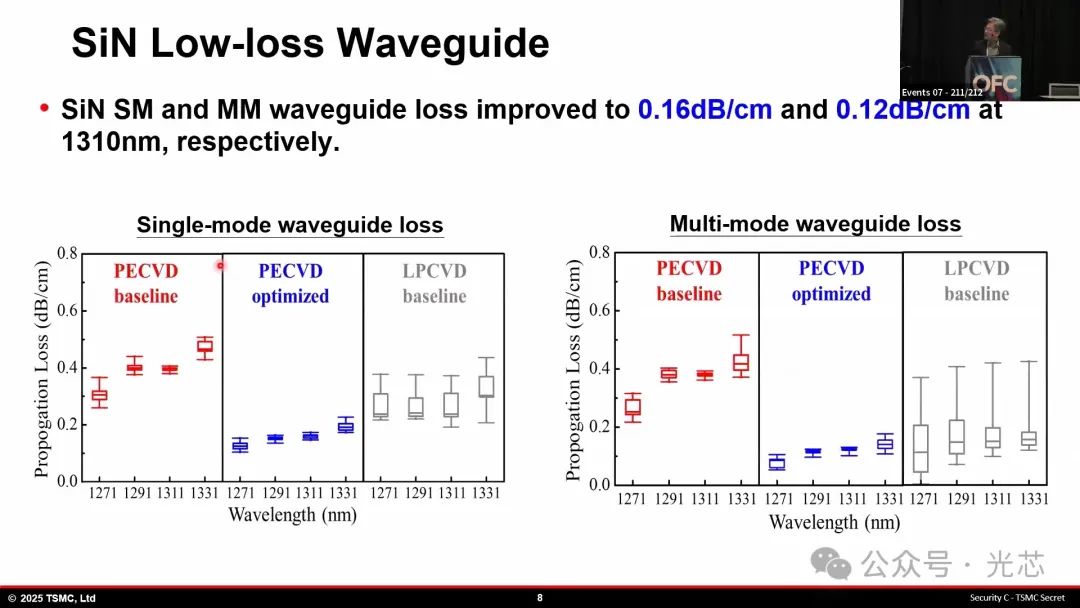

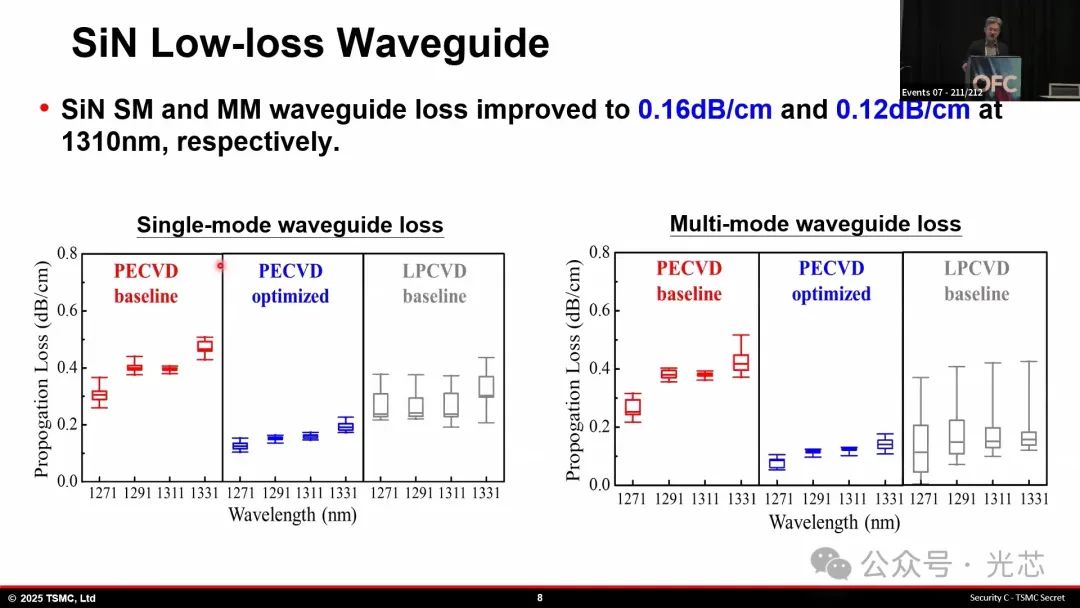

通过多种工艺优化,降低了氮化硅波导传播损耗,优化后单模和多模波导在1310纳米处的损耗分别降至0.16 dB/cm和0.12 dB/cm,低于未优化的LPCVD工艺损耗。

◆ 组件性能

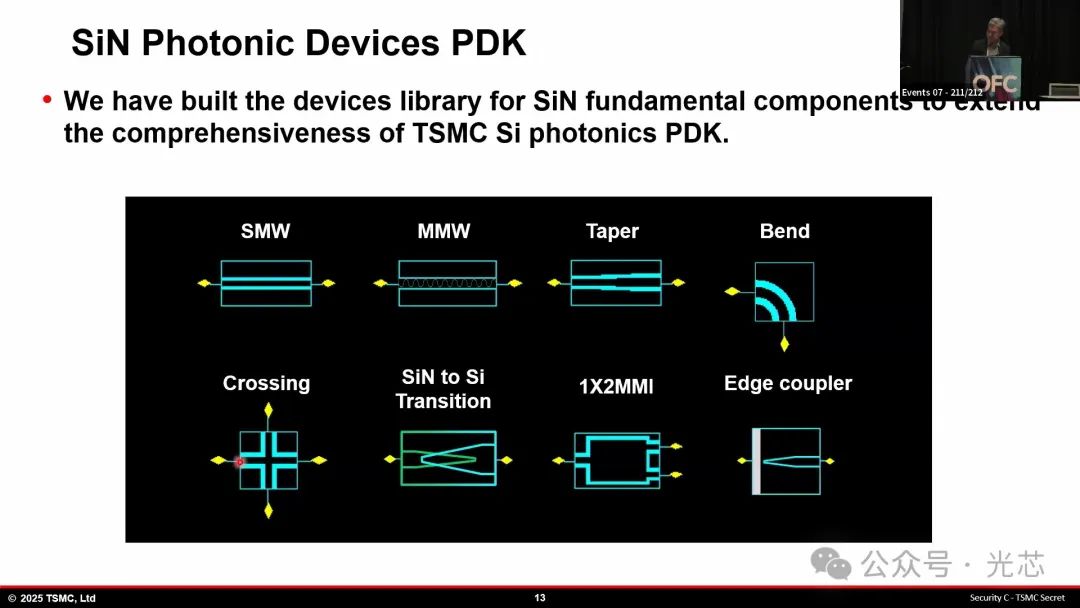

介绍了氮化硅基本组件的性能,包括

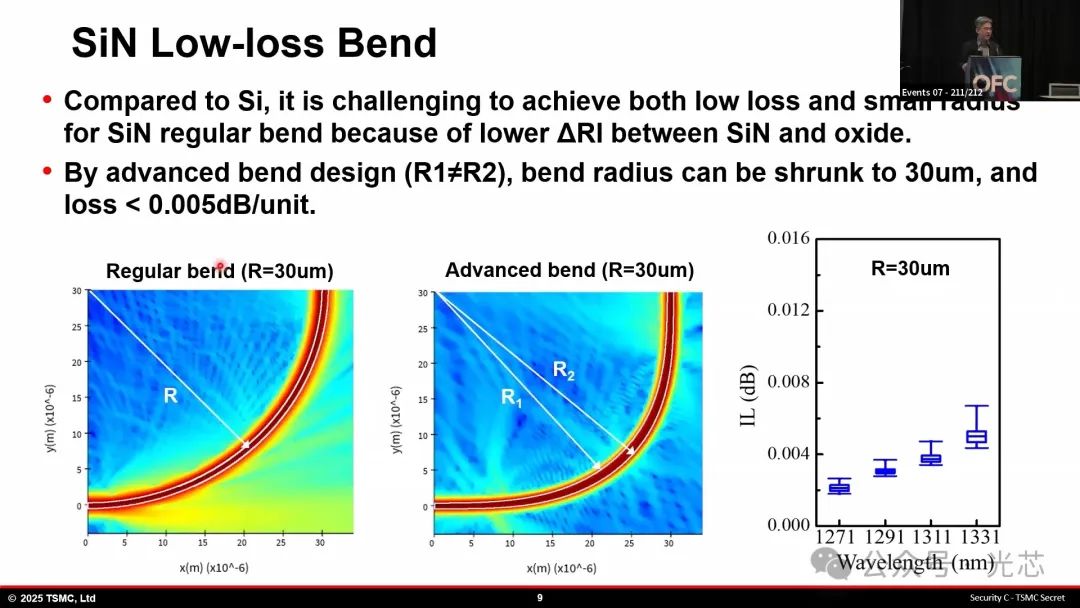

①设计了先进弯曲结构,在30 um半径下损耗为0.005 dB;

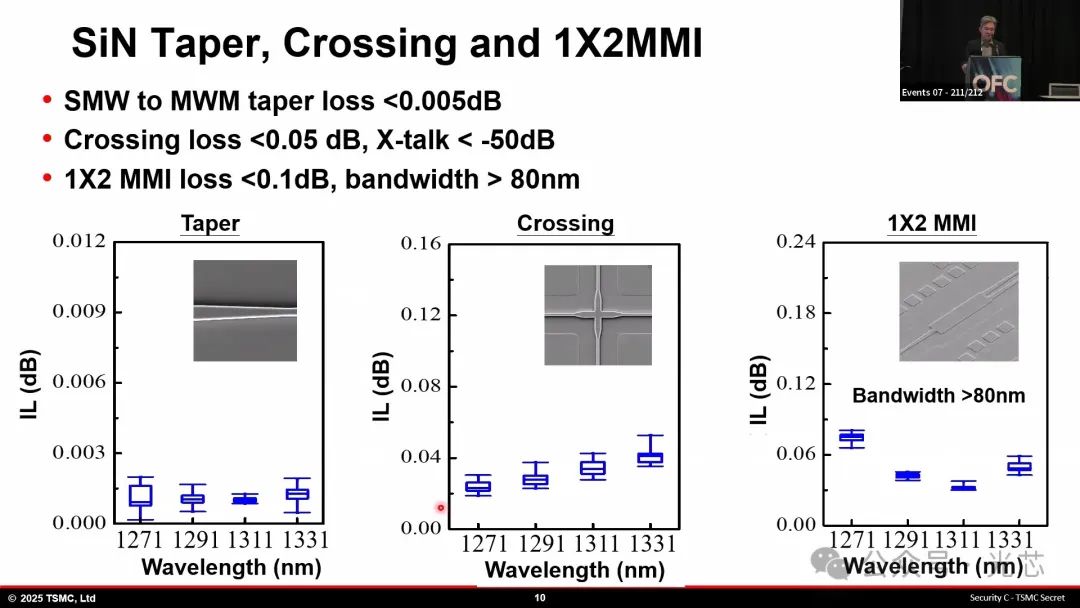

②单模转多模波导Taper损耗小于0.005 dB;

③波导交叉损耗约0.05 dB,串扰小于 - 50 dB;

④1×2 MMI损耗约0.1 dB,带宽超过80nm。

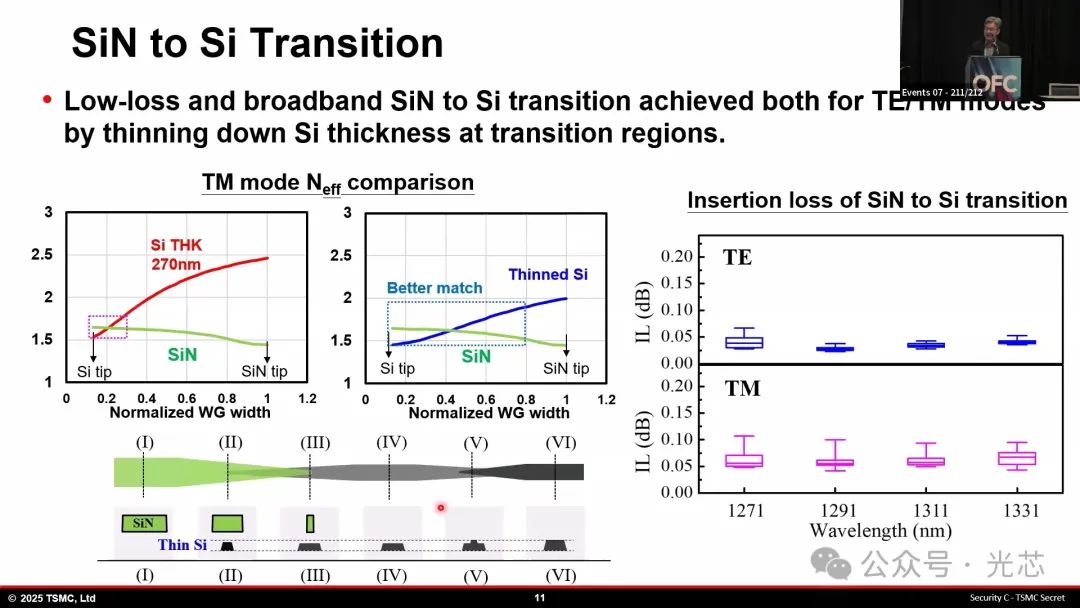

⑤SiN - Si的Transition,采用二次刻蚀工艺形减薄过渡区域的硅形成双层taper结构,使TE和TM模式在O波段60 nm波长范围内都能够实现低插损过渡,插入损耗约为0.05 dB。

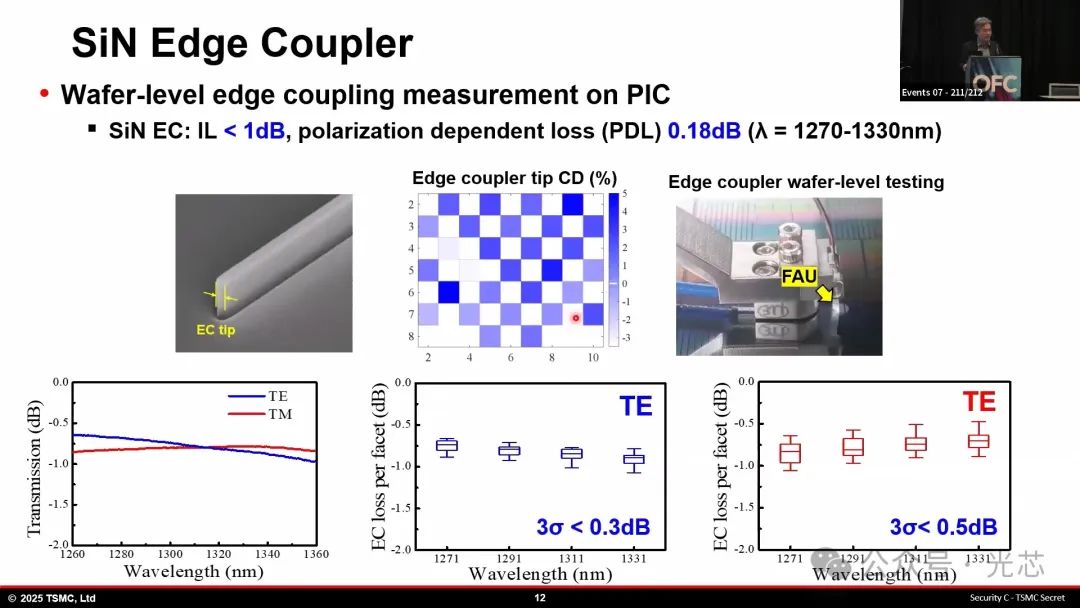

⑥ SiN端面耦合器通过光刻和蚀刻工艺优化,具有良好的均匀性,TE0和TM0插入损耗均小于1 dB(8通道 小模场光纤),偏振相关损耗小于0.2 dB,损耗3σ约为0.3 - 0.5 dB,带宽超过100纳米。

总的来说,台积电在这里报道的还是他们初步的开发结果,这个结果在PECVD SiN-on-SOI平台里边算是挺不错的了,以TSMC的工艺能力还是有不少优化空间的,未来看是不是也会走向集成LPCVD氮化硅,获得更优异的无源性能。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-04-14,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读