深入理解DRAM(全文·万字30+图)

深入理解DRAM(全文·万字30+图)

数据存储前沿技术

发布于 2025-02-11 16:42:52

发布于 2025-02-11 16:42:52

按:本文是深入理解DRAM1-4的合集,整合后略有改动,文章较长。

DRAM 现况与原理

DRAM 现况

DDR(Double Data Rate)内存的总带宽计算公式可以简化为:

总带宽=数据传输速率 × 位宽总带宽 × CPU内存控制器通道数。

其中,“数据传输速率”是指每个时钟周期内单个引脚的数据传输速度,而“位宽”则代表了连接到内存控制器的引脚数量。

在DDR内存中,位宽通常指的是内存模块上可用的数据线的数量,以比特为单位。例如,常见的DDR3和DDR4内存条的位宽有64位、128位等。

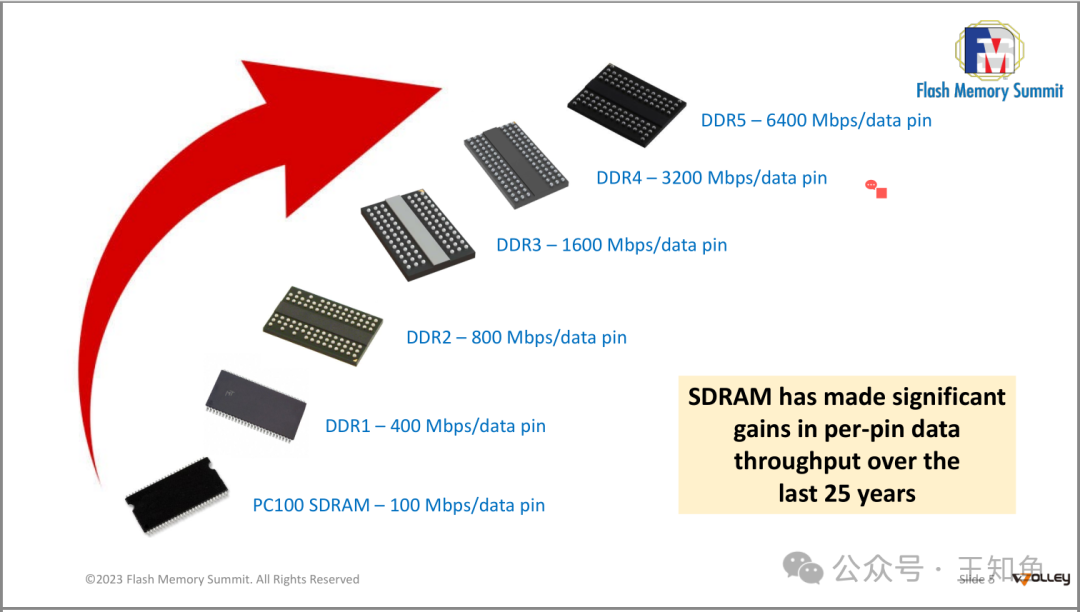

然而,随着技术的进步,DDR内存标准经历了多次迭代,从DDR到DDR2、DDR3、DDR4,再到现在的DDR5,数据传输速率有了显著提升。

DDR5相较于前代DDR4,不仅提高了数据传输速率,还增加了单个内存模块上的通道数,从而提高总带宽。

尽管如此,引脚数量受到物理限制和成本控制的影响,并不是无限增加的。因此,提高内存带宽的主要途径是提高数据传输速率,以及优化内存架构,比如DDR5引入的双通道设计,可以在不增加引脚数量的情况下提高总带宽。

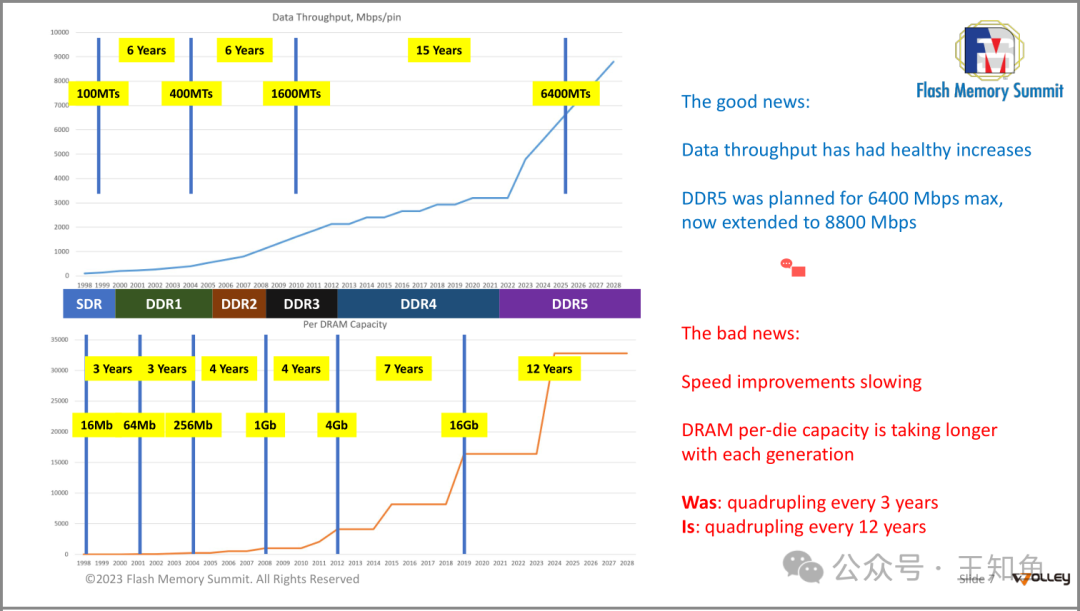

图中的两个图表分别展示了数据传输速率的增长和DRAM芯片容量的增长情况。

数据传输速率主要取决于以下几个因素:

- 1. 技术进步:随着工艺技术的改进,能够实现更快的数据传输速率。例如,更先进的制造工艺允许晶体管之间的距离变得更小,这有助于提高信号传输的速度。

- 2. 内存标准:新的内存标准通常会带来更高的数据传输速率。例如,从SDR到DDR5,每次新标准的推出都会显著提高数据传输速率。

- 3. 设计优化:内存控制器和其他相关硬件的设计也会影响数据传输速率。例如,增加并行处理能力或者改善信号完整性都可以提高数据传输速率。

DRAM芯片容量的增长主要受以下因素影响:

- 1. 制造工艺:随着制造工艺的进步,能够在相同面积的晶圆上集成更多的存储单元,从而提高单个DRAM芯片的容量。

- 2. 存储单元设计:改进存储单元的设计也可以提高密度,例如采用更小的电容或者更高效的电路布局。

- 3. 多层堆叠:现代DRAM芯片可以通过将多个存储层堆叠在一起来增加容量,这种方法称为高密度堆叠技术。

然而,正如图像所示,虽然数据传输速率一直在稳步增长,但是DRAM芯片容量的增长速度已经放缓。这是因为随着技术的发展,提高芯片容量变得越来越困难,尤其是在达到一定水平后,每一代产品的容量提升所需的时间明显延长。

DRAM 器件原理

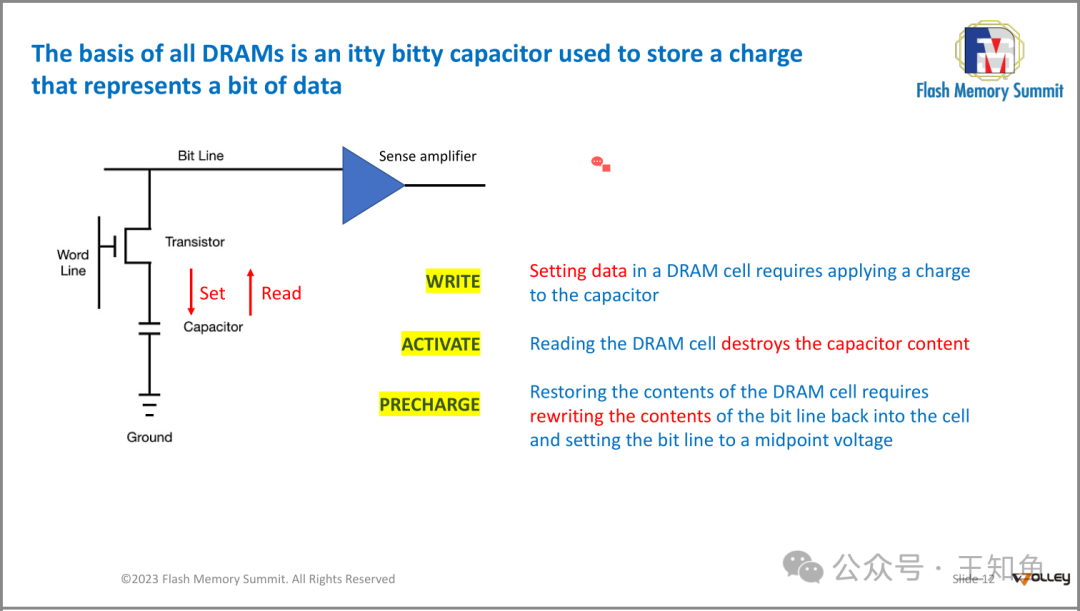

DRAM的基本单元由一个电容器和一个晶体管组成,用于存储一个二进制位(0或1)。以下是DRAM单元操作的简要说明:

- 1. 数据写入:

- • 当要向DRAM单元写入数据时,首先激活(ACTIVATE)该单元,使能晶体管,允许对电容器进行充电或放电。

- • 根据要写入的数据位(0或1),电容器会被充至不同的电压水平。如果要写入0,则电容器保持接地;如果要写入1,则电容器被充电至电源电压Vcc。

- 2. 数据读取:

- • 要读取DRAM单元的内容,首先激活(ACTIVATE)该单元,然后使用感测放大器(Sense amplifier)检测电容器的电压状态。

- • 感测放大器是一个高度敏感的放大器,它可以从电容器中提取微弱的电压信号,并将其转换成逻辑0或1。

- • 然而,在读取过程中,由于漏电流等原因,电容器的电压可能会发生轻微变化,导致其内容被破坏。

- 3. 预充电(数据重写):

- • 为了避免数据丢失,读取之后必须重新写回(PRECHARGE)电容器的内容。

- • 在读取操作完成后,关闭晶体管,断开电容器与位线的连接。

- • 使用预充电操作将位线电压设置为中间值(即,介于0和Vcc之间的一个电压),并将电容器的电压恢复为其原始状态。

- • 如果原始数据位是0,则电容器保持接地;如果是1,则电容器被充电至Vcc。

- • 最后,再次激活(ACTIVATE)单元,使能晶体管,将位线电压重新加载到电容器中。

这个过程确保了DRAM单元中的数据始终保持最新且可访问。请注意,DRAM需要定期刷新,因为电容器会逐渐泄漏电荷,如果不进行刷新,数据最终会丢失。这就是为什么DRAM被称为“动态”的原因——它需要不断更新以保持数据的有效性。

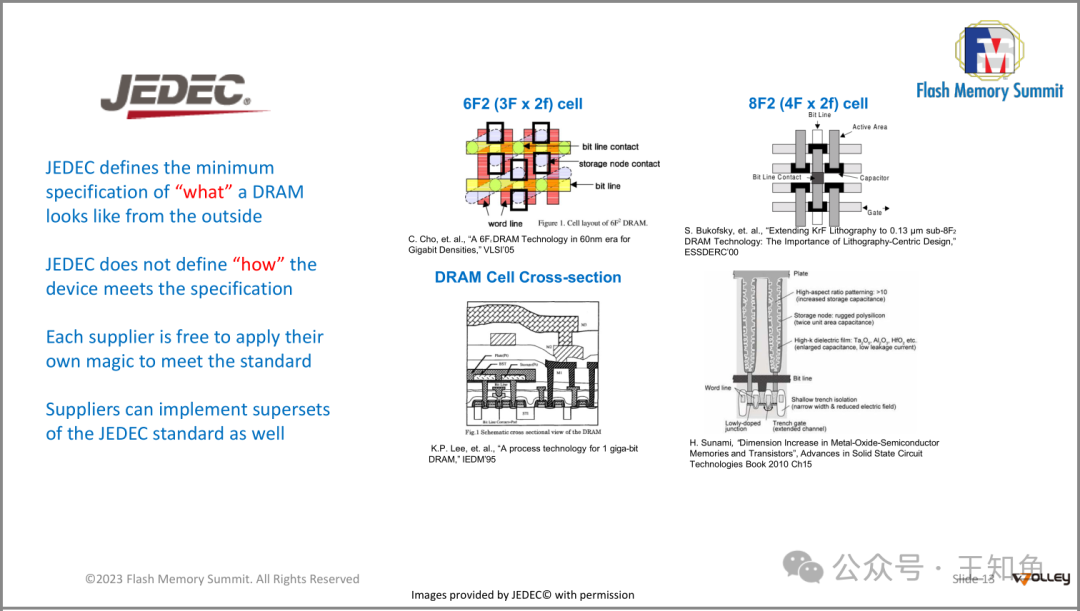

JEDEC(Joint Electron Device Engineering Council)是一家全球性的行业组织,负责制定电子设备的标准,特别是在半导体领域。在DRAM(Dynamic Random Access Memory)领域,JEDEC扮演着至关重要的角色,因为它定义了DRAM器件的外部规范和接口标准。这些标准包括但不限于封装尺寸、引脚分配、电气特性、时序要求等等。具体来说,JEDEC在DRAM领域的主要作用如下:

- 1. 标准化: JEDEC制定了各种类型的DRAM(如SDRAM, DDR SDRAM, GDDR, LPDDR等)的技术规格,使得不同制造商生产的内存产品具有互换性和兼容性。这意味着任何符合JEDEC标准的DRAM芯片都可以在任何支持相应标准的主板或其他设备上使用,无需担心兼容性问题。

- 2. 促进创新: JEDEC的标准鼓励竞争和创新,因为它们提供了一种公平的竞争环境,所有公司都遵循相同的规则。这促进了技术的进步,因为制造商们专注于如何在满足标准的同时提高性能、降低功耗和降低成本。

- 3. 市场协调: JEDEC的标准帮助协调市场需求和技术发展,确保整个行业的同步发展。当新的DRAM技术出现时,JEDEC会发布相应的标准,以便制造商和消费者了解新技术的特点和优势。

- 4. 质量保证: JEDEC的标准确保了产品质量的一致性,这对于终端用户和系统集成商来说非常重要,因为他们知道购买的产品符合一定的质量和性能标准。

在图片中提到,JEDEC定义了DRAM看起来是什么样的,也就是它的外观和接口,但没有规定内部的具体实现方式。这就给供应商留下了空间去开发自己的技术和工艺来满足这些标准,这也是DRAM技术持续发展的驱动力之一。供应商可以根据自身的技术实力和创新能力,提供超越JEDEC标准的超集产品,以获得竞争优势。

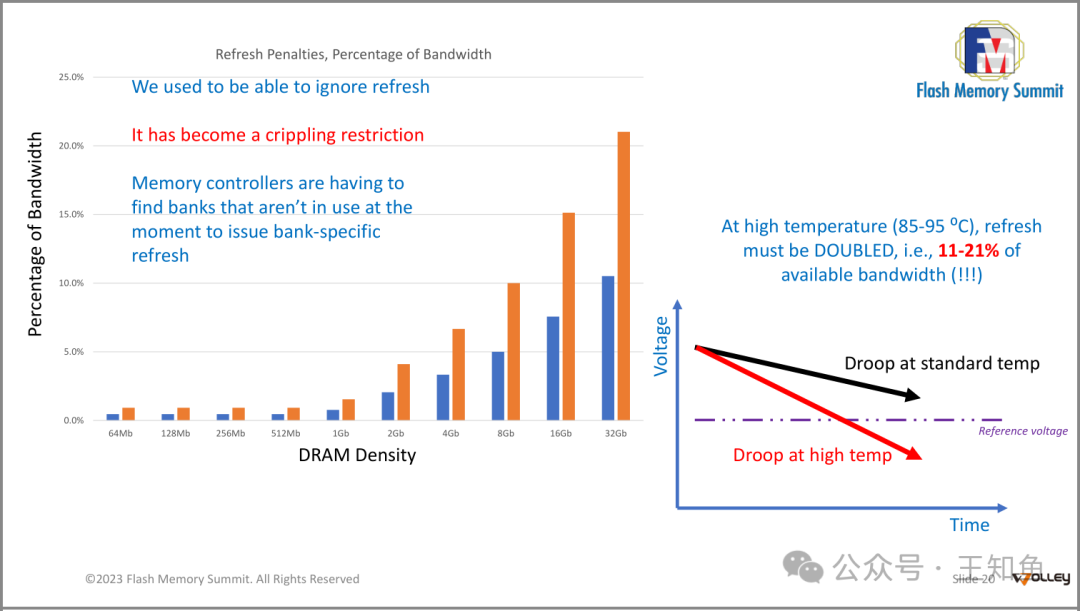

这张图表显示的是随着DRAM密度增加,刷新(refresh)带来的带宽惩罚百分比的变化情况。从图表中可以看出,随着DRAM容量的增长,刷新操作对总带宽的影响越来越大。在早期的小容量DRAM中,我们可以忽略刷新操作,因为它几乎不会影响系统的整体性能。然而,随着DRAM密度的增加,刷新已经变成了一个严重的限制因素,占据了可用带宽的相当一部分比例。

在高密度DRAM中,例如32Gb,刷新操作可能消耗高达21%的可用带宽,这对系统性能产生了显著的影响。此外,当温度升高时(85-95摄氏度),为了维持稳定性,刷新频率必须加倍,这意味着额外的11%-21%的带宽损失,这是一个非常大的性能下降。

图表右侧还有一条时间轴,表示随着时间的推移,电压也会有所下降,这可能是由于老化或者高温导致的。在标准温度下,电压下降(Droop at standard temp)相对于参考电压(Reference voltage)有一定的幅度,而在高温环境下,电压下降更严重(Droop at high temp)。

SOC上的散热设计是个非常重要的问题。

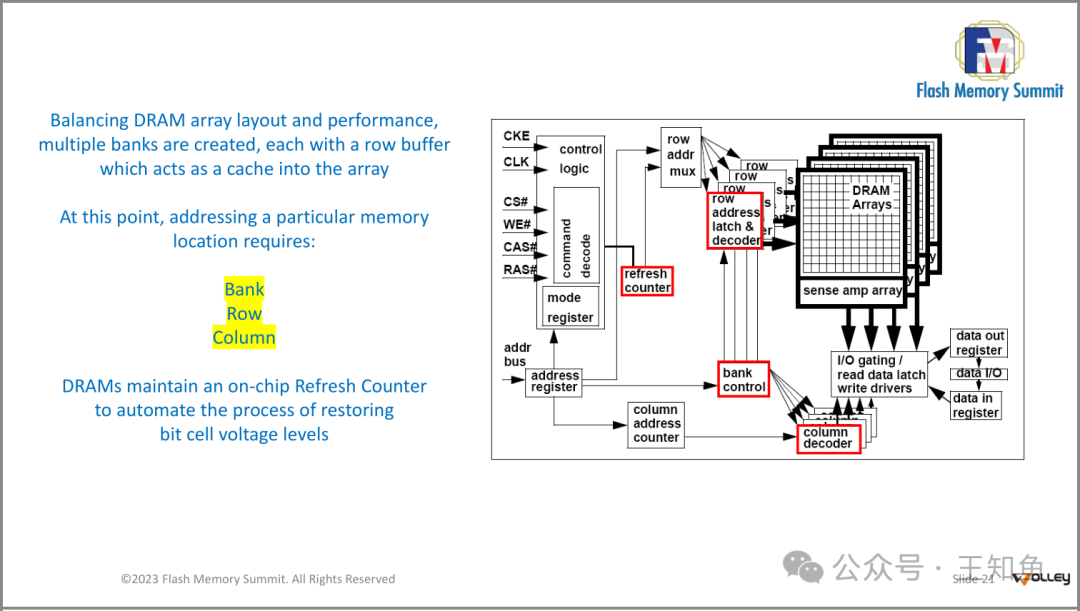

展示了一个DRAM存储器的基本架构,并解释了如何通过创建多个bank来平衡DRAM阵列布局和性能。

每个bank都有一个行缓冲区,可以作为数组的缓存。要访问特定的记忆位置,需要指定Bank、Row和Column三个参数。同时,DRAM维护了一个片上Refresh Counter,用于自动恢复位单元电压水平的过程。

多年来,DRAM的核心架构设计并没有发生显著变化,基于Core驱动器来调度(写入、读取、刷新)器件上上电压位;快速迭代的是链接Host和DRAM器件的I/O驱动器,用时髦的术语来说,软件定义DRAM使得传统器件的访存效率明显改善。

在DRAM存储器快速发展的25年里,有哪些过程优化和改进呢?

DRAM优化策略:DDR1-DDR4

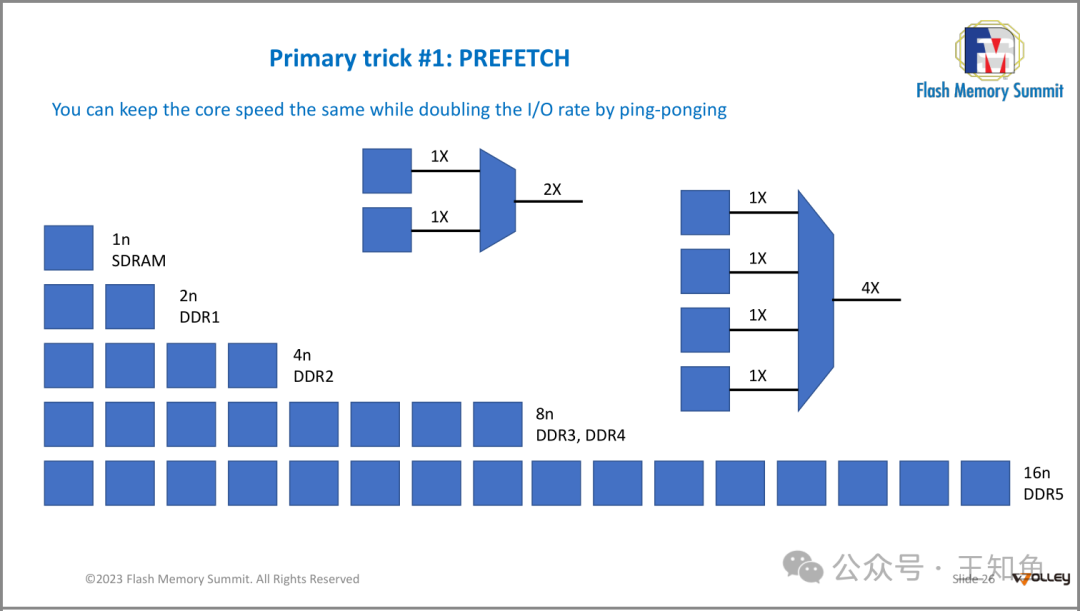

策略一:并行预取(Prefetch)

预取并行度是指一次数据传输过程中,内存控制器可以处理多少组数据。这个数字越大,表示内存系统可以一次性处理的数据量越多,从而提高数据吞吐量。

例如,DDR5的16n预取并行度(内存控制器双通道,8n/通道)意味着它可以一次处理16组数据,而DDR1只能处理一组数据。这种增加预取并行度的方法使得内存系统能够在保持核心速度不变的情况下,通过ping-ponging方式提高I/O速率,从而提高整体系统性能。

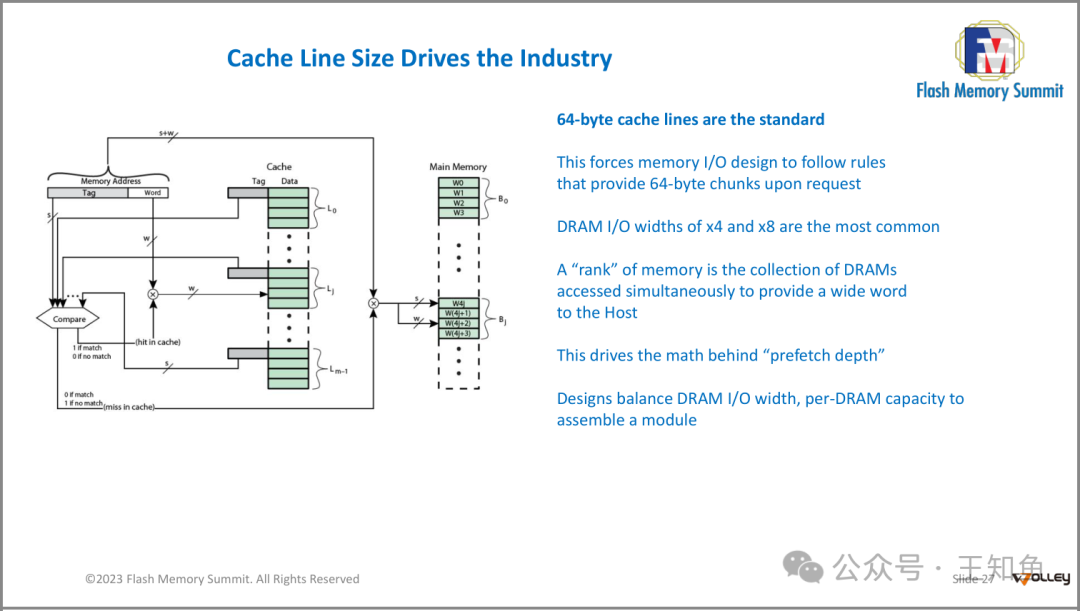

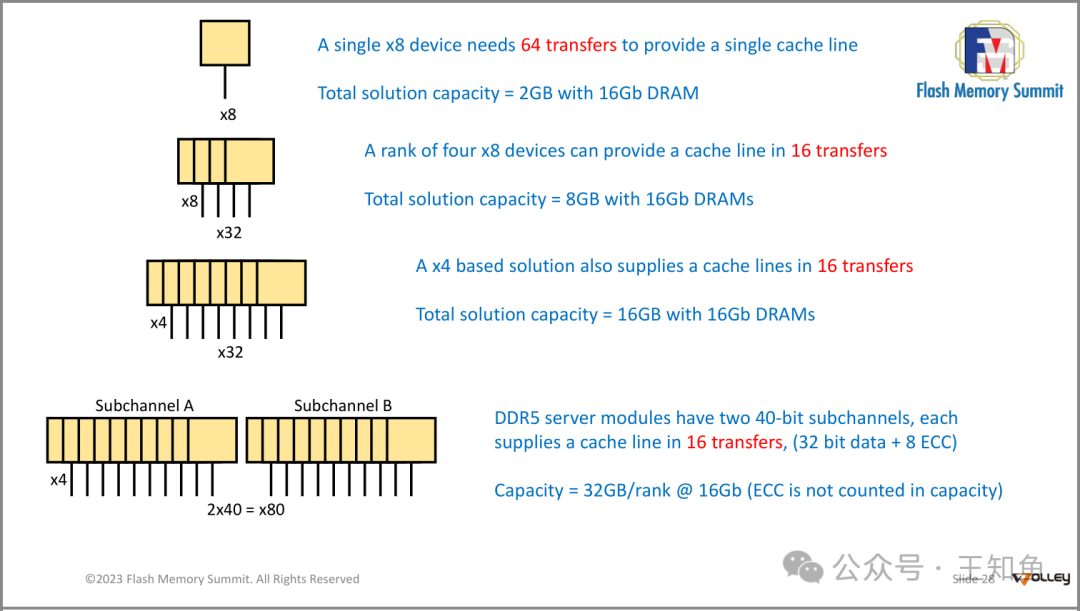

缓存行(Cache Line)大小驱动着整个行业的发展。具体来说:

- • 64字节的缓存行是标准:这是指当前计算机体系结构中的缓存行大小通常是64字节。

- • 这迫使内存I/O设计遵循规则:这些规则要求在请求时提供64字节的数据块。

- • DRAM I/O宽度为x4和x8是最常见的:这是指DRAM接口的宽度通常为4倍或8倍的数据宽度。

- • 一个“rank”指的是同时被访问的一组DRAM芯片:它们一起工作以向主机提供一个宽字。

- • 这推动了预取深度背后的数学原理:预取深度是指一次从内存中读入多少数据到缓存中的策略。

- • 设计师们平衡DRAM I/O宽度和每个DRAM的容量:以此来构建内存模组。

不同数据宽度对应着不同Rank(即内存条上的单个颗粒)大小,展开来看,

- • 64 Byte的缓存行,对应8 bit I/O通道,需要传输64次(1Byte = 8 bit),常见于早期服务器内存条(DDR1);

- • 4并行的8位DRAM I/O,只需要16次传输(相对加速了4倍!);

- • 同样的道理,8并行的4位DRAM I/O,也需要16次传输;

- • DDR5服务器模块有两个40位子通道(明显提升!),每个子通道都能在16次传输内提供一个缓存线,其中包含32位数据和8位ECC(错误校验码,提高Cache命中率)

Prefetch 可以升级到x16或者更高,来优化传输带宽吗?

内存设计确实可以通过提高预取(prefetch)并行度来优化传输效率,但这并非没有限制。在考虑是否可以设计出更高并行度如x16的设备时,我们需要考虑几个关键因素:

- 1. 信号完整性:随着数据线数量的增加,信号完整性和电气特性变得更加复杂,这可能导致信号反射、串扰和时序问题,进而影响数据的可靠性和速度。

- 2. 功耗:更多的数据线意味着更高的功耗,这对于便携式设备和服务器的热管理是不利的。

- 3. 成本和封装尺寸:更多的数据线意味着更大的封装尺寸,这不仅增加了成本,也可能限制了在有限空间内的使用。

- 4. 芯片设计复杂性:更高的并行度要求更复杂的芯片设计,包括更多的I/O控制器和更复杂的内存控制器,这会增加设计难度和成本。

- 5. 效率和带宽:虽然理论上x16设备可能提供更高的带宽,但实际上,由于信号质量和功耗的限制,实际的带宽增益可能不如预期显著。例如,两个x8设备可能比一个x16设备在实际应用中更加高效。

- 6. 标准化和兼容性:内存标准如DDR是由JEDEC这样的组织制定的,它们平衡了上述所有因素来确定最佳的并行度。偏离这些标准可能会导致兼容性问题。

因此,尽管理论上可以设计x16设备,但在实践中,考虑到上述限制,业界通常会选择更优化的方案,如增加通道数(比如DDR5中的两个独立的40位子通道),使用更先进的工艺节点来降低功耗和提高速度,或是采用其他类型的内存技术(如HBM,高带宽内存)来达到更高的带宽和效率,而不只是单纯增加单个设备的数据线数量。

策略二:通信系统优化(DDR1--DDR4)

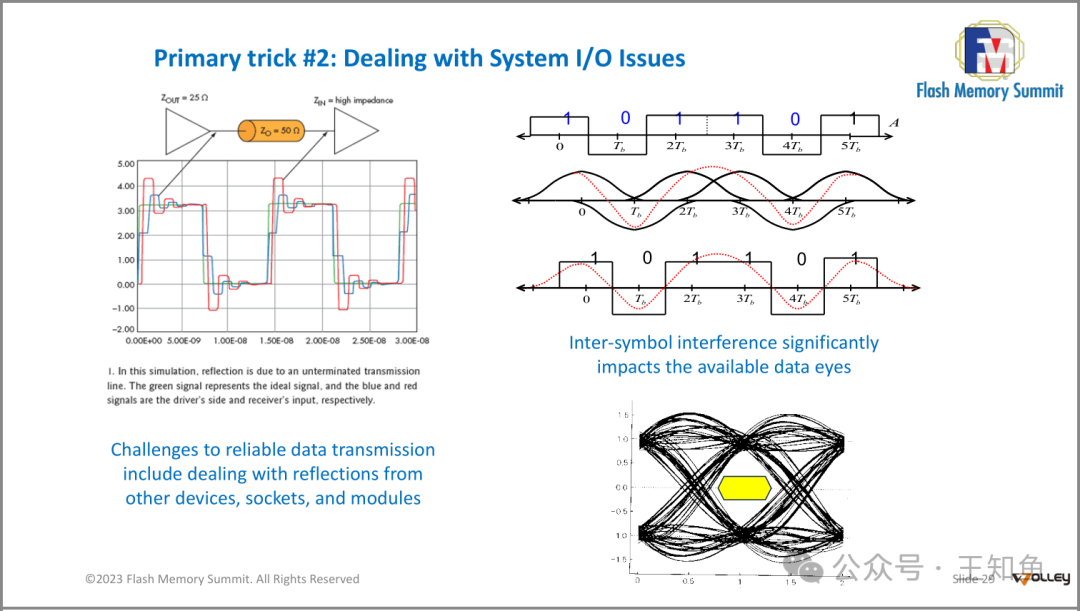

相对于并行预取策略的高效,如何优化DRAM io 和系统 io 间的模型信号的相干性,是更底层的优化策略。

图中显示了信号反射对可靠数据传输的挑战,特别是在系统输入输出(I/O)方面。

图中左侧是一个模拟电路图,显示了信号反射的情况,右侧则是实际测量得到的眼图。眼图是一种用来评估数字通信系统中信号质量的方法,它可以帮助我们理解信号在经过长距离传输后受到噪声干扰的程度。图中可以看到,由于反射导致的符号间干扰(Inter-symbol interference, ISI)显著影响了可用的数据窗口(data eyes),这会降低系统的传输速率和可靠性。因此,解决这种问题成为了设计高速通信系统的一个重要技巧。

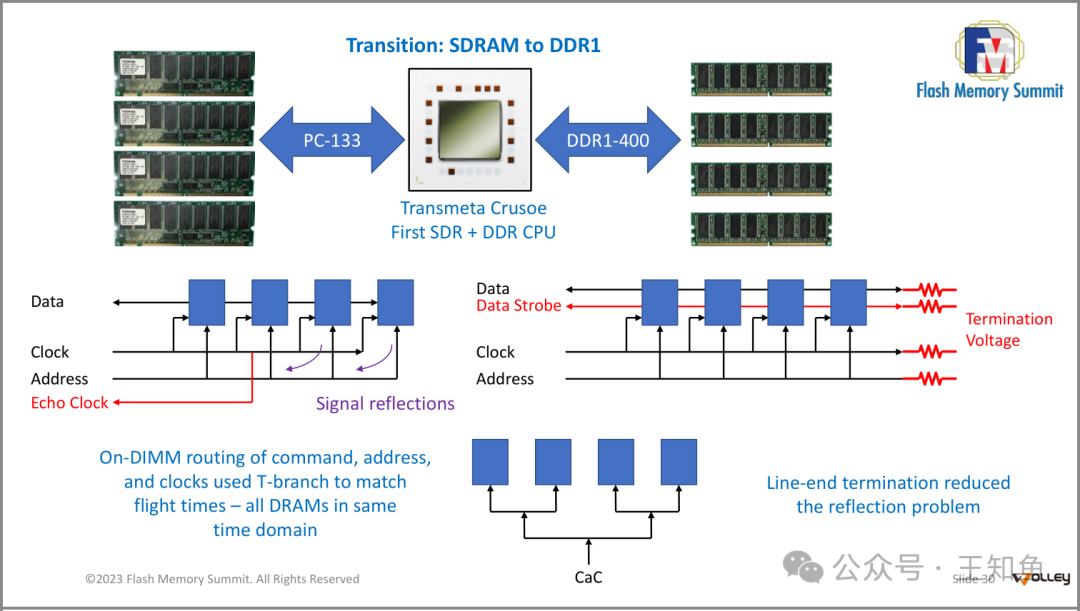

SDRAM--DDR1

SDRAM到DDR1的过渡过程,Transmeta Crusoe处理器作为第一个支持这两种类型的CPU。

SDRAM(Synchronous Dynamic Random Access Memory)是一种同步动态随机存取存储器,它是DRAM(Dynamic Random Access Memory)的一种类型,但与传统的异步DRAM相比,它能够与系统时钟同步运行,从而提供更高的数据传输率和更佳的性能。SDRAM的设计目的是为了适应计算机系统中日益增长的性能需求,尤其是在处理器速度快速提升的背景下,传统的异步DRAM无法提供足够的带宽和响应速度。

图中左边是PC-133 SDRAM的架构,右边是DDR1-400的架构。中间有一个小插图展示了一个Transmeta Crusoe CPU。在SDRAM中,数据、地址和时钟信号都是分开的,而在DDR1中,数据和数据 strobe是结合在一起的,而且还有终结电压(Termination Voltage)和寄生电容(CaC)。此外,DDR1还采用了线路末端终止(Line-end termination)技术来减少反射问题。

通过 数据 strobe、终结电压(Termination Voltage)、寄生电容(CaC)和线路末端终止(Line-end termination)技术 来优化SDRAM的信号质量。

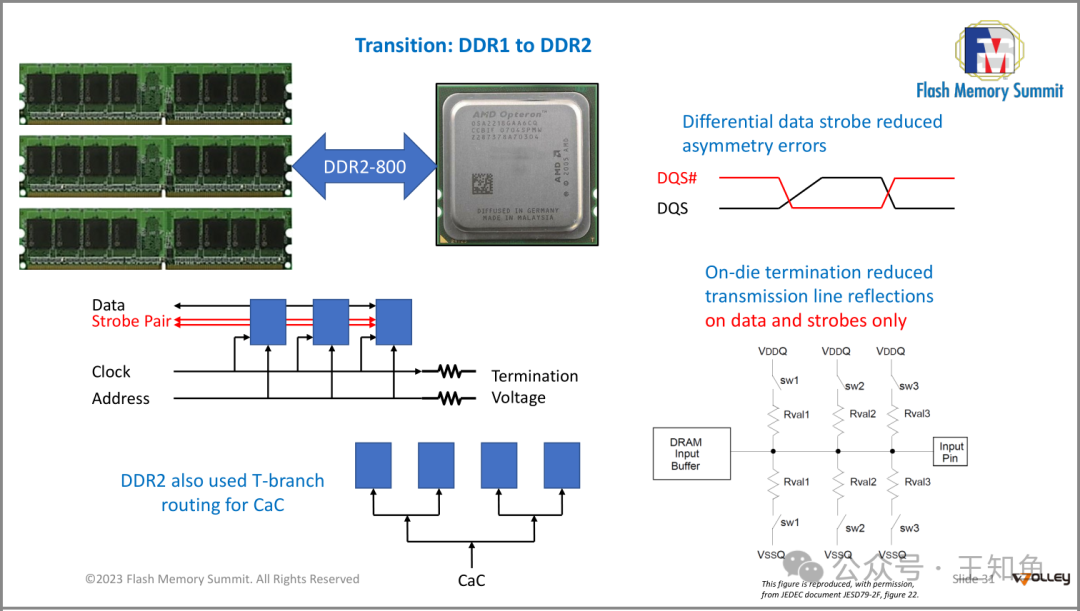

DDR1--DDR2

Strobe Pair 是 DDR2 中的一种设计特性,用于减少不对称性错误。它由两个互补的信号 DQS 和 DQS# 组成,它们是差分信号,可以提高信号质量和稳定性。这个设计有助于改善数据传输的准确性和效率,并且在数据和脉冲线上使用了片上终接(On-die termination) 来减少传输线的反射。此外,DDR2也继续使用了T分支路由来进行寄生电容补偿(CaC)。

图中还包含了一个详细的内部缓冲器示意图,说明了如何通过开关(sw1、sw2、sw3)来控制终端电阻(Rival1、Rival2、Rival3),从而实现片上终接。

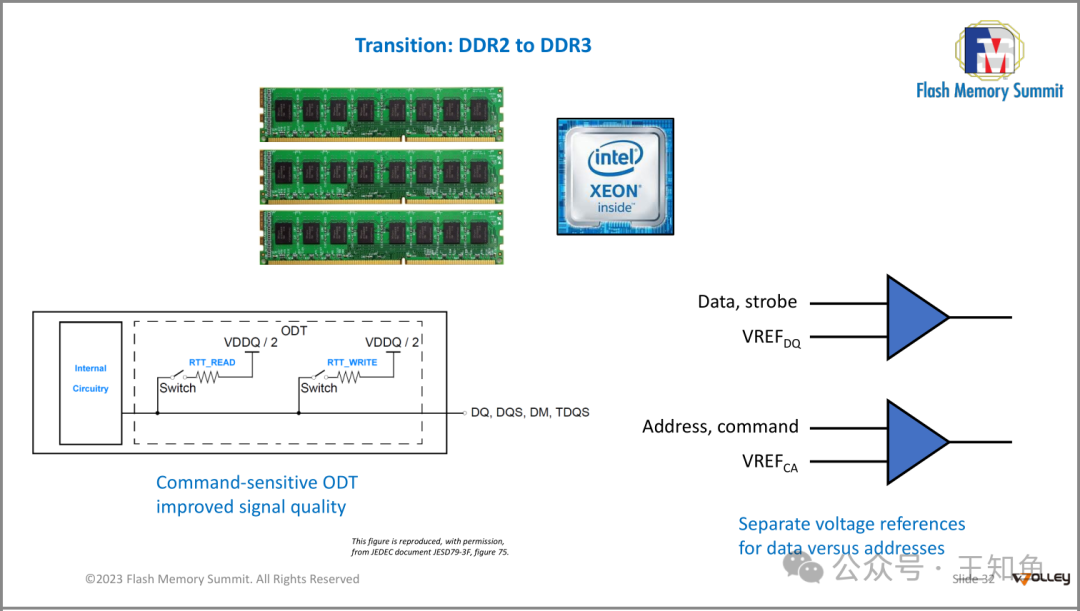

DDR2--DDR3

DDR3引入了命令敏感的ODT(Command-sensitive ODT),提高了信号质量,并且为数据和地址使用了不同的电压参考(Separate voltage references for data versus addresses)。

图中还包括一个内部电路图,显示了VREF_DQ和VREF_CA是如何连接到数据和地址/命令线上的。

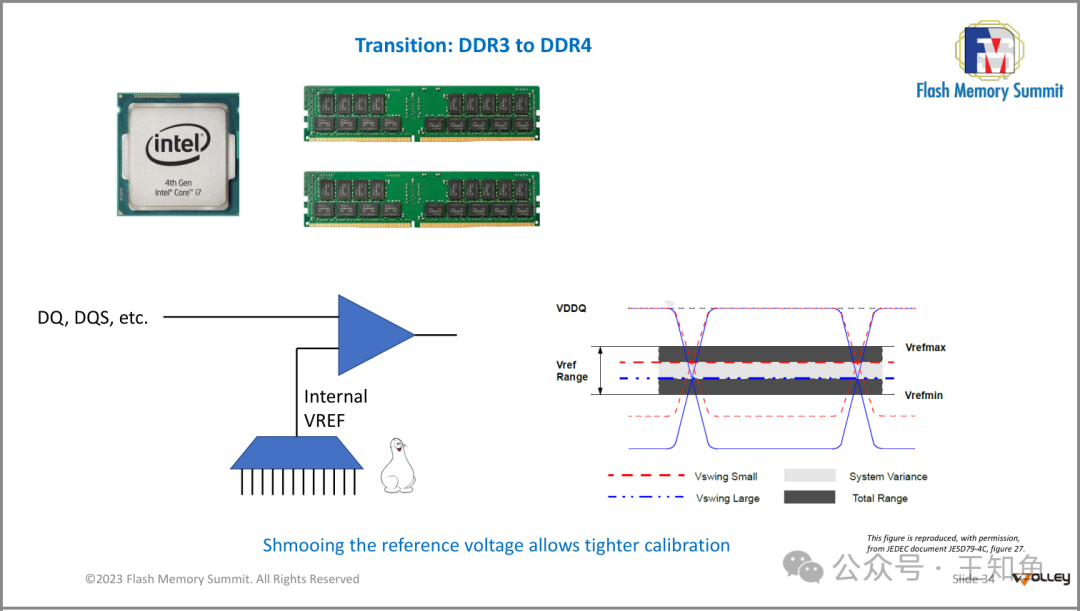

DDR3--DDR4

DDR4引入了更精细的参考电压调整(Shmooing the reference voltage allows tighter calibration),并且图中包括了一个内部电路图,显示了VREF是如何连接到数据线上的。

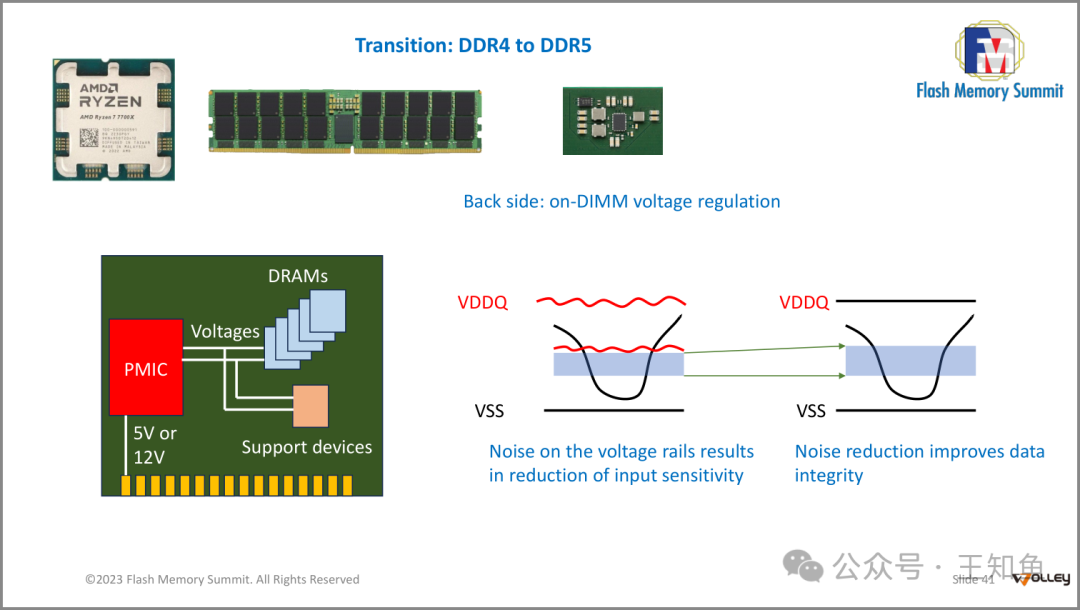

DDR5

DDR5 是当前DRAM行业成熟工艺制程的最新产品,与DDR4 相比:

DDR5引入了DIMM上的电压调节(Back side: on-DIMM voltage regulation),以减少电源轨上的噪声(Noise reduction improves data integrity),从而提高输入灵敏度(Noise on the voltage rails results in reduction of input sensitivity)。图中还包含了一个内部电路图,显示了PMIC如何连接到电压轨上。

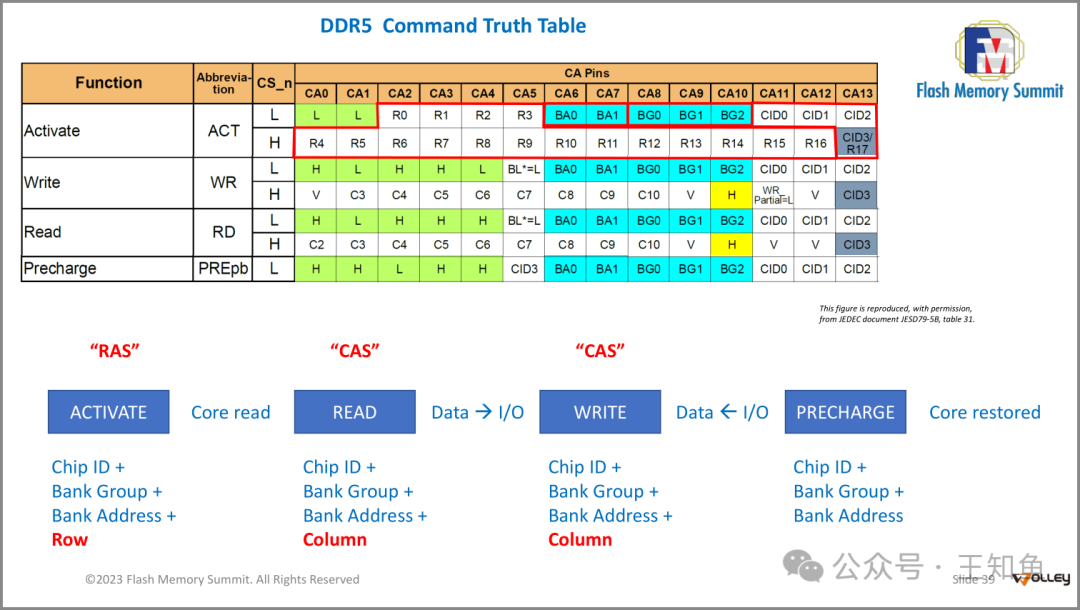

图示DDR5命令真值表(Command Truth Table),它详细说明了不同命令(Activate, Write, Read, Precharge)对应的引脚状态(CS_n, CA pins等)。

表格分为四部分,“RAS”、“CAS”、“CAS”和“CAS”,分别对应ACTIVATE、READ、WRITE和PRECHARGE四个动作及其所需的信号组合。例如,激活(ACTIVATE)需要Chip ID、Bank Group、Bank Address和Row信息;读取(READ)需要Chip ID、Bank Group、Bank Address和Column信息;写入(WRITE)也需要同样的信息;最后,预充电(PRECHARGE)只需要Chip ID、Bank Group和Bank Address信息。

表格对于理解DDR5内存的工作原理非常有帮助,因为它描述了控制器如何通过特定的引脚状态向内存模块发送各种命令。

内存控制器(Memory Controller)和命令真值表有什么关系呢?

内存控制器(Memory Controller)是负责管理与内存交互的硬件组件,它位于CPU或北桥芯片中,在现代系统中通常集成在CPU内部。内存控制器的任务包括但不限于接收来自CPU的数据读写请求,将这些请求转换为适合内存模块的操作命令,管理内存寻址,控制内存的刷新周期,以及处理数据的传输。

内存控制器与命令真值表之间的关系体现在以下几个方面:

- 1. 命令生成:当CPU发出读写请求时,内存控制器根据请求的类型生成相应的内存命令。这些命令需要按照命令真值表的规定,设置正确的控制引脚状态,以确保正确的命令被发送到内存模块。

- 2. 时序控制:内存控制器还必须遵守命令真值表中规定的时序要求,例如,在发送读或写命令之前,可能需要先发送激活(Activate)命令打开正确的行,然后在适当的时间间隔后发送读或写命令。内存控制器需要确保这些命令按正确的顺序和时间间隔发送。

- 3. 错误检测与纠正:内存控制器还可能包含错误检测和纠正机制,这在一定程度上依赖于命令真值表来确定哪些命令序列是合法的,哪些可能是错误的。

- 4. 刷新管理:命令真值表也会列出刷新(Refresh)命令的触发条件,内存控制器需要定期执行刷新操作,以维持动态RAM中的数据不丢失。

简而言之,内存控制器基于命令真值表来正确地生成和发送内存命令,以保证内存的正常读写操作和其他功能的正确执行,可以把真值表理解成计算体系的指令集,而MC则是负责翻译和执行指令集的计算单元。

DDR5 新特性

伴随系统通信信号的底层优化,最新一代DDR5在功能上通过软硬结合定义出多种新特性,以下逐一介绍。

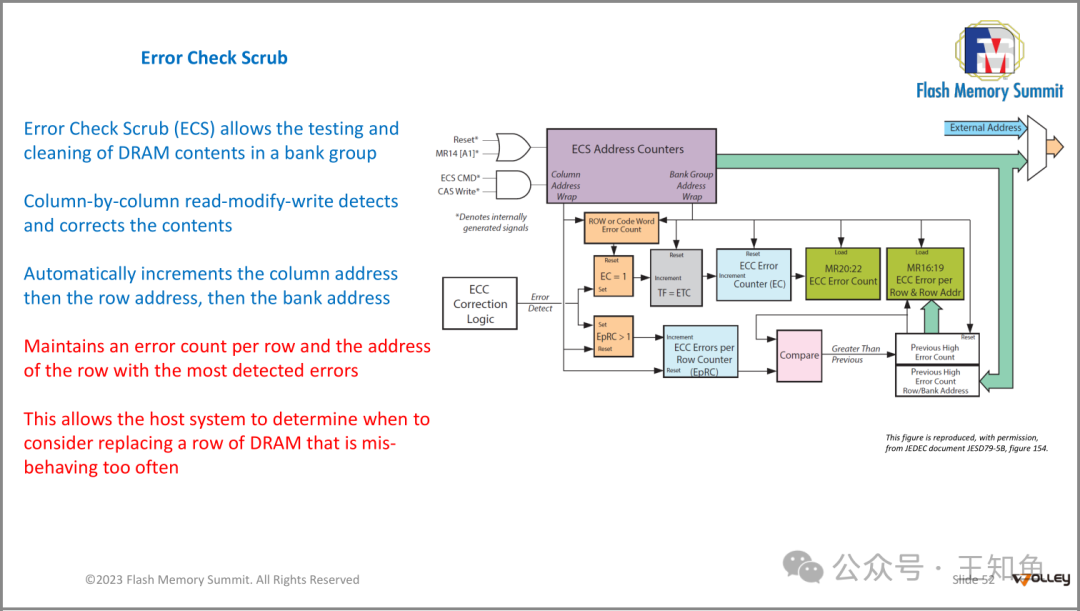

Error Check Scrub (ECS)

Error Check Scrub (ECS),允许测试和清理Bank组中DRAM内容。通过列读修改写操作检测和纠正内容,并自动递增列地址,然后行地址,再然后Bank地址。此外,它还会维护每行的错误计数和错误最多的行的地址,以便主机系统可以决定何时替换行为异常的DRAM行。

Error Check Scrub (ECS)主要用于以下场景:

- 1. 故障排除和诊断:当系统遇到内存相关的问题时,ECS可以帮助定位问题的具体位置,比如哪一行DRAM出现了过多的错误。这对于故障排除和诊断非常重要,因为它能提供有关内存健康状况的详细信息。

- 2. 长期稳定性监控:在服务器和数据中心环境中,ECS可用于监控内存的长期稳定性。如果某一行DRAM频繁出错,那么系统可以根据ECS提供的信息决定是否需要更换该行,以避免潜在的数据损坏或系统崩溃。

- 3. 内存校验:在某些安全关键的应用程序中,ECS可以作为额外的安全层,确保内存内容的准确性。例如,在金融交易或医疗设备中,任何内存错误都可能导致严重后果,因此这种自我检查和修复功能至关重要。

- 4. 实验研究:研究人员可能会使用ECS来分析内存错误模式,了解其原因,或者评估不同内存配置下的错误率。

- 5. 内存测试:在生产过程中,制造商可以使用ECS来测试新生产的内存模块的质量,确保其符合规格。

- 6. 老化管理:随着内存使用时间的增长,一些位可能会逐渐变得不稳定。ECS有助于发现这些问题并在它们导致严重问题之前采取措施。

- 7. 故障预防:在高可用性系统中,ECS可以帮助预防因内存错误而导致的服务中断,通过提前识别和替换有问题的内存行。

Memory Built In Self Test (MBIST)

Memory Built-In Self Test (MBIST) 是一种内置自测技术,它允许DDR5设备在接收到主机指令时进行内部自检。以下是MBIST的工作原理和实际应用场景:

工作原理:

- 1. 启动测试:当主机命令DDR5设备运行MBIST时,设备开始执行一系列预先编程的测试。

- 2. 测试过程:MBIST会生成并注入特定的测试模式到内存阵列,然后读回结果并与预期的结果进行比较。如果有任何差异,则表示可能存在错误。

- 3. 报告结果:完成测试后,设备将结果存储在一个称为模式寄存器(Mode Register,MR)的位置,通常是MR22。主机可以通过查询这个寄存器来获取测试结果。

- 4. 决策制定:如果测试结果显示存在未修复的错误,主机可以决定是否需要进一步的修复步骤,如Post Package Repair (PPR)。

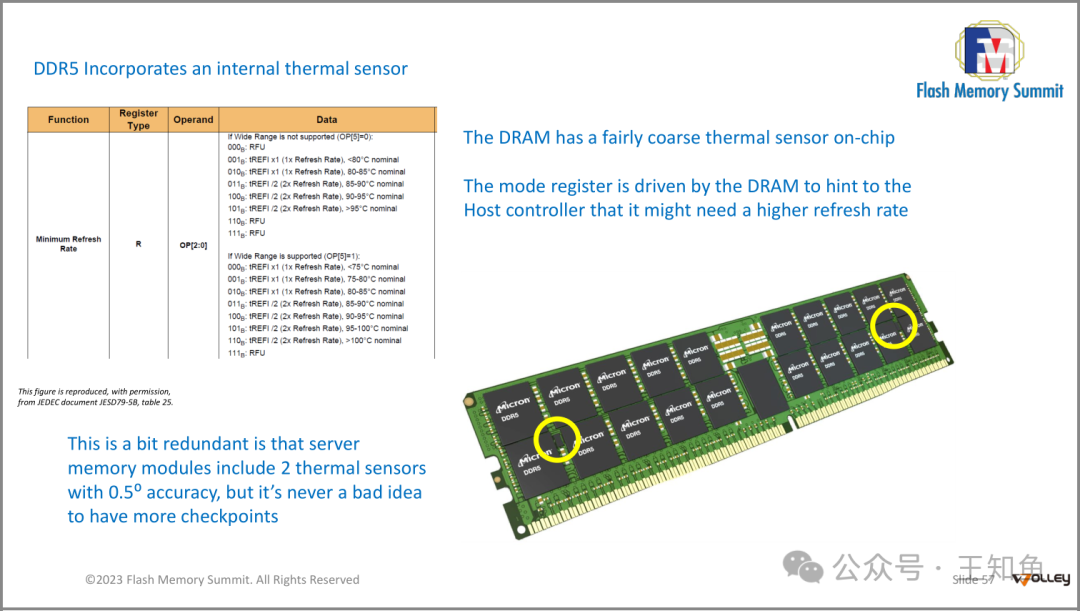

Internal Thermal Sensor

DDR5内存模块具有一个内置的热传感器,该传感器能够感知温度并将其反馈给主控。

当温度超过一定阈值时,如温度在85℃以下,保持单次刷新频率,超过则2倍刷新频率(Wide Range 功能支持更细粒度的温度控制),内存模块会向主控提示需要增加刷新速率以保持数据的稳定性。虽然服务器内存模块通常已经包含了两个精度为0.5度的热传感器,但多一层保障总是好的。

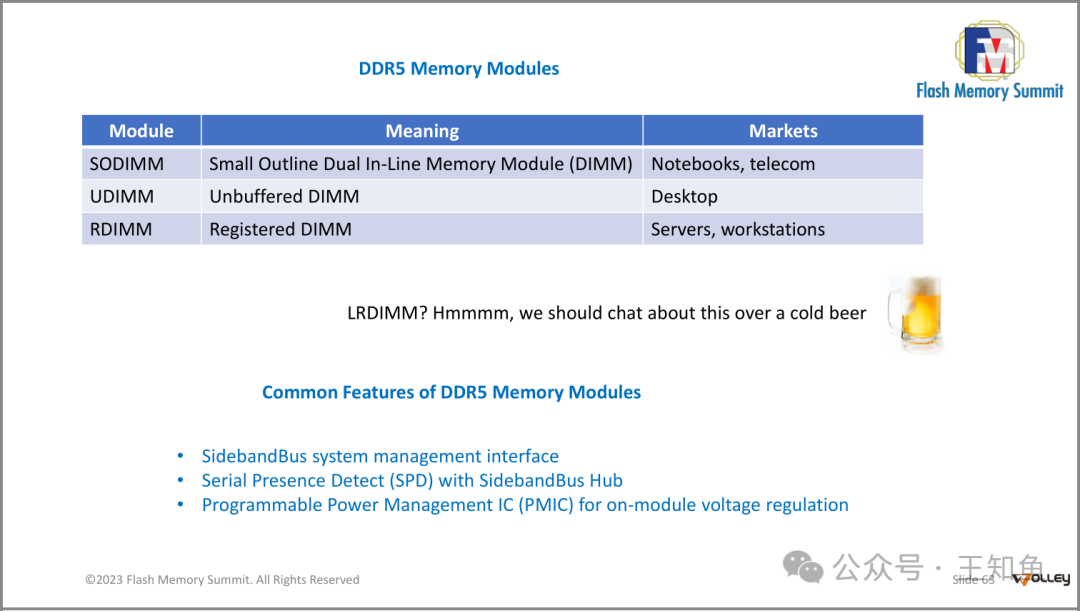

DDR5 模组

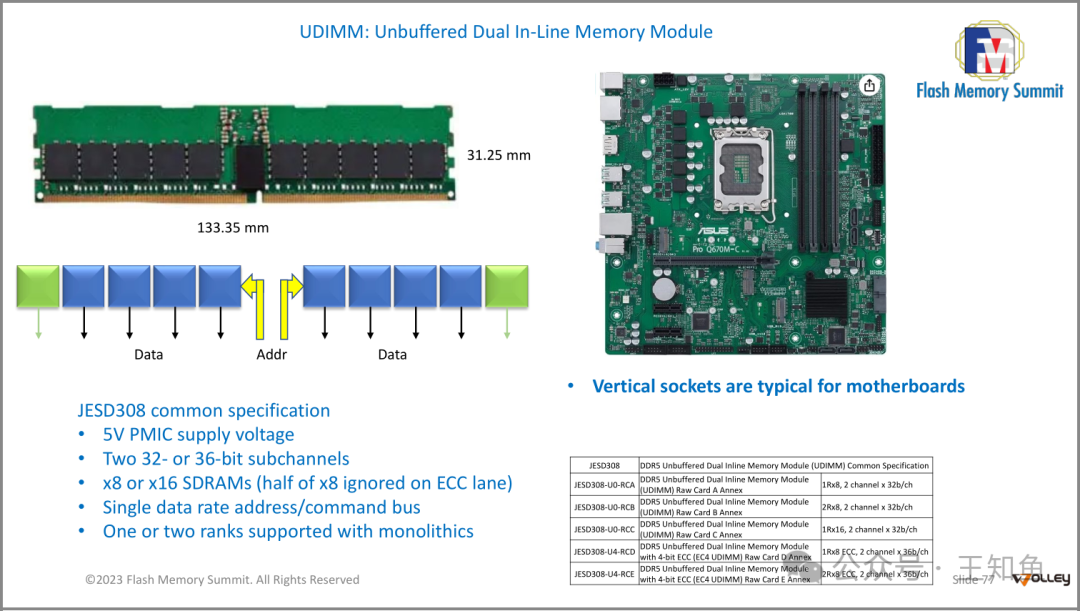

DDR5内存模块的不同类型对应不同市场,包括:

- • SODIMM:Small Outline Dual In-Line Memory Module,用于笔记本电脑和电信领域;

- • UDIMM:Unbuffered DIMM,用于台式机;

- • RDIMM:Registered DIMM,用于服务器和工作站。

DDR5内存模块的共同特征,包括:

- • SidebandBus系统管理接口;

- • Serial Presence Detect (SPD) with SidebandBus Hub;

- • Programmable Power Management IC (PMIC) for on-module voltage regulation。

这些特性使得DDR5内存模块更加高效、可管理并且具备更好的电源管理能力。

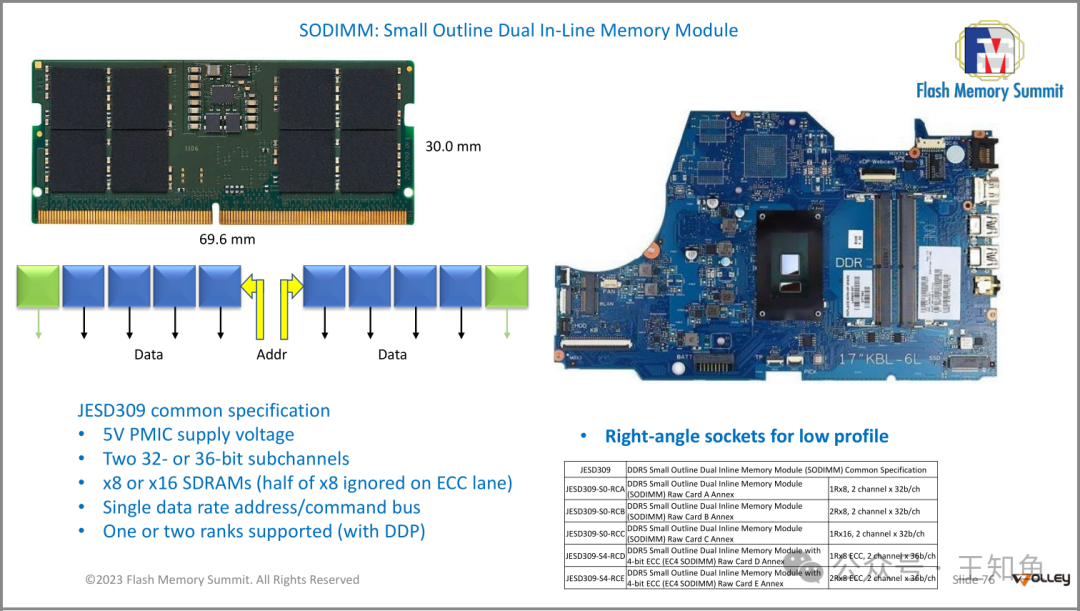

SODIMM-小型双列直插内存模块

SODIMM的一般特性:

- • JESD309通用规范

- • 5V PMIC供电电压

- • 两个32或36位子通道

- • x8或x16 SDRAMs(ECC x8被忽略)

- • 单一的数据/命令总线速度

- • 支持一或两行(使用DDP)

UDIMM

与SODIMM基本保持一致。

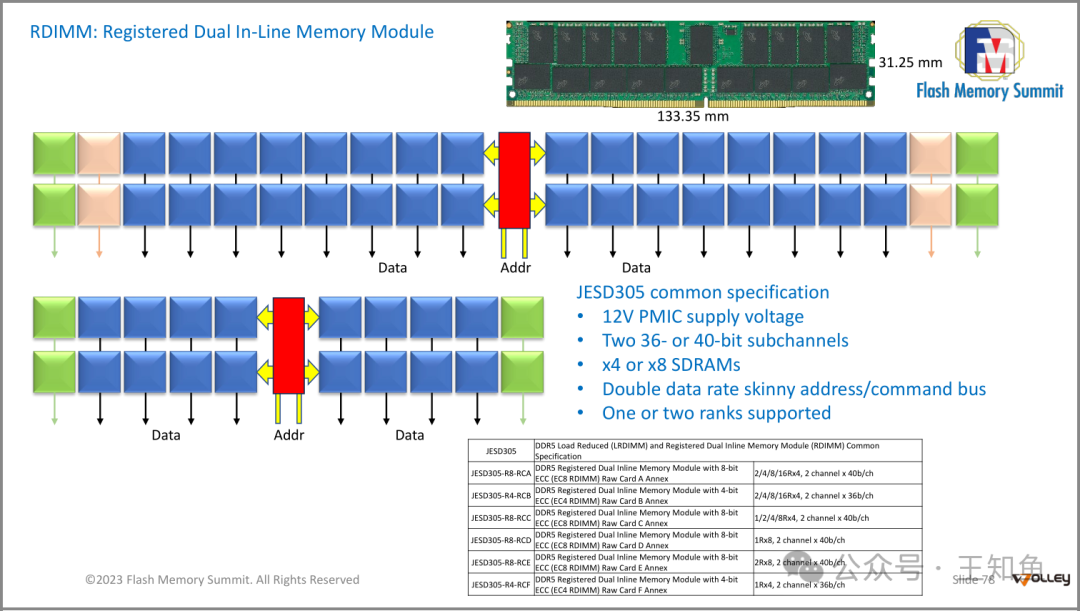

RDIMM-双列直插内存模块

应用于工作站和服务器的DIMM外观与应用于台式机的UDIMM 大致相同,主要差异点在:

- 1. 工作电压从5V升级到12V;

- 2. 基于ECC机制,位宽较前两者要高一点;

- 3. 接口宽度较SODIMM 和 UDIMM 的宽度下降,保留 x4 和 x8(为什么会下降?大概率还是服务器场景的功耗考虑)

- 4. 支持双路寻址

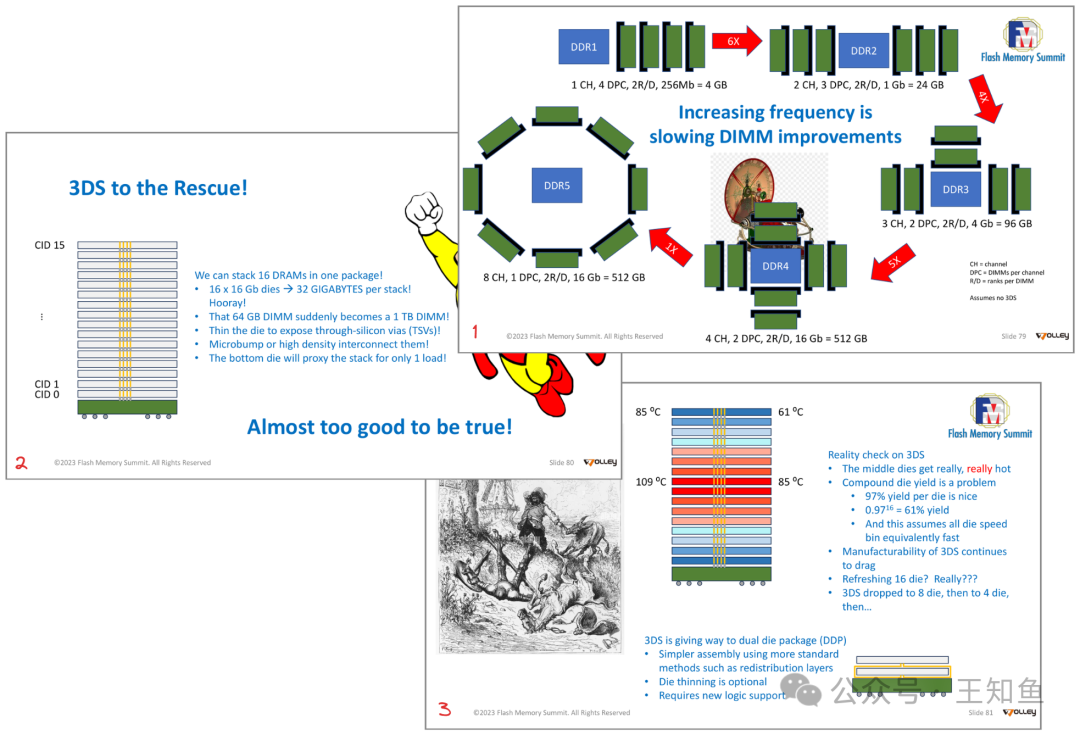

DRAM的未来与CXL

DRAM 容量焦虑与现实

- 1. 长期关注于提高DIMM 带宽,使得对DIMM物理结构上的优化停滞不前,而应用场景(如AI、自动驾驶)对DRAM的容量需求一直在上涨;

- 2. 业界提出3DS的制造工艺,通过不断堆叠DRAM层数来实现容量的线性增加;

- 3. 随着DRAM 层数的增加,又将出现新问题:

- • 堆叠器件的中间位置将成为高温灾区,因温度造成的频繁刷新,将严重影响DRAM的可用带宽(每次刷新消耗近21%的理论带宽);

- • 器件的量产率不可控,当前单层良产率能达到97%,看似不错,可一旦按16层堆叠,仅有61%的良产率;

- • 3DS的工艺和产能尚不成熟,无法满足产业需求。

考虑到以上因素,目前3DS的生产工艺,停留在2层堆叠,即DDP(Dual Die Package ),先进厂商提出4D-NAND概念[1]。

坐以待毙是下策

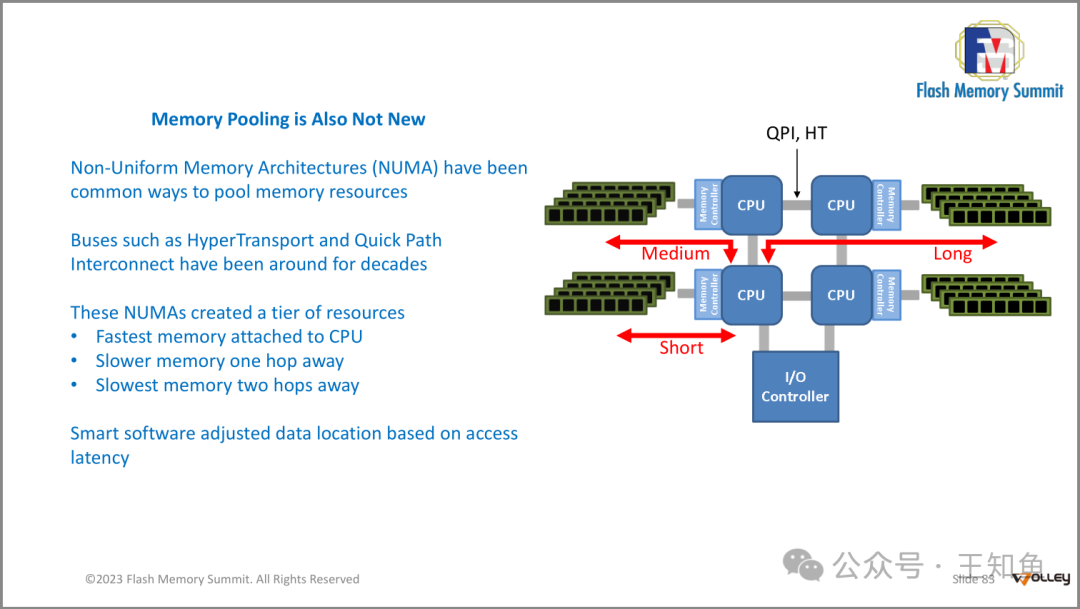

内存池化早在 ARM 多核领域就有过考虑,最早是科学计算场景需求,现在是AI/ML领域,从大科学仪器下沉到企业。

非一致性内存访问(NUMA)一直是池化内存资源的常用方法,

HyperTransport和Quick Path互连等总线已经存在了几十年,

NUMA架构创建了一个资源层次结构 :

- • 离CPU最近的内存访问速度最快 ;

- • 稍远距离的内存,访问速率下降;

- • 访问距离最远的内存,速度相应最慢。

业界已经出现根据访问延迟调整数据位置的智能软件。

现实中NUMA似乎是多核场景(ARM)策略,在Intel主导的服务器市场,并没有多少实际投入和实践。

DRAM的”困境“

- • 每个通道只能安装一个DIMM(Dual In-line Memory Module,内存条)。限制内存扩展的能力,因为在多通道系统中,如果每个通道只能安装一个DIMM,那么内存总量的增长就会受限。

- • DRAM(动态随机存取存储器)在达到32Gb(十进制的32吉比特,相当于4GB)时会遇到瓶颈(此处应该是指单个颗粒的容量)。这可能意味着当前的技术限制使得内存容量难以进一步扩大。

- • 人工智能(AI)的发展需要更大的内存容量。由于AI算法和模型的复杂性,它们往往需要大量的内存来运行,所以内存容量的限制可能会阻碍AI的应用发展。

CXL

- • CXL允许几乎无限的内存扩展。通过CXL连接的内存可以突破传统内存插槽限制,实现更大规模内存扩展。

- • 内存池化功能允许未使用的内存被重新分配。通过CXL连接的内存可以组成一个共享的内存池,让系统能够灵活地管理内存资源,将未充分利用的内存重新分配给需要更多内存的任务,提高资源利用率。

明日之星:CXL ?

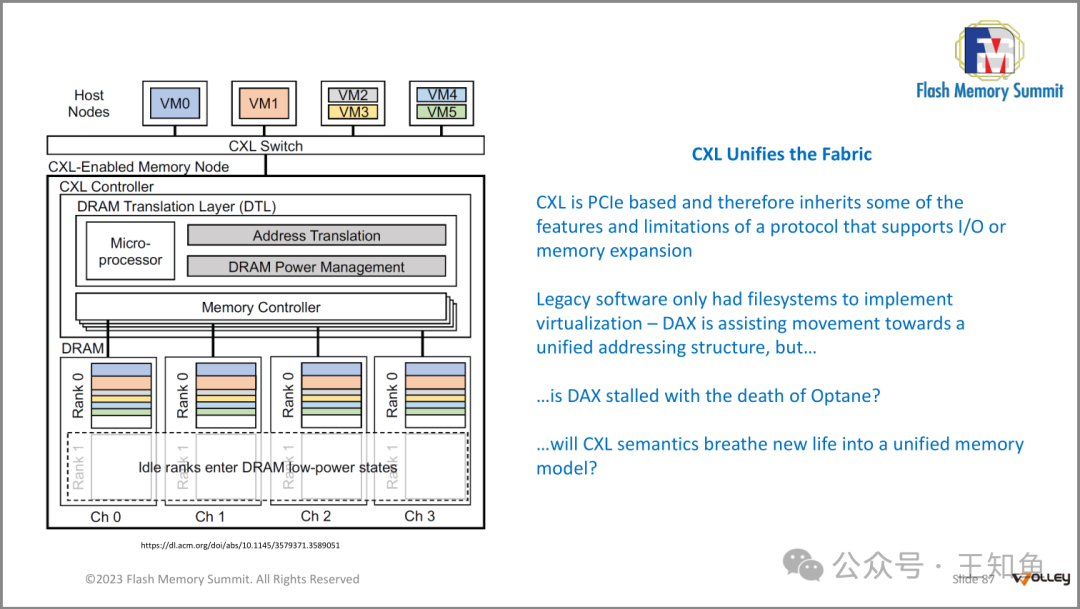

左图是对CXL技术实现的完整架构,核心是基于CXL协议的DRAM控制器(CXL Controller),通过CXL 交换机连接到Host 节点从而实现内存池化后的资源共享,DTL核心组件及工作原理,另文详解。

值得关注的是,Bill 并未一股脑肯定CXL未来统治地位,而是追忆起傲腾往事,并直接表露DAX(Direct Access)是否因为Optane技术的消亡而停滞不前。

或许市场就是如此残酷,Intel这次押宝CXL在逻辑芯片市场再创辉煌了。

随着CXL作为扩展PCIe的统一接口,加入数据存储大家庭,热数据场景除了直接访问(DAS)的DRAM和”不怎么争气“的NUMA[2] ,基于CXL扩展的DRAM内存池将作为最大活跃数据缓存池,从而为企业市场的AI/ML及自动驾驶的IT可行性奠定基础。

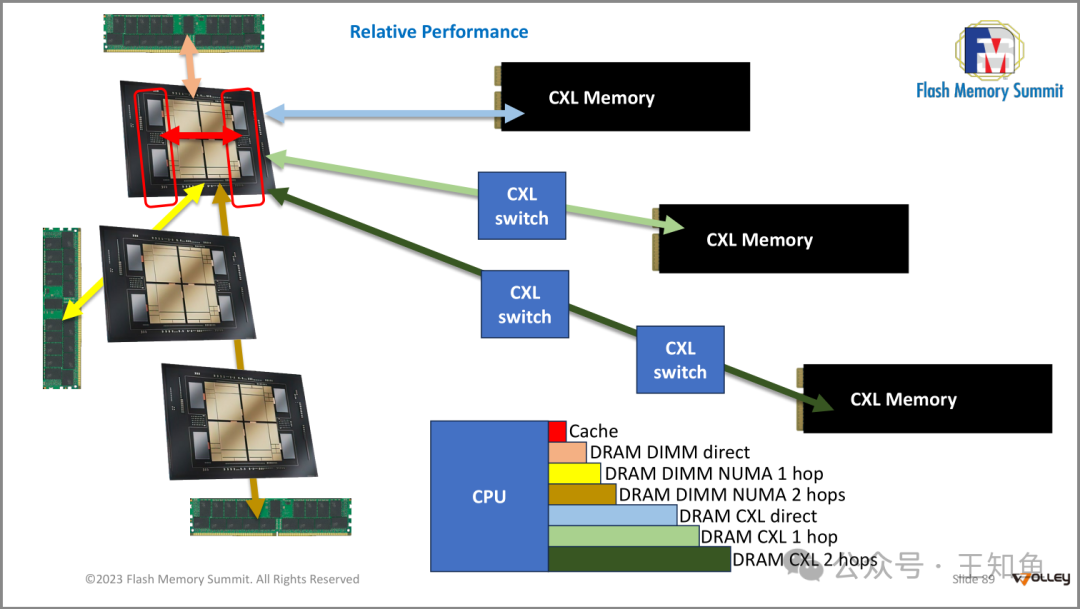

图中说明了三种CXL访存方式:

- 1. CXL Memory 直接通过PCIe口连接到母版,此法效率一等,称之为 DRAM CXL direct;

- 2. CXL Memory 通过一层 CXL交换机连接到PCIe 口,此法效率二等,称之为 DRAM CXL 1 hop;

- 3. 诸如此类,经过2次CXL交换机连接的,效率三等,DRAM CXL 2 hops,但容量却可以做到最大。

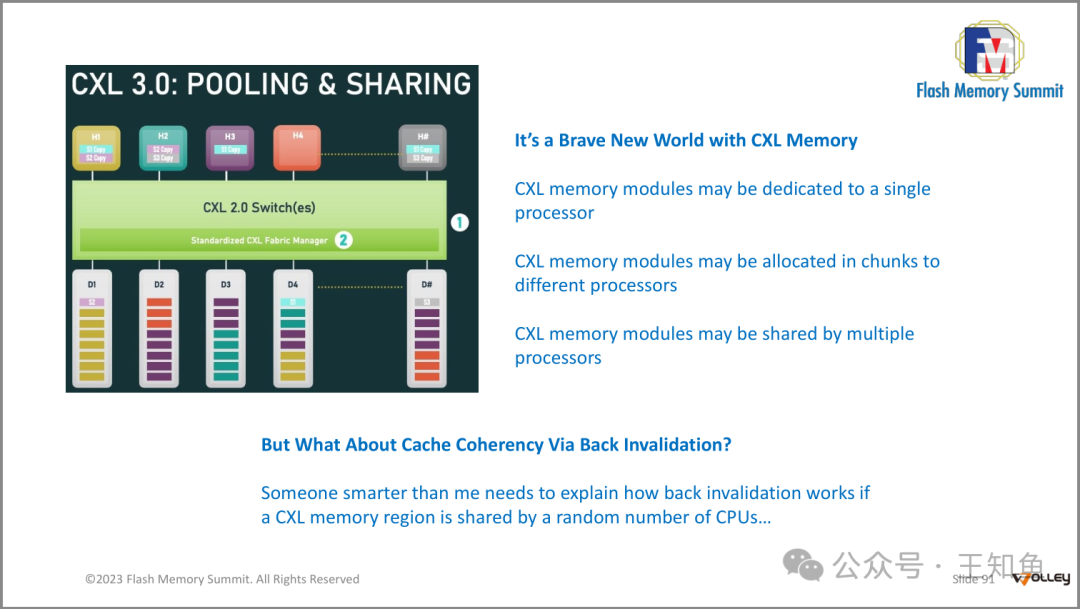

来畅想下CXL 实现后的内存访问方式,CXL内存模块可以有三种分配方式:

- • 可以专属于一个处理器;

- • 可以分块给不同的处理器使用;

- • 指定Moudle可被多个处理器同时共享(有点VMware中VMFS的感觉)。

存在的问题是:当同一内存区域被多个处理器共享写入时,缓存一致性的反向失效是如何工作的?

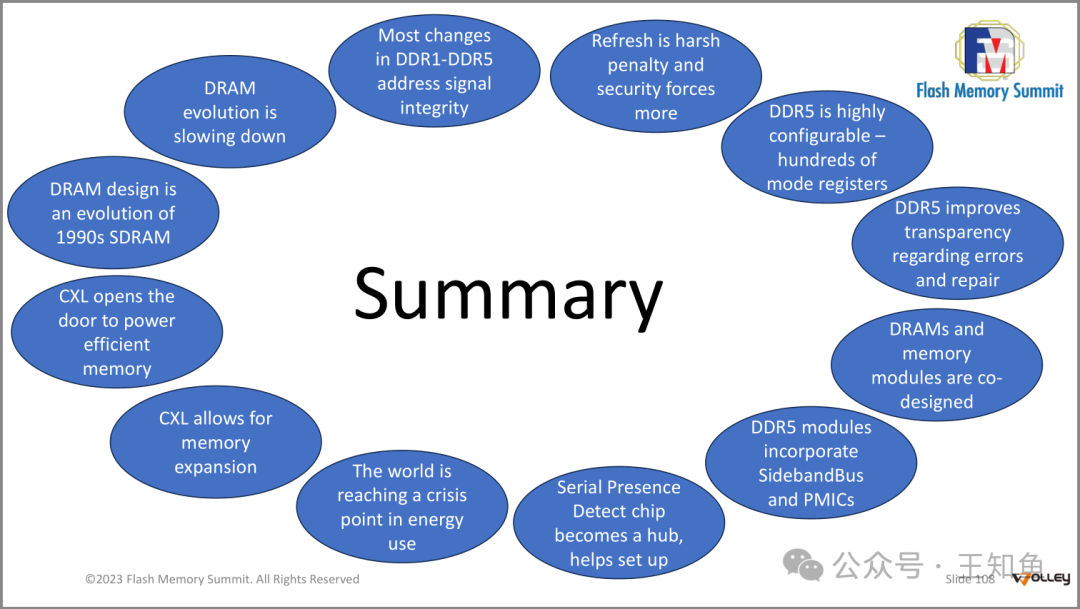

总结

- • DRAM的设计源自于1990年代SDRAM技术

- • DRAM的发展正在逐渐放缓

- • UDDR5具有高度可配置性——拥有数百个模式寄存器

- • DDR5提高了关于错误和修复的透明度

- • DRAM和内存模块协同设计

- • DDR5模块集成了侧带总线(SidebandBus)和电源管理集成电路(PMICs)

- • DDR1至DDR5的大多数变化集中在提高信号完整性

- • 刷新操作带来严重的性能损失,而安全要求进一步加剧了这一问题

- • CXL技术允许进行内存扩展

- • CXL技术为高效能、低功耗内存打开了大门

引用链接

[1] 4D-NAND概念: https://www.dramx.com/News/Memory/20240808-36833.html

[2] ”不怎么争气“的NUMA: https://frankdenneman.nl/2022/09/21/sub-numa-clustering/

---【本文完】---

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-08-30,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录